Xilinx Virtex-5 FPGA CLB资源学习笔记

FPGA CLB介绍

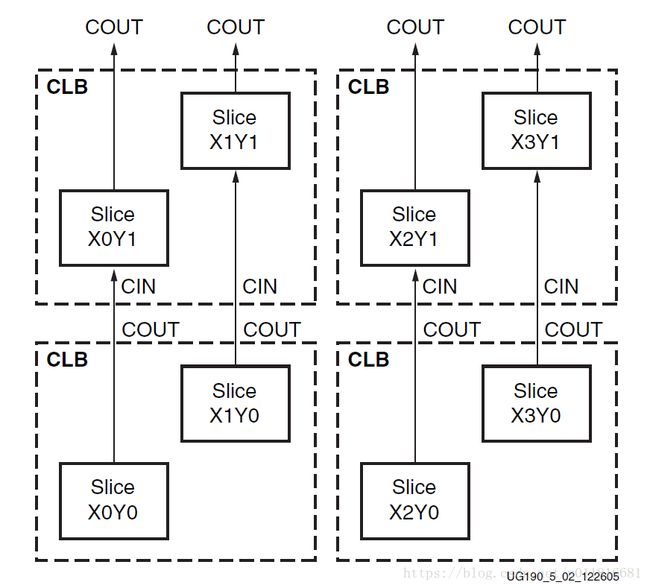

一个CLB包含两个Slice,两个Slice分别位于独立的列,有各自的进位链,他们相互不连接。每个CLB连接到一个Switch matrix上已完成布线。CLB中底部的Slice为Slice0,上部的为Slice1。

Xilinx给Slice的标号为X代表列、Y代表行,从die的左下角开始排序。

每个Slice包含4个逻辑生成器(6-LUT)、4个Storage element、4个Wide-function multiplexer、1个进位逻辑。这些器件可以实现逻辑、算术运算、ROM的功能。此外,有一些Slice可以支持2种额外功能:用Distributed RAM存数、32位移位寄存器,这些有额外功能的Slice叫SliceM。其他的Slice叫SliceL。

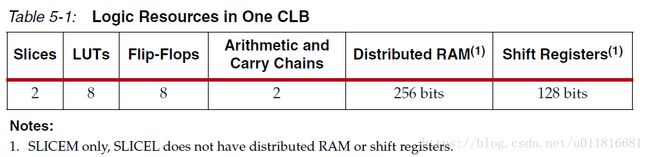

每个CLB可以提供的逻辑资源如下。

Slice中的逻辑生成器由6-LUT实现。每个6-LUT有6个独立输入(A1~A6)、两个独立输出(O5、O6)。6-LUT可以实现任意6输入布尔逻辑,也可以实现任意两个5输入布尔逻辑,只要这两个逻辑运算有共同输入。O6是6输入布尔逻辑运算的输出,而O5、O6是5输入布尔逻辑运算的输出。一个6-LUT的延迟是与所计算的逻辑函数无关的。布尔逻辑运算的结果可以①输出Slice(O6通过A、B、C、D,O5通过AMUX、BMUX、CMUX、DMUX),②O6的输出可以进入一个专用异或门,③O5的输出可以进入进位逻辑链,④O6的输出还可以进入进位逻辑选择器的选择端,⑤进入Storage element的数据输入端口,⑥O6的输出进入F7AMUX/F7BMUX。

F7AMUX/F7BMUX、F8MUX是用来组合四个6-LUT用的,可以提供7输入布尔逻辑运算、8输入布尔逻辑运算。更多输入的布尔逻辑运算需要更多的Slice。

CLB中的Storage element可以配置为边沿触发的DFF或者锁存器。配置为DFF时,DFF的输入可以是6-LUT的输出通过AFFMUX、BFFMUX、CFFMUX、DFFMUX这4个选择器输入,或者通过AX、BX、CX、DX输入而passby掉6-LUT。配置为锁存器是,当CLK为低时,输出随输入变化(transparent)。

Storage element的控制信号有时钟(CK)、时钟使能(CE)、置位复位(SR)、取反(REV)。一个Slice中所有Storage element共用相同的控制信号,但是时钟信号的极性可以不同(通过时钟路径上的非门实现)。

Attribute SRHIGH决定了当SR assert时,输出高。而Attribute SRLOW决定了当SR assert时,输出低。同时REV assert时输出取反。Slice中的每个storage element的Attribute SRHIGH 与Attribute SRLOW都能独立设置。但是SR是同步还是异步则不能独立设置。

Attribute INT0与Attribute INT1设置了Storage element的初始值。默认情况设置Attribute SRLOW时设置了INIT0,而设置Attribute SRHIGH时设置了INIT1。但是Attribute INT0与Attribute INT1可以独立于Attribute SRLOW、Attribute SRHIGH单独设置。

SliceM中的6-LUT可以配置为Distributed RAM。

每种RAM所需的LUT数量如下,

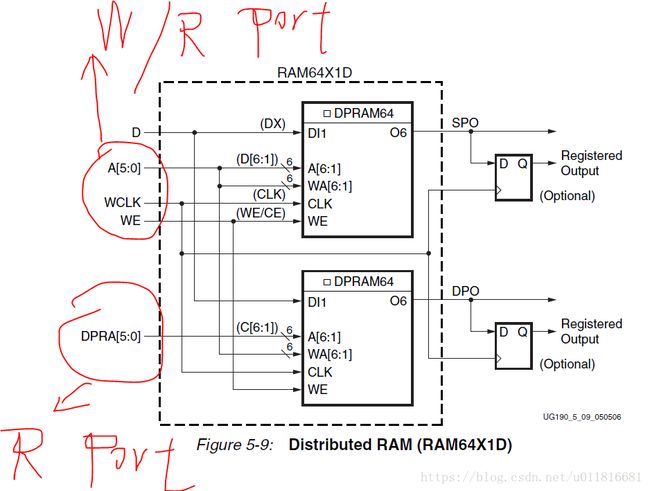

单端口模式时,分布式RAM的同步写、异步读共用相同的端口。双端口模式时,分布式RAM的一个端口用于同步写、异步读,另一个用于异步读。对于四端口模式时,一个端口用于同步写和异步读,另三个用于异步读。

单端口模式中,读写共用相同的地址总线,双端口模式中,一个函数生成器连接共用的读写地址,另一个函数生成器的A pin连接第二个端口的只读地址总线,WA pin连接第一端口的读写地址总线。

上图是4端口32x2 bit RAM,A~C是只读端口,D是读写端口,4个函数生成器(DPRAM32)的输入DI1、DI2是输入的2bit数据。

上图是单个2端口32x6 bit RAM,用4个函数生成器实现一个双端口RAM。

上图是用1个函数生成器实现的单端口64x1 bit RAM。DI1是1bit数据输入,A是读写地址。

上图是双端口64x1 bit RAM。

同步写操作:时钟沿来到的时候,当写使能为高,数据端口的数据写入RAM中地址A处。

异步读操作:输出由A pin决定(单端口模式或者双端口模式中的SPO pin)、DPRA pin决定(双端口模式中的DPO pin)。只要地址端口变化,一定的LUT延迟后,输出就会变。

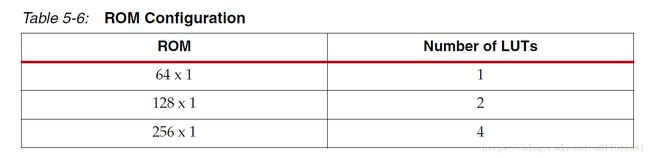

配置为只读ROM所需的函数生成器数量如下表。

SliceM、SliceL都可以配置为64x1 bit ROM、128x1 bit ROM、256x1 bit ROM。

SliceM可以配置为32位移位寄存器。

函数生成器还可以实现选择器。

Slice中的进位逻辑资源用于算术加、减法。