基于xilinx 平台的dma调试体会

年前最后一天,心不能飞。

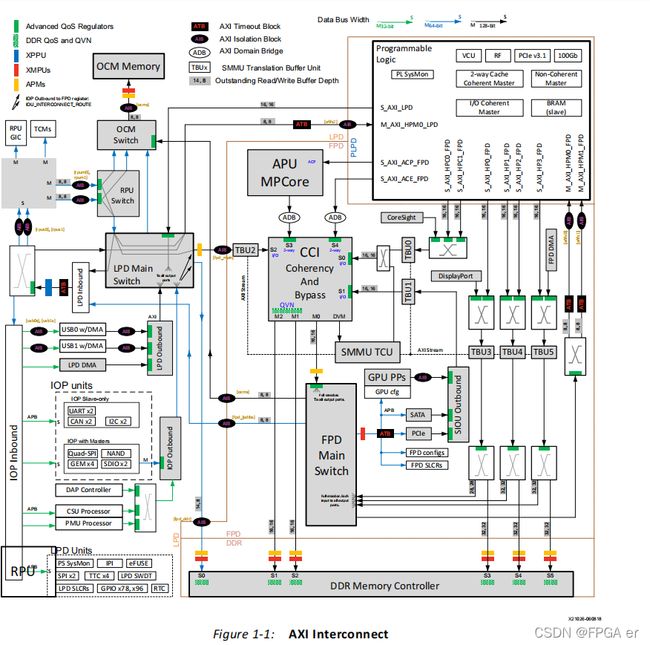

1. AXI协议介绍

Xilinx ZYNQ或者UltraScale+ 芯片集成了ARM核和传统FPGA,具有硬件集成度高,ARM和FPGA的通信速率快,外部接口可灵活配置等优点。很适合应用在视觉、AI等领域。ARM和FPGA的数据交互大致有中断、寄存器和AXI等几种方式。

a. 中断, xilinx的soc芯片提供了专门的中断接口,由pl给到ps;

b. 寄存器, ps产生控制信号或者提供参数给到pl使用,或者ps读取pl侧的逻辑状态;

c. 当ps和pl需要频繁地的交互大量数据时,通常需要用到axi-dma;

在ZYNQ或者UltraScale+ 中支持三种AXI总线, 分别是

AXI4: 主要面向高性能地址映射通信的需求,是面向地址映射的接口,允许最大256的数据突发传输。

AXI-LITE: 轻量级的地址映射单次传输接口,占用很少的逻辑单元。

AXI-Stream: 面向高速数据流传输,去掉地址项,允许无限制的数据突发传输规模。

ZYNQ里pl和ps的接口共有9个接口

AXI-ACP:加速一致性接口,用来管理dma之类不带缓冲的AXI外设,PS端是slave接口,通过该接口PL

端可以直接访问PS部分的cache, 故PL逻辑可以直接从cache中拿到cpu的计算结果,同时第

一时间将逻辑加速运算的结果送至CPU. 用于传输少量数据。

AXI-HP: 高性能axi接口,共4个主要是为了PL访问PS上的存储器(DDR 和 OCM)而设计的高速数据通

路。

AXI-GP: 通用axi接口,共4个,包括两个32位主设备接口和两个32位从设备接口。

2. DMA介绍以及调试体会

PL和PS之间的接口(ACP,GP,HP)只支持AXI4和AXI-Lite协议,PL端的AXI-Stream协议是不能直接与PS相连的,需要先经过AXI4和AXI-lite转换,比如dma/vdma 的ip就是在pl的内部实现了AXI_Stream到AXI4的转换。PL和PS通过dma的方式进行数据传输时,PL输出的数据通过AXIS总线将数据先存入该模块中的FIFO,再将FIFO中的数据读出通过AXI4总线将数据发送给PS。xinlinx提供了dma的ip,也可以手动编写dma代码,并不复杂,可以更加方便调试。如果使用提供的ip, 配置好相关参数,通过axi-lite接口将长度,地址等信息配置下去即,相对来说较为简单;如果是手写dma,则重点要注意**m_axi_s2mm_awvalid 信号

每次通过AXI4总线发送一次burst传输之前先要发送控制请求m_axi_s2mm_awvalid ,并伴随发送起始地址、burst长度等信息。等待m_axi_s2mm_awready应答才可以进行burst传输。在目前的设计中,当一次m_axi_s2mm_awvalid发送,并且等到m_axi_s2mm_awready应答后,除非等待当前的burst传输完成,否则不再发送 m_axi_s2mm_awvalid请求。发送m_axi_s2mm_awvalid请求条件分为两种情况。

s2mm_ressize >= burst_size

这种情况表明至少还需要一个满burst才能将剩余的数据全部传输完成。此时当fifo_burst_cnt大于0时,表明fifo中至少还存在一个burst以上的数据量, 即可发是哪个控制请求。

s2mm_ressize < burst_size

这种情况表明只需再进行最后一次burst传输即可将剩下所有数据传输完,并且剩余的数据量不能占满一个burst. 此时fifo_burst_cnt恒为0,当fifo中的字节数量等于s2mm_ressize时表明剩余所有数据都已经写入fifo, 即可以发送m_axi_s2mm_awvalid请求,在这种burst传输下,当burst前面时钟周期已经将fifo中的数据都传输完成,burst内后面的时钟周期数据全部为0,并把对应的m_axi_s2mm_wstrb置0.

3. 提高dma传输效率的方法尝试

对于某些加速应用,pl和ps需要频繁地的交互,这个时候dma的传输效率显得尤为关键,有以下几种方法 可以尝试:

1: 通QoS设置优先级,通过写寄存器将其中的某个HP口的优先级设置提高,其他的HP口的优先级次之。 参考ug1085和ug585。

参考ug1085的437页读写仲裁这一部分,可以通过修改PCFGR和PCFGW来实现优先级的设定。HP Port使用的为DDRC的port3-5,可以修改PCFGR_3-5和PCFGW3-5,相关寄存器描述见此链接:https://www.xilinx.com/html_docs/registers/ug1087/ug1087-zynq-ultrascale-registers.html

2 : 对于utralscale +系列的芯片,由下图(pg1085)可知,PS_DDR控制器有6个AXI-Slave接口,与PL直接相关的是S3, S4, S5。 HPC0/HPC1都连接到了CCI interconnect. DP和HP0连接到了S3, HP1和HP2连接到了S4上,HP3和 FP DMA连接到了S5。如果需要提高带宽,要充分利用PS-DDR控制器的AXI Slave接口,如果可能,HP1和HP2最好不要同时使用,因为HP1和HP2都连接到了S4上,彼此会竞争带宽。

3 : 将DMA的读写突发长度适当的加大也有利于提高传输效率;

以上内容编写较为匆忙,可能有些许纰漏,欢迎指出讨论。