AMBA 2 AHB、AMBA 3 AHB(AHB_Lite)和AMBA 5 AHB协议比较

官方手册:AMBA系列官方协议规范文档,点击下载

更详细的内容建议阅读官方协议规范

路 线:

- 【verilog实战】同步FIFO的设计与功能验证(附源码)

- 【Verilog实战】异步FIFO设计和功能验证(附源码)

- 【Verilog实战】UART通信协议,半双工通信方式(附源码)

- 【Verilog实战】SPI协议接口设计和功能验证(附源码)

- 【Verilog实战】AMBA 3 APB接口设计和功能验证(附源码)

- 【Verilog实战】AMBA 3 AHB-Lite接口设计和功能验证(附源码)

- 【Verilog实战】AMBA AXI接口设计和功能验证(附源码)

- 【Verilog实战】UART2APB bridge 设计和功能验证(附源码)

- 【Verilog实战】AHB2APB bridge 设计和功能验证(附源码)

文章目录

- 一、AHB协议

-

- 1.1 简介

- 二、 AMBA 2 AHB(AHB2)

-

- 2.1 Interface

- 2.2 关于AMBA 2 AHB

- 2.3 AMBA握手机制

- 2.4 典型系统

- 2.5 互联类型

- 2.6 传输类型

- 2.7 传输大小

- 2.8 突发操作

- 2.9 保护控制

- 2.10 时序

- 2.11 地址译码

- 2.12 从机传输响应

- 2.13 数据总线的端结构

- 2.14 仲裁

- 2.15 分块传输

- 2.16 分块传输的总线移交

- 三、 AMBA 3 AHB(AHB_Lite)

-

- 3.1 特性

- 3.2 架构

- 3.3 接口

- 四、 AMBA 5 AHB(对比)

-

- 4.1 接口

- 4.2 特性

- 4.3 特点

- 4.4 传输响应

- 4.5 突发类型

- 4.6 传输类型

- 4.7 传输大小

- 4.8 保护类型

一、AHB协议

1.1 简介

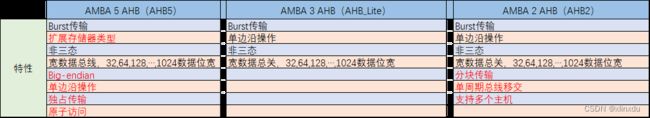

AHB2 :AMBA 2 AHB(AHB2),多master多slave框架,需要仲裁器

AHB3 :AMBA 3 AHB(AHB_Lite),单master多slave,没有仲裁器(AHB2的简化版)

AHB5 :AMBA 5 AHB,单master多slave,没有仲裁器,扩展存储器类型

二、 AMBA 2 AHB(AHB2)

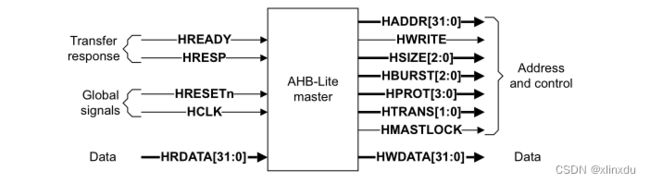

2.1 Interface

| Signal | Source | Description |

|---|---|---|

| HCLK (Bus clock) |

Clock source | This clock times all bus transfers. All signal timings are related to the rising edge of HCLK. |

| HRESETn (Reset) |

Reset controller | The bus reset signal is active LOW and is used to reset the system and the bus.This is the only active LOW signal. |

| HADDR[31:0] (Address bus) |

Master | The 32-bit system address bus. |

| HTRANS[1:0] (Transfer type) |

Master | Indicates the type of the current transfer, which can be NONSEQUENTIAL,SEQUENTIAL, IDLE or BUSY. |

| HWRITE (Transfer direction) |

Master | When HIGH this signal indicates a write transfer and when LOW a read transfer. |

| HSIZE[2:0] (Transfer size) |

Master | Indicates the size of the transfer, which is typically byte (8-bit), halfword (16-bit) or word (32-bit). The protocol allows for larger transfer sizes up to a maximum of 1024 bits. |

| HBURST[2:0] (Burst type) |

Master | Indicates if the transfer forms part of a burst. Four, eight and sixteen beat burstsare supported and the burst may be either incrementing or wrapping. |

| HPROT[3:0] (Protection control) |

Master | The protection control signals provide additional information about a bus access and are primarily intended for use by any module that wishes to implement some level of protection. The signals indicate if the transfer is an opcode fetch or data access, as well as if the transfer is a privileged mode access or user mode access. For bus masters with a memory management unit these signals also indicate whether the current access is cacheable or bufferable. |

| HWDATA[31:0] (Write data bus) |

Master | The write data bus is used to transfer data from the master to the bus slaves during write operations. A minimum data bus width of 32 bits is recommended.However, this may easily be extended to allow for higher bandwidth operation. |

| HSELx (Slave select) |

Decoder | Each AHB slave has its own slave select signal and this signal indicates that the current transfer is intended for the selected slave. This signal is simply a combinatorial decode of the address bus. |

| HRDATA[31:0] (Read data bus) |

Slave | The read data bus is used to transfer data from bus slaves to the bus master during read operations. A minimum data bus width of 32 bits is recommended. However, this may easily be extended to allow for higher bandwidth operation. |

| HREADY (Transfer done) |

Slave | When HIGH the HREADY signal indicates that a transfer has finished on the bus. This signal may be driven LOW to extend a transfer. Note: Slaves on the bus require HREADY as both an input and an output signal. |

| HRESP[1:0] (Transfer response) |

Slave | The transfer response provides additional information on the status of a transfer.Four different responses are provided, OKAY, ERROR, RETRY and SPLIT. |

AMBA 2 AHB也有许多信号请求支持多主机操作(见下表) ,这些仲裁信号用于点对点连接,下表中后缀x用来表示信号来自模块x 例如,一个系统中会有许多的信号HBUSREQx,比如HBUSREQarm,HBUSREQdma和HBUSREQtic。

| Signal | Source | Description |

|---|---|---|

| HBUSREQx (Bus request ) |

Master | A signal from bus master x to the bus arbiter which indicates that the bus master requires the bus. There is an HBUSREQx signal for each bus master in the system, up to a maximum of 16 bus masters. |

| HLOCKx (Locked transfers) |

Master | When HIGH this signal indicates that the master requires locked access to the bus and no other master should be granted the bus until this signal is LOW. |

| HGRANTx(Bus grant) | Arbiter | This signal indicates that bus master x is currently the highest priority master. Ownership of the address/control signals changes at the end of a transfer when HREADY is HIGH, so a master gets access to the bus when both HREADY and HGRANTx are HIGH. |

| HMASTER[3:0] (Master number) |

Arbiter | These signals from the arbiter indicate which bus master is currently performing a transfer and is used by the slaves which support SPLIT transfers to determine which master is attempting an access. The timing of HMASTER is aligned with the timing of the address and control signals. |

| HMASTLOCK (Locked sequence) |

Arbiter | Indicates that the current master is performing a locked sequence of transfers. This signal has the same timing as the HMASTER signal. |

| HSPLITx[15:0] (Split completion request) |

Slave (SPLIT-capable) |

This 16-bit split bus is used by a slave to indicate to the arbiter which bus masters should be allowed to re-attempt a split transaction. Each bit of this split bus corresponds to a single bus master. |

2.2 关于AMBA 2 AHB

Advanced Microcontroller Bus Architecture(AMBA)是由ARM公司制定的高性能 片上(on chip)通信标准。常用的有以下三种协议:

- Advanced High-performance Bus(AHB)

- Advanced Peripheral Bus(APB)

- Advanced eXtensible Interface(AXI)

一般设计中AXI和AHB用于高带宽、高性能、低延时场合,如DMA、Memory controller、MCU总线互连等。APB用于对带宽、性能要求不敏感的场合,如外设bridge、寄存器配置等。

AMBA AHB 是位于 APB 之上新一级的总线并且实现了高性能、高系统时钟频率系统的以下特征要求:

- burst transfers (突发传输)

- split transactions (分块处理,分块(SPLIT)和重试(RETRY)响应给从机提供了在无法立刻给传输提供数据时释放总线的机制。这两种机制都允许在总线上结束传输因此允许更高优先级的主机能够访问主机)

- single-cycle bus master handover(单周期总线主机移交)

- single-clock edge operation (单时钟沿操作)

- non-tristate implementation (无三态)

- wider data bus configurations (64/128 bits)(更宽的数据总线架构(根据个人情况配置))

2.3 AMBA握手机制

AMBA采用valid和ready进行master和slave之间的握手。master发出valid和data,slave反馈ready给master。valid为data的有效指示,ready为slave可以接收数据的指示,握手成功发生在valid和ready同时为高时。

AMBA采用valid和ready进行master和slave之间的握手。master发出valid和data,slave反馈ready给master。valid为data的有效指示,ready为slave可以接收数据的指示,握手成功发生在valid和ready同时为高时。

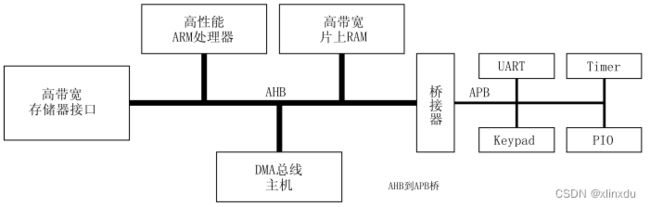

2.4 典型系统

基于AMBA的微控制器典型地由一个高性能系统中枢总线组成,能够支持外部存储器带宽,包括CPU,片上存储器和其他直接数据存取(DMA)设备,加上一个桥接器连接到较窄的挂接着较低带宽外设的APB总线。

基于AMBA的微控制器典型地由一个高性能系统中枢总线组成,能够支持外部存储器带宽,包括CPU,片上存储器和其他直接数据存取(DMA)设备,加上一个桥接器连接到较窄的挂接着较低带宽外设的APB总线。

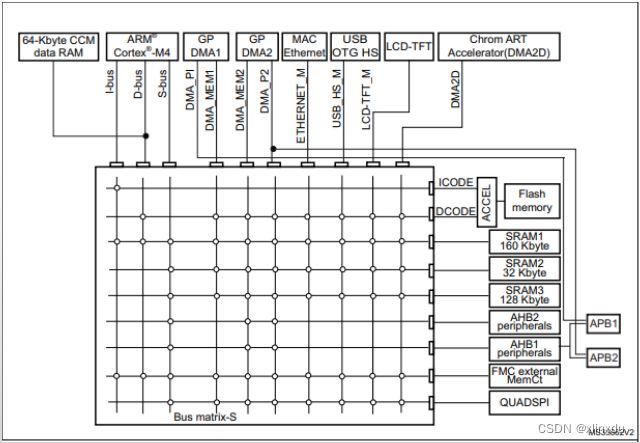

AHB协议在Bus matrix(crossbar)架构中的应用如下:

2.5 互联类型

AHB2协议可以实现多master多slave互连。多master互连时需要arbiter对master请求进行仲裁。(AHB-Lite只能用于单master互连)

2.6 传输类型

每个传输都可以被分类为四个不同类型之一,如HTRANS[1 :0]信号所表示的状态。

| HTRANS[1:0] | Type | Description |

|---|---|---|

| 00 | IDLE(空闲) | Indicates that no data transfer is required. The IDLE transfer type is used when a bus master is granted the bus, but does not wish to perform a data transfer. Slaves must always provide a zero wait state OKAY response to IDLE transfers and the transfer should be ignored by the slave. |

| 01 | BUSY(忙) | The BUSY transfer type allows bus masters to insert IDLE cycles in the middle of bursts of transfers. This transfer type indicates that the bus master is continuing with a burst of transfers, but the next transfer cannot take place immediately. When a master uses the BUSY transfer type the address and control signals must reflect the next transfer in the burst. The transfer should be ignored by the slave. Slaves must always provide a zero wait state OKAY response, in the same way that they respond to IDLE transfers. |

| 10 | NONSEQ(非连续) | Indicates the first transfer of a burst or a single transfer. The address and control signals are unrelated to the previous transfer. Single transfers on the bus are treated as bursts of one and therefore the transfer type is NONSEQUENTIAL.(表示一次突发的第一个传输或者一个单一传输。地址和控制信号和前一次传输无关。) |

| 11 | SEQ(连续) | The remaining transfers in a burst are SEQUENTIAL and the address is related to the previous transfer. The control information is identical to the previous transfer. The address is equal to the address of the previous transfer plus the size (in bytes). In the case of a wrapping burst the address of the transfer wraps at the address boundary equal to the size (in bytes) multiplied by the number of beats in the transfer (either 4, 8 or 16).(突发传输中除去第一个,剩下的传输是连续传输并且地址和前一次传输有关。控制信息和前一次传输一样,地址等于前一次传输的地址加上传输大小(字节)。) |

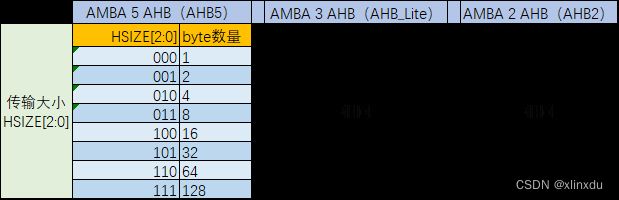

2.7 传输大小

**HSIZE[2:0]**表示传输的大小,即代表每次传输的数据大小,最高支持1024bit。和HBURST[2:0]信号一起决定回环突发的地址边界。

| HSIZE[2] | HSIZE[1] | HSIZE[0] | Size | Description |

|---|---|---|---|---|

| 0 | 0 | 0 | 8bit | Byte |

| 0 | 0 | 1 | 16bit | Haftword |

| 0 | 1 | 0 | 32bit | Word |

| 0 | 1 | 1 | 64bit | - |

| 1 | 0 | 0 | 128bit | 4-word line |

| 1 | 0 | 1 | 256bit | 8-word line |

| 1 | 1 | 0 | 512bit | - |

| 1 | 1 | 1 | 1024bit | - |

2.8 突发操作

AMBA 2 AHB 协议定义了4、8和16拍突发传输,也有未定长度的突发和信号传输。协议对增量和回环都支持:

| HBURST[2:0] | Type | Description |

|---|---|---|

| 000 | SINGLE | Single transfer(单一传输) |

| 001 | INCR | Incrementing burst of unspecified length(未指定长度的增量突发传输) |

| 010 | WRAP4 | 4-beat wrapping burst(4拍回环突发传输) |

| 011 | INCR4 | 4-beat incrementing burst(4拍增量突发传输) |

| 100 | WRAP8 | 8-beat wrapping burst(8拍回环突发传输) |

| 101 | INCR8 | 8-beat incrementing burst(8拍增量突发传输) |

| 110 | WRAP16 | 16-beat wrapping burst(16拍回环突发传输) |

| 111 | INCR16 | 16-beat incrementing burst(16拍增量突发传输) |

- 增量突发访问连续地址并且突发中的每次传输地址仅是前一次地址的一个增量;

- 对于回环突发,如果传输的起始地址并未和突发(x 拍)中字节总数对齐那么突发传输地址将在达到边界处回环。例如,一个

4拍回环突发的字(4 字节)访问将在16 字节边界回环。因此,如果传输的起始地址是 0x30,那么它将包含四个到地址0x30、0x34、0x38 和 0x3C,继续传输时,地址又会从0x30开始。如果是4拍增量突发传输,那么它将包含四个到地址0x30、0x34、0x38 和 0x3C,继续传输。地址会从0x40开始,0x44、0x48、0x4C这样增加,这就是回环和增量的区别。

注意:突发禁止超过 1KB(1024bit) 的地址边界。因此主机不要尝试发起一个将要超过这个边界的定长增量突发;在执行单个传输时使用未指定长度的增量突发可以理解为长度为1的突发;一个增量突发可以是任何长度,但是(长度)上限由“

地址不能超过 1KB 边界”这个事实限定了。

- 所有突发传输必须将地址边界和传输大小对齐。例如,字传输必须对齐到字地址边界(也就是 A[1:0] = 00),半字传输必须对齐到半字地址边界(也就是 A[0] = 0)。

怎么理解这个地址对齐呢,以4拍回环突发为例

| 8bit | 16bit | 32bit | 64bit | 总结 |

|---|---|---|---|---|

| addr+1 | addr+2 | addr+4 | addr+8 | - |

| 0->1->2->3->0 | 0->2->4->6->0 | 0->4->8->C->0 | 0->8->10->18->0 | - |

| 00 01 10 11 高两位累加 |

00 0 01 0 10 0 11 0 最低位不变,高两位累加 |

00 00 01 00 10 00 11 00 低两位不变,高两位累加 |

00 000 01 000 10 000 11 000 低三位不变,高两位累加 |

16bit->[0]=0 32bit->[1:0]=00 64bit->[2:0]=000 128bit->[3:0]=0000 … |

注意:突发大小表示突发的节拍数量,并不是一次突发传输的实际字节数量。一次突发传输的数据总量可以用节拍数乘以每拍数据的字节数来计算,每拍字节数由 HSIZE[2 :0]指示。

2.9 保护控制

| HPROT[3] (cacheable) (高速缓存) |

HPROT[2] (bufferable ) (带缓冲的) |

HPROT[1] (privileged) (特权模式) |

HPROT[0] (data/opcode) (数据/预取指) |

Description |

|---|---|---|---|---|

| - | - | - | 0 | Opcode fetch(预取指) |

| - | - | - | 1 | Data access(数据访问) |

| - | - | 0 | - | User access(用户模式访问) |

| - | - | 1 | - | Privileged access(特权模式访问) |

| - | 0 | - | - | Not bufferable(无缓冲) |

| - | 1 | - | - | Bufferable(带缓冲) |

| 0 | - | - | - | Not cacheable(无高速缓存) |

| 1 | - | - | - | Cacheable(带高速缓存) |

官方手册里面有这样一句话:Not all bus masters will be capable of generating accurate protection information, therefore it is recommended that slaves do not use the HPROT signals unless strictly necessary.大概的意思是说:不是所有的总线主机都能产生准确的保护信息,因此,如果从机没有严格必要使用的情况下,不建议使用HPROT信号。(我也是初学,不知道这个信号重不重要,可能没那么重要吧)

2.10 时序

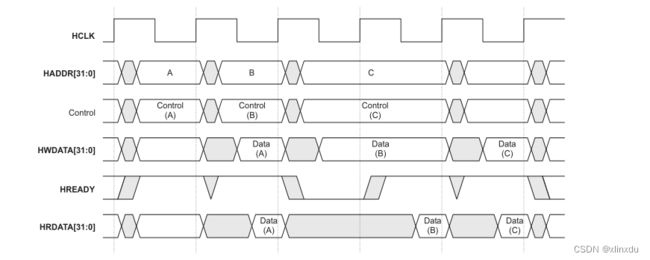

(1)基本传输

AHB2 传输可分为两部分:

- 地址相位,只持续单个周期;

- 数据相位,可能需要多个周期,通过HREADY信号扩展实现;

- 无等待传输

在这个没有等待状态的简单传输中:

- 主机在 HCLK 的上升沿之后将地址和控制信号驱动到总线上;

- 然后在时钟的下一个上升沿,主机驱动写数据到总线上,且从机采样地址和控制信息;

- 在从机采样了地址和控制信号后,开始驱动适当的响应并且该响应被总线主机在第三个时钟的上升沿采样。

注:这个例子演示了在不同的时钟阶段传输的地址和数据相位是如何产生的。事实上,任何传输的

地址相位在前一次传输的数据相位期间出现。这种地址和数据的交叠是总线传输通道的基本性质同时允许高性能的操作,同时给从机提供足够的时间来产生传输响应。

注:控制信息包括传输方向HWRITE,传输大小HSIZE[2:0],保护控制HPROT[3:0]

- 带等待状态的传输

官方手册有这样两句话:

- For write operations the bus master will hold the data stable throughout the extended cycles.

- For read transfers the slave does not have to provide valid data until the transfer is about to complete.

大概的意思是,对于写操作而言,主机必须保持总线数据在整个扩展周期中稳定不变化;对于读操作,从机没有必要在传输即将结束前一直提供有效的数据。

官方手册有这样一句话:

- When a transfer is extended in this way it will have the side-effect of extending the address phase of the following transfer.

- 当传输以HREADY扩展方式进行传输,那么在随后的传输过程中,会影响到地址相位。

- 地址A和C的传输是零等待状态

- 地址B的传输有一个等待的周期

- 传输地址B的

扩展数据相位对传输地址C的扩展地址相位产生了影响,地址C的地址相位也多维持了一个周期。

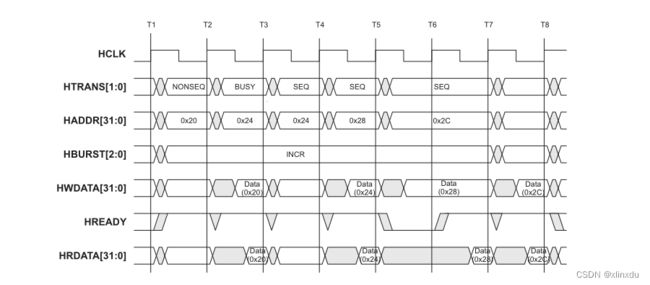

- 传输类型实例

- 第一个传输是一次突发传输的开始,所以是NONSEQ(非连续)类型;

- T2时刻,主机不能立即执行第二次突发传输,所以主机请求了一个BUSY(忙)类型来延时准备。在这个实例中,在第二次突发传输之后,没有等待状态了;

- T3时刻开始,主机立即执行第二次突发传输。T4时刻立即执行第三次突发传输。但此时,从机没有准备好,使用了HREADY来插入一个延时等待状态;

- 最后一个突发传输以无等待状态完成。

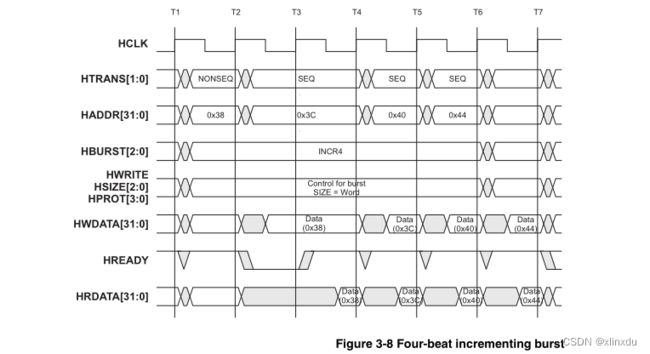

(2) a Four-beat wrapping burst(一个四拍回环突发)

(3)a Four-beat incrementing burst(一个四拍增量突发)

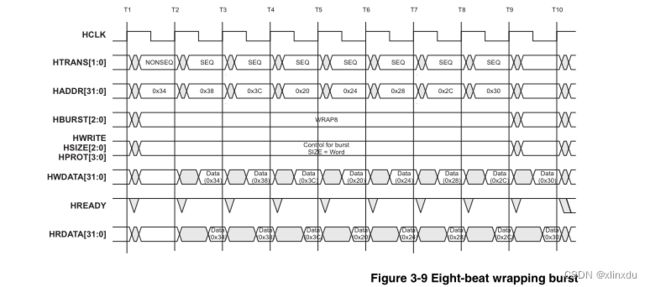

(4)an Eight-beat wrapping burst(一个八拍回环突发)

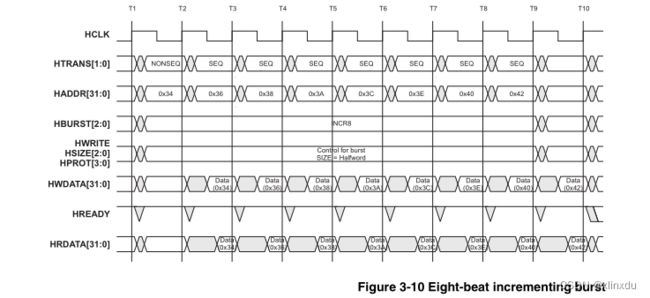

(5) an Eight-beat incrementing(一个八拍增量突发)

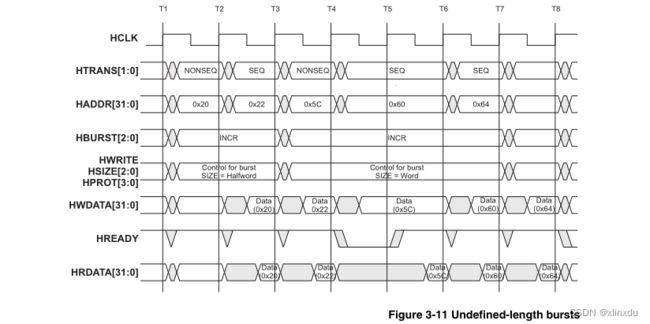

(6)Undefined-length bursts(一个未定长度的突发)

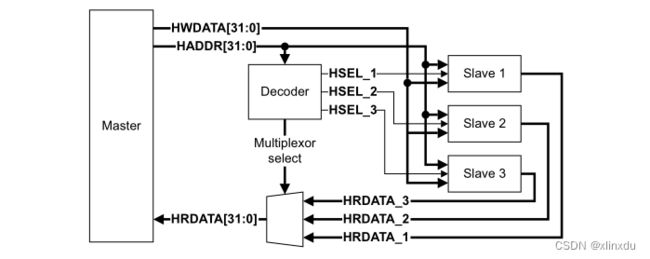

2.11 地址译码

由这张图可以发现,三个从机共用一个地址总线。通过Decoder中央地址译码器提供选择信号。(官方:The select signal is a combinatorial decode of the high-order address signals,and simple address decoding schemes are encouraged to avoid complex decode logic and to ensure high-speed operation.选择信号是高位地址信号的组合译码,并且建议使用简单的译码方案以避免复杂译码逻辑和确保高速操作。)

注:

- 从机只能在 HREADY 信号为高时采样地址和控制信号以及 HSELx,HSELx 为高表示当前传输已经完成。在特定的情况下有可能在 HREADY 为低时采样 HSELx,但是被选中的从机将会在当前传输完成后变更。

- 在系统设计中如果有包含一个存储器映射并未完全填满(存储空间)的情况时,应该设置一个额外的默认从机,以在访问任何不存在的地址空间时提供响应。如果一个非连续或者连续传输试图访问一个不存在的地址空间时,这个默认从机应该提供一个 ERROR 响应。空闲或者忙传输访问不存在的空间(默认从机)应该给出一个零等待状态的 OKAY 响应。这个默认从机的功能将以作为中央地址译码器的一部分来实现。

2.12 从机传输响应

值得注意的是,AHB协议中,在主机发起传输后,由从机决定传输如何进行。而且只要从机被访问,那么它必会提供一个表示传输状态的响应。其中HREADY信号用来扩展传输,和响应信号HRESP[1:0]结合以表示相应的传输状态。

从机能提供多种状态完成传输:

- 立即完成传输;

- 插入一个或者多个等待状态以允许有时间来完成传输;

- 发出一个错误信号来表示传输失败;

- 延时传输的完成,但是允许主机和从机放弃总线,把总线留给其他传输使用。

(1)传输完成(Transfer done)

HREADY 信号用来扩展一次 AHB 传输的数据部分(也会影响到地址总线)。当 HREADY 信号为低时,表示传输将被扩展;直到其为高时,表示传输完成。

官方:

- Every slave must have a predetermined maximum number of wait states that it will insert before it backs off the bus, in order to allow the calculation of the latency of accessing the bus. It is recommended, but not mandatory, that slaves do not insert more than 16 wait states to prevent any single access locking the bus for a large number of clock cycles.

- 在从机放弃总线之前,每个从机必须有一个预先确定插入的最大等待状态数目,以便能够计算访问总线的延时。建议但不强制规定,从机不要插入多于 16 个等待状态以防止任何单个访问将总线锁定较长的时钟周期。

(2)传输响应(Transfer response)

| HRESP[1] | HRESP[0] | Response | Description |

|---|---|---|---|

| 0 | 0 | OKAY | 当 HREADY 为高时,表示传输已经成功完成。OKAY 响应也被用来插入任意一个附加周期,当 HREADY 为低时,优先给出其他三种响应之一。 |

| 0 | 1 | ERROR | 该响应表示发生了一个错误。错误条件应该发信号给总线主机,以便让主机意识到传输失败。一个错误条件需要双周期响应。 |

| 1 | 0 | RETRY | RETRY(重试)信号表示传输并未完成,因此总线主机应该重试传输。主机应该继续重试传输,直到完成为止。要求双周期的 RETRY 响应。 |

| 1 | 1 | SPLIT | 传输并未成功完成。总线主机必须在下一次被授予访问总线时重试传输。当传输能够完成时从机将请求代替主机访问总线。要求双周期的 SPLIT 响应。 |

- 典型的从机将会用 HREADY 信号来在传输中,插入适当数量的等待状态;而传输在HREADY 为高时完成,并且给出 OKAY 响应,表示传输成功完成。

- ERROR 响应被从机用来表示某种形式的错误条件和相关的传输。典型的被用作保护错误,例如试图写一个只读的存储空间。

- SPLIT 和 RETRY 响应组合允许从机延长传输完成的时间,但是释放总线给其他主机使用。这些响应组合通常仅由有高访问延时的从机请求并且从机能够利用这些响应编码来确保其他主机在长时间内不被阻止访问总线。(下面会详细讲分块和重试)

(3)双周期响应(Two-cycle response)

仅有 OKAY 响应可以在单个周期里给出,ERROR、SPLIT 和 RETRY 响应需要至少两个周期。为了完成这些响应中的任意一个那么在

仅有 OKAY 响应可以在单个周期里给出,ERROR、SPLIT 和 RETRY 响应需要至少两个周期。为了完成这些响应中的任意一个那么在倒数第二个(最后一个的前一个)周期从机驱动 HRESP[1 :0]以表示 ERROR、RETRY 或者 SPLIT 并同时驱动 HREADY 为低以给传输扩展一个额外的周期。在最后一个周期 HREADY 被驱动为高电平以结束传输,同时HRESP[1 :0]保持驱动以表示 ERROR、RETRY 或者 SPLIT。

上图是一次RETRY操作的例子。在上图中,T2时刻,驱动HREADY为低电平,同时HRESP状态为RETRY;T3驱动HREADY为高电平,同时HRESP维持原来的状态一个周期。

过程可以理解为:

- 主机从地址 A 发起传输;

- 这次传输在接收到响应之前主机将地址移动到 A + 4;

- 从机在地址 A 不能立刻完成传输,因此从机发出一个 RETRY 响应。该响指示主机在地址 A 的传输无法完成并且在地址 A + 4 的传输被取消而用空闲传输替代。

(4)错误响应(Error response)

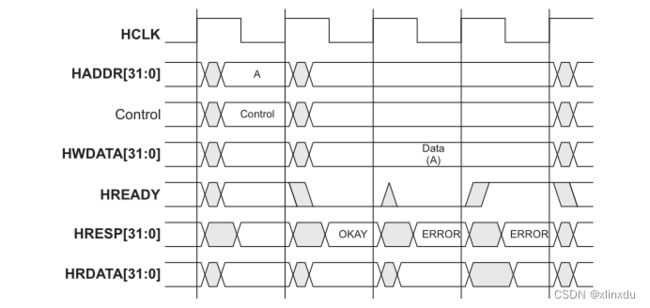

上图表示在一个传输中,从机请求一个周期来决定它将要给出的响应(在此期间HRESP为OKAY状态),之后从机用一个双周期的ERROR状态响应结束传输(在第二个ERROR时,HREADY驱动为高电平)。

上图表示在一个传输中,从机请求一个周期来决定它将要给出的响应(在此期间HRESP为OKAY状态),之后从机用一个双周期的ERROR状态响应结束传输(在第二个ERROR时,HREADY驱动为高电平)。

官方

- If a slave provides an ERROR response then the master may choose to cancel the remaining transfers in the burst. However, this is not a strict requirement and it is also acceptable for the master to continue the remaining transfers in the burst.

- 大概的意思是:如果从机提供一个错误响应,那么主机可以选择取消突发中剩下的传输。也可以继续突发中剩下的传输,没有严格的要求。

(5)分块和重试(Split and retry)

分块和重试响应给从机提供了在无法立刻给传输提供数据时,释放总线的机制。这两种机制都允许在总线上结束传输,因此允许更高优先级的主机能够访问主机。

分块(SPLIT)和重试(RETRY)的不同之处在于仲裁器在发生 SPLIT 和 RETRY 后分配总线的方式:

- 对于 SPLIT 传输而言,仲裁器将调整优先级方案,以便其他任何主机请求总线都能获得总线访问权,即使是优先级较低的主机。为了完成一个 SPLIT 传输,当从机有可用数据时,从机必须通知仲裁器。

- 对RETRY而言,仲裁器将继续使用常规优先级方案,因此拥有更高优先级的主机将优先获得总线访问权。

SPLIT 传输虽然增加了仲裁器和从机的复杂性,但是却有可以完全释放总线给其他主机使用的优点,而在 RETRY(响应)的情况下,就只允许较高优先级的主机使用总线。

2.13 数据总线的端结构

对于宽度小于总线宽度的传输,例如一个在 32 位总线上的 16 位传输,那么总线主机仅需要驱动相应的字节通道,从机负责从正确的字节通道选择写数据。有效字节通道取决于系统的端结构(小端系统和大端系统),但是 AHB 并不指定要求的端结构。因此,总线上所有主机和从机的端结构相同这点很重要。

- 32位小端数据总线的有效字节通道

| Transfer size 传输大小 |

Address offset 地址偏移 |

DATA[31:24] | DATA[23:16] | DATA[15:8] | DATA[7:0] |

|---|---|---|---|---|---|

| Word | 0 | Y | Y | Y | Y |

| Halfword | 0 | - | - | Y | Y |

| Halfword | 2 | Y | Y | - | - |

| Byte | 0 | - | - | - | Y |

| Byte | 1 | - | - | Y | - |

| Byte | 2 | - | Y | - | - |

| Byte | 3 | Y | - | - | - |

- 32位大端数据总线的有效字节通道

| Transfer size 传输大小 |

Address offset 地址偏移 |

DATA[31:24] | DATA[23:16] | DATA[15:8] | DATA[7:0] |

|---|---|---|---|---|---|

| Word | 0 | Y | Y | Y | Y |

| Halfword | 0 | Y | Y | - | - |

| Halfword | 2 | - | - | Y | Y |

| Byte | 0 | Y | - | - | - |

| Byte | 1 | - | Y | - | - |

| Byte | 2 | - | - | Y | - |

| Byte | 3 | - | - | - | Y |

对于宽度小于总线宽度的传输从机仅需要在有效的字节通道提供有效数据,总线主机负责从正确的字节通道中选择数据。当传输以 OKAY 响应完成时从机仅需提供有效数据。SPLIT、RETRY 和 ERROR 响应不需要提供有效的读数据。

2.14 仲裁

==仲裁器有啥用?==仲裁器可以被用来确保任何时刻只有一个master能够访问总线,即通过检测诸多访问总线的请求和决定当前请求总线的多个master中的优先级。同时仲裁器也接收来自slave的需要完成SPLIT传输的请求。

官方:

- Any slaves which are not capable of performing SPLIT transfers do not need to be aware of the arbitration process, except that they need to observe the fact that a burst of transfers may not complete if the ownership of the bus is changed.

- 任何不能执行SPLIT传输的从机不需要知道仲裁过程,除非它们需要检测因为总线的所有权被更改,而到最后传输可能无法完成的情况。

(1)信号列表

| Signal | Description |

|---|---|

| HBUSREQx | 被总线主机用来请求访问总线的总线请求信号。每个总线主机都有自己的连接到仲裁器的 HBUSREQx 信号并且任何一个系统中都可以有高达 16 个独立的总线主机。 |

| HLOCKx | 由主机在请求总线的同时时断言的锁定信号。这提示仲裁器主机正在执行一系列不可分割的传输并且一旦锁定传输的第一个传输已经开始仲裁器不能授予任何其他主机访问总线。HLOCKx 必须在涉及到的地址被寻址到之前至少断言一个周期,以防止仲裁器改变授予信号。 |

| HGRANTx | 授予信号由仲裁器产生并且表示相关主机是当前请求总线的主机中优先级最高的主机,(优先)考虑锁定传输和 SPLIT 传输。主机在 HGRANTx 为高时获取地址总线的所有权并且在HCLK 的上升沿 HREADY 为高电平。 |

| HMASTER[3 :0] | 仲裁器使用 HMASTER[3: :0]信号表示哪一个主机当前被授予总线并且该信号可被用来控制中央地址和控制多路选择器。有 SPLIT 传输能力的从机也可以请求主机的序号以便它们能够提示仲裁器哪个主机能够完成一个 SPLIT 传输。 |

| HMASTLOCK | 仲裁器通过断言 HMASTLOCK 信号指示当前传输是一个锁定序列的一部分,该信号和地址以及控制信号有相同的时序。 |

| HSPLIT[15 :0] | 这 16 位有完整分块能力的总线被有分块(SPLIT)能力的从机用来指示哪个总线主机能够完成一个 SPLIT 传输。仲裁器需要这些信息以便于授予主机访问总线完成传输。 |

(2)请求总线访问

- 总线主机使用HBUSREQx信号请求对总线的访问,并且可以在任何周期内请求总线。 仲裁器将在时钟上升时对请求进行采样,然后使用内部优先级算法来决定下一个访问总线的master。

- 通常情况下,仲裁只会在突发完成时,授予一个不同的总线主机。但是,如果需要,仲裁器可以提前终止突发,以便允许更高的优先级主机访问总线。

- 如果主机请求锁定访问,那么它也必须断言HLOCKx信号,向仲裁器表明不应该授予其他主机总线访问权。

- 当master被授予总线并且正在执行固定长度的突发时,没有必要为了完成突发而继续请求总线。仲裁器监控突发的进程,并使用HBURST[2:0]信号来确定主机需要多少个传输。如果主机希望在当前正在进行的突发之后执行第二个突发,那么它应该在突发期间重新断言请求信号。

- 如果主机在一次突发当中失去了对总线的访问,那么它必须重新断言 HBUSREQx 请求线以重新获取访问总线。

- 对未定长度的突发主机应该继续断言请求直到已经开始最后一次传输。在未定长度的突发结束时,仲裁器不能预知何时改变仲裁。

- 对于主机而言,有可能当它未申请总线时却被授予总线。这可能在没有主机请求总线并且仲裁器将访问(总线)授予一个默认的主机时发生。因此,如果一个主机并没请求访问总线,那么它驱动传输类型 HTRANS 来表示空闲传输显得很重要。

(3)授予总线访问

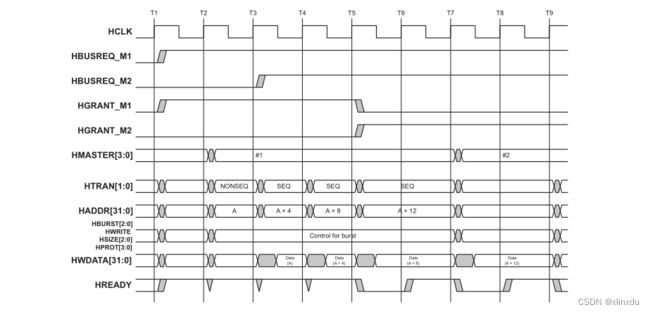

上图表示了当所有传输都为零等待状态并且HREADY信号为高时的处理过程(即无等待状态访问授予)。仲裁器通过断言相应的 HGRANTx 信号(授予信号)来表示请求总线的主机中哪个是当前优先级最高的。当当前传输完成,由 HREADY 为高时所表示,那么主机将被授予(总线)并且仲裁器将改变HMASTER[3:0]信号来表示总线主机序号。

上图表示了当所有传输都为零等待状态并且HREADY信号为高时的处理过程(即无等待状态访问授予)。仲裁器通过断言相应的 HGRANTx 信号(授予信号)来表示请求总线的主机中哪个是当前优先级最高的。当当前传输完成,由 HREADY 为高时所表示,那么主机将被授予(总线)并且仲裁器将改变HMASTER[3:0]信号来表示总线主机序号。

上图描述的是“有等待状态的访问授予”过程,有等待和无等待的区别在于HREADY是否被驱动为低电平进行扩展。即当HGRANT信号被断言(高电平)且HREADY驱动为高电平时,主机被授予总线。数据总线的所有权延时在地址总线的所有权之后。一次传输无论何时完成(由HREADY为高时所表示)然后占有地址总线的主机才能使用数据总线并且将继续占有数据总线直到传输完成。

上图描述的是“有等待状态的访问授予”过程,有等待和无等待的区别在于HREADY是否被驱动为低电平进行扩展。即当HGRANT信号被断言(高电平)且HREADY驱动为高电平时,主机被授予总线。数据总线的所有权延时在地址总线的所有权之后。一次传输无论何时完成(由HREADY为高时所表示)然后占有地址总线的主机才能使用数据总线并且将继续占有数据总线直到传输完成。

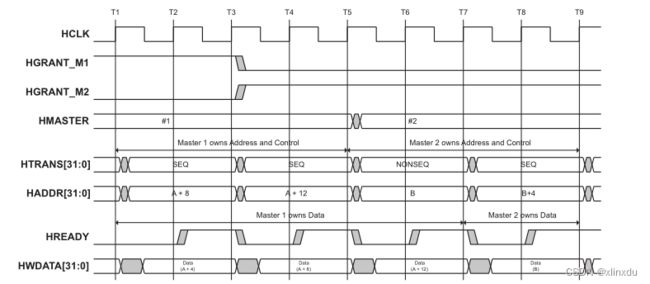

上图描述的是“两个总线主机之间,数据总线移交”过程,在T5时刻,HGRANT_M2为高,且HREADY为高,总线移交。T5时刻之后,master_2占用地址总线个控制信号。

上图描述的是“两个总线主机之间,数据总线移交”过程,在T5时刻,HGRANT_M2为高,且HREADY为高,总线移交。T5时刻之后,master_2占用地址总线个控制信号。

上图描述的是一个仲裁器在一次突发传输结束时移交总线的过程。在T7时刻,master_1已经突发完成,此时HGRANT_M2为高,HREADY为高,总线移交给master_2。我们可以看到:

上图描述的是一个仲裁器在一次突发传输结束时移交总线的过程。在T7时刻,master_1已经突发完成,此时HGRANT_M2为高,HREADY为高,总线移交给master_2。我们可以看到:仲裁器在倒数第二个(最后一个之前的)地址被采样时改变 HGRANTx 信号。新的HGRANTx 信息将在突发的最后一个地址被采样的同时被采样。

上图描述的HGRANTx和HMASTER信号是如何在系统中使用的。

上图描述的HGRANTx和HMASTER信号是如何在系统中使用的。

官方:

- Because a central multiplexor is used, each master can drive out the address of the transfer it wishes to perform immediately and it does not need to wait until it is granted the bus. The HGRANTx signal is only used by the master to determine when it owns the bus and hence when it should consider that the address has been sampled by the appropriate slave.

- 因为使用了中央多路选择器,每个主机可以立刻输出它希望执行的地址而不需要等到被授予总线。HGRANTx 信号是仅被主机用来决定它何时拥有总线并因此需要考虑何时让地址被合适的从机采样。

(4)突发提前终止

通常仲裁器在突发传输结束之前不会将总线移交给一个新的主机。但是,如果仲裁器决定突发必须被提前终止以防止过长的总线访问时间那么它可能会在一个突发完成之前将(总线)授予转移给另外一个总线主机。

如果主机在突发传输中间失去了对总线的所有权那么它必须重新断言总线(请求)以完成突发。主机必须确保 HBURST 和 HTRANS 信号都被更新以反映主机不再执行一个完整的 4、8 或者 16 拍的突发。

例如,如果一个主机仅能完成一个 8 拍突发的 3 个传输,那么当它重新获得总线时必须使用一个合法的突发编码来完成剩下的 5 个传输。主机可以使用任何合法组合,因此无论是5拍未定长度的突发或者是4拍固定长度的突发然后跟上一个单拍未定长度的突发都是可以接受的。

(5)锁定传输

仲裁器必须监视来自各个主机的HLOCKx信号,以确定master何时希望执行一个锁定连续传输。之后,仲裁器负责确保锁定传输完成之前没有其他总线主机被授予总线。

在一个连续锁定传输之后,仲裁器将始终授予总线主机一个额外的传输,以确保锁定序列的最后一个传输成功完成,并且没有接收到 SPLIT 或者 RETRY 响应。因此建议但不规定,主机在任何锁定连续传输之后,插入一个空闲传输,以便开始另外一个突发传输之前为仲裁器改变(总线授予)提供机会。

仲裁器还负责断言HMASTLOCK信号,HMASTLOCK信号、地址和控制信号具有相同的时序。该信号指示每个从机当前传输是锁定的,因此必须在其他主机被授予总线之前进行处理。

(6)默认总线主机

- 每个系统必须包含一个默认总线主机,如果所有其他主机不能使用总线时,该主机被授予总线。当被授予总线时,默认主机

必须只能执行空闲(IDLE)传输。 - 如果没有请求总线,那么仲裁器可以授予默认主机(访问总线),也可以授予从总线低访问延迟中获益最大的主机。。

- 授予默认主机访问总线还提供了一种有用的机制:确保总线上没有启动新的传输,这是进入低功耗操作模式之前执行的一个有用步骤。。

- 如果其他所有主机都在等待 SPLIT 传输完成时,则默认主机必须被授予总线。

2.15 分块传输

- 分块传输通过根据从机的响应操作来分离(或者分块)主机操作以给从机提供地址和合适的数据,提高了总线的总体使用率。

- 当传输产生时,如果从机认为传输的执行将占据大量的时钟周期,那么从机能够决定发出一个 SPLIT 响应。该信号提示仲裁器尝试这次传输的主机不应该被授予访问总线,直到从机表示它准备好了完成传输时。因此仲裁器负责监视响应信号并且在内部屏蔽已经是 SPLIT传输主机的任何请求。

- 在传输的地址相位期间,仲裁器在 HMASTER[3 :0]产生一个标记,或者总线主机序号,以表示正在执行传输的主机。任何一个发出 SPLIT 响应的从机必须表示它有能力完成这个传输,并且通过记录 HMASTER[3 :0]信号上的主机序号来实现。

- 之后,当从机能够完成传输时,它就根据主机序号,在从从机到主机的 HSPLITx[15 :0]信号上断言适当的位。然后仲裁器使用这个信息来解除来自主机请求信号的屏蔽,并且主机将被及时授予访问总线以重试传输。仲裁器在每个时钟周期采样 HSPLITx 总线,因此从机只需要

断言适当的位一个周期以便仲裁器能够识别。 - 如果系统中有多个具有SPLIT能力的从机,那么每个从机的HSPLITx总线可以

逻辑或在一起,以提供给仲裁器单个 HSPLIT 总线。 - 大多数系统中,不会使用16个总线主节点的最大容量,因此仲裁器仅要求

一个位数和总线主机数量一样的 HSPLIT 总线。但是,建议所有支持 SPLIT 的从机被设计成支持最多 16个主机。

(1)分块传输的顺序

- 主机以 和任何其他传输一样 的方式发起传输,并开始传输地址和控制信息;

- 如果从机能够立刻提供数据那么它可以马上提供数据。如果从机确认获取数据可能会占据较多的周期那么它给出一个 SPLIT 传输响应;每次传输中仲裁器广播一个序号或者标记,表示哪个主机正在使用总线。从机必须记录该序号,以便用来在之后的一段时间重新发起传输;

- 仲裁器授予其他主机使用总线并且 SPLIT 响应的动作允许主机移交总线。如果所有其他主机也接收到一个 SPLIT 响应那么默认主机将被授予总线;

- 当从机准备完成传输那么它断言 HSPLITx 总线中的适当位给仲裁器以指示哪个主机应该被重新授予访问总线;

- 仲裁器

每个时钟周期监视 HSPLITx 信号,并且当 HSPLITx 中的任何一位被断言仲裁器将恢复对应主机的优先级; - 最后仲裁器将授予(SPLIT 的)主机总线,因此主机能重新尝试传输。如果一个优先级更高的主机正在使用总线的话这可能不会立刻发生;

- 当传输终于开始后从机以一个 OKAY 传输响应来结束(传输)。

(2)多重分块传输(略)

(3)防死锁

SPLIT 和 RETRY 传输响应都必须在使用中注意预防总线死锁。单个传输决不会锁定AHB,因为每个从机必须被设计成能在预先确定的周期数内完成传输。但是,如果多个不同主机试图访问同一个从机,从机发出 SPLIT 或者 RETRY 响应以表示从机不能处理,那么就有可能发生死锁。

- 分块传输

从机可以发出 SPLIT 传输响应,通过确保从机能够承受系统中每个主机(最多 16 个)的单个请求来预防死锁。从机并不需要存储每个主机的地址和控制信息,它只需要简单的记

录传输请求已经被处理和 SPLIT 响应已经发出的事实即可。最后所有主机将处在低优先级

然后从机可以有次序的来处理这些请求,指示仲裁器正在服务于哪个请求,因而确保了所有

请求最终都被服务。

当从机有许多未完成的请求时,它可能以任何顺序(随机的)来选择处理这些请求,尽管从机需要注意锁定传输必须在任何其他传输继续之前完成。

从机使用 SPLIT 响应而不用锁存地址和控制信息显得非常合法(合适)。从机仅需要记录特定主机做出的传输尝试,并且稍后的时间段里,从机通过指示自己已经准备好完成传输,就能获取地址和控制信息。主机将被授予总线并将重新广播传输,允许从机锁存地址和控制信息并且立刻应答数据,或者发出另外一个 SPLIT 响应,如果还需要额外的一些周期的话。理想情况下从机不应该有多于它能支持的未完成传输,但是要求支持这种机制以防止总线死锁。

- 重试传输

发出 SPLIT 响应的从机必须一次只能被一个主机访问。在总线协议中并没有强制而在系统体系结构中应该确保这一点。大多数情况下发出 RETRY 响应的从机必须是一次只能被一个主机访问的外设,因此这会在一些更高级协议中得到确保。

如果要求硬件保护那么这可以被 RETRY(响应)的从机自己执行。当一个从机发出一个 RETRY 信号后它能够采样主机序号。在这之后和传输最终完成之前 RETRY 的从机可以检查做出的每次传输尝试以确保主机序号是相同的。如果从机发现主机号不一致那么它可以选择下列的行动方式:

- 一个错误响应;

- 一个信号给仲裁器;

- 一个系统级中断;

- 一个完全的系统复位。

2.16 分块传输的总线移交

协议要求主机在接收到一个SPLIT或者RETRY响应后,

立刻执行一个空闲传输以允许总线转移给另外一个主机。

- 传输的地址在时间 T1 之后出现在总线上。在时钟沿 T2 和 T3 后从机返回两个周期的 SPLIT 响应;

- 在第一个响应周期的末尾,也就是 T3,主机能够检测到传输将会被分块因此(主机)改变接下来的传输控制信号以表示一个空闲传输;

- 同样也在时间 T3 处仲裁器采样响应信号并确定传输已经被分块。之后仲裁器可以调整仲裁优先权并且在接下来的周期改变授予信号,这样新的主机能够在时间 T4后被授予地址总线;

- 新主机可以保证立刻访问(总线),因为空闲传输总是在一个周期内完成。

三、 AMBA 3 AHB(AHB_Lite)

3.1 特性

AHB_Lite与AHB2对比,属于简化版。主要应用框架是单master多slave结构,因此没有仲裁器。

AHB_Lite协议有以下特性:

- Burst transfers(突发传输)

- Single clock-edge operation(单时钟沿操作)

- Non-tristate implementation(无三态)

- Wide data bus configurations,32,64,128,256,512,1024(数据总线配置,最大为1024bit)

- All transfer in a burst must be aligned to the address(基于地址对齐的突发传输)

- Pipeline transfer(流水线传输)

3.2 架构

&emsp AHB3协议可以实现单master多slave互连

在单master多slave架构下,多slave共用一个数据和地址总线,其中地址总线中,位宽包括Decoder位和真正的地址。如3个slave,则至少需要2bit片选位,即[31:30]是Decoder片选slave,[29:0]才是真正的地址(地址译码)。

3.3 接口

| Name | Destination | Description |

|---|---|---|

| HCLK | Clock Source | 总线时钟,所有的信号时序变化都在HCLK的上升沿触发. |

| HRESETn | Reset controller | 总线复位信号,低有效,复位更个系统和总线. 这是AHB-Lite信号中唯一的低有效信号. |

| HADDR[31:0] | Slave and decoder | 系统的32位地址总线 |

| HBURST[2:0] | Slave | Burst类型表示当前传输是否是single传输还是构成burst传输的一拍. 支持固定长度为4、8和16的burst.Burst可以是递增型或者是回卷型. 系统同样支持未定义长度的递增型burst.详细的和AHB2一样,可以查看上一章内容 |

| HMASTLOCK | Slave | 当为高电平时,表示当前传输是一个锁定序列的一部分. 它与地址总线和控制信号有着相同的时序. |

| HPROT[3:0] | Slave | 保护控制信号提供总线访问的额外信息,设置它的初衷是方便一些模块需要实现多种的级别的保护功能.保护控制信号,表示当前传输是否是一个操作码获取还是数据访问,还可以表示传输是否是一个特权模式访问还是用户模式访问. 对于带MMU功能的Master,保护信号也可以指示是否当前访问可以高速缓存(Cachable)或者Buffer缓存。和AHB2一样,可查看2.9小节 |

| HSIZE[2:0] | Slave | 表示传输的大小,典型值有字节、半字和字。 协议支持更大的传输大小,支持最大值为1024位 |

| HTRANS[1:0] | Slave | 指示当前传输的传输类型.。可以是: IDLE BUSY NONSEQUENTIAL SEQUENTIAL. |

| HWDATA[31:0] | Slave | 写数据总线 在总线写操作时从Master向Slave传输数据,建议最小的数据总线位宽为32位. 当然,位宽也可以扩展到支持更高带宽的操作. |

| HWRITE | Slave | 表示传输方向. 高电平表示写操作,低电平表示读操作。 它需要和地址总线同时有效,但在burst传输中必须保持不变。 |

| Name | Destination | Description |

|---|---|---|

| HRDATA[31:0] | 多路器 | 在读操作时,此信号从被选中的Slave向多路器传输数据.。多路器再将数据传输到Master.建议最小的数据总线位宽为32位.。当然,位宽也可以扩展到支持更高带宽的操作(宽度为32/64/128/256/512/1024) |

| HREADYOUT[2:0] | 多路器 | 当信号为高电平,表示总线上的传输结束了。 此信号可以通过驱动为低电平来增加传输的拍数 |

| HRESP | 多路器 | 传输的响应信号,在通过多路器后,给Master提供传输的状态信息。当信号为低电平,表示传输的状态正常。当信号为高电平,表示传输的状态错误。 |

- Decoder

| Name | Destination | Description |

|---|---|---|

| HSELx | Slave | 每个AHB-Lite Slave 拥有它自己的选择信号HSELx,并且这个信号指示了当前传输意图选择的Slave。当Slave被选中,它必须要监控HREADY信号的状态来确保在它响应当前传输之前的那个总线传输已经完成。HSELx信号是地址总线的组合逻辑译码。 |

- Multiplexor

| Name | Destination | Description |

|---|---|---|

| HRDATA[31:0] | Master | 读数据总线,由译码器输入的选择信号选出 |

| HREADY[2:0] | Master和Slave | 当信号为高电平,HREADY信号指示给Master和所有的Slave,前一个传输已经完成了 |

| HRESP | Master | 传输的响应信号,由译码器输入的选择信号选出 |

四、 AMBA 5 AHB(对比)

4.1 接口

4.2 特性

4.3 特点

4.4 传输响应

4.5 突发类型

4.6 传输类型

4.7 传输大小

4.8 保护类型

作者:xlinxdu

版权:本文版权归作者所有

转载:未经作者允许,禁止转载,转载必须保留此段声明,必须在文章中给出原文连接。