cpu设计和实现(iverilog工具)

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

编写verilog的工具不少。大家熟知的modelsim、quartus和vivado都可以用来编写的。前者主要是用来仿真,quartus主要用于altera芯片(现在属于intel),vivado则服务于xilinx芯片(现在属于amd)。如果不愿意破解,其实找到一款合适的工具还是蛮难的,而且简单、方便、好上手。好在开源工具有iverilog这样一款工具,windows、linux、mac都可以安装。暂时不想购买开发板的朋友,可以试试,至少入门是不成问题的。

代码链接地址,https://github.com/feixiaoxing/design_mips_cpu/tree/master/rtl/day01

1、安装地址

http://bleyer.org/icarus/iverilog-v11-20190809-x64_setup.exe

工具中本身包含了iverilog和gtkwave,前者负责编译,后者负责显示。

2、编译命令

C:\iverilog\bin\iverilog.exe -o tb tb.v cnt.v

C:\iverilog\bin\vvp.exe -n tb -lxt2

C:\iverilog\gtkwave\bin\gtkwave.exe hello.vcd命令主要是分成了三个部分。第一个命令iverilog主要是把所有的verilog文件编译在一起。第二个命令主要是仿真执行。第三个命令主要是把生成的hello.vcd文件显示出来。

3、cnt.v

这是一个计数的代码,主要是周期性输出一个trigger信号。

module count(rst, clk, out);

// input & output

input rst;

input clk;

output out;

// wire & reg

wire rst;

wire clk;

reg ce;

reg out;

// inner wire & reg

reg[5:0] cnt;

// clause defined

always @(posedge clk or posedge rst)

if(rst)

ce <= 1'b0;

else

ce <= 1'b1;

always @(posedge clk or posedge rst)

if (rst) begin

cnt <= 6'h00;

end else if (ce == 1'b1)begin

if (cnt == 6'd59)

cnt <= 6'h00;

else

cnt <= cnt + 1;

end

always @(posedge clk or posedge rst)

if(rst)

out <= 1'b0;

else if(out == 1'b1)

out <= 1'b0;

else if(cnt == 6'd59)

out <= 1'b1;

endmodule

整个代码是关于定时输出trigger信号的代码。首先,有一个ce信号,它在rst后的第一个时钟上升沿才变得有效。接着有了ce信号之后,cnt信号就可以开始自增了。自增的范围是0~59。等到cnt等于59的时候,就恢复为0。out就是触发信号,除了一开始复位为0的时候,其他时刻只有cnt==59的时候才会翻转为1,并且只翻转一次,马上又恢复为0。

4、tb.v测试代码

`timescale 1ns/1ps

module test();

reg rst;

reg clk;

wire data;

count tt(.rst(rst),

.clk(clk),

.out(data));

initial

begin

rst = 0;

clk = 0;

#12 rst = 1;

#21 rst = 0;

#1000 $finish;

end

initial

begin

while(1)

clk = #5 !clk;

end

initial

begin

$dumpfile("hello.vcd");

$dumpvars(0, test);

end

endmodule

tb.v其实就相当于单元测试。给被测试函数输入指定的信号,观察信号是否按照我们之前设定的设计运行。如果是,则皆大欢喜。否则,就要回过头来看一下,确认错误发生的位置,并及时修正。注意中间的hello.vcd文件,这就是生成的中间结果,最终的波形都要通过它显示出来。

另外,注意tb.v里面的信号类型和 cnt.v里面一般是反着来的。

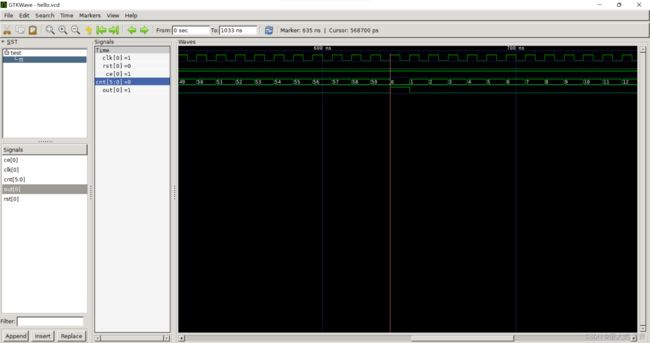

5、波形显示

hello.vcd文件直接用gtkwave显示就好,中间的波形可以自己选择,

这个工具虽然粗糙了一些,但是基本的功能都是在的。 左上是模块,左下是模块对应的信号。中间是需要查看的信号。右侧是观察到的数据,大家如果使用过逻辑分析仪,应该观察过对应的场景。信号的放大、缩小、拖拽、信号的显示格式,这些功能都是在的。用它来仿真,其实问题不大。