Vivado2018.2联合modelsim10.5仿真教程

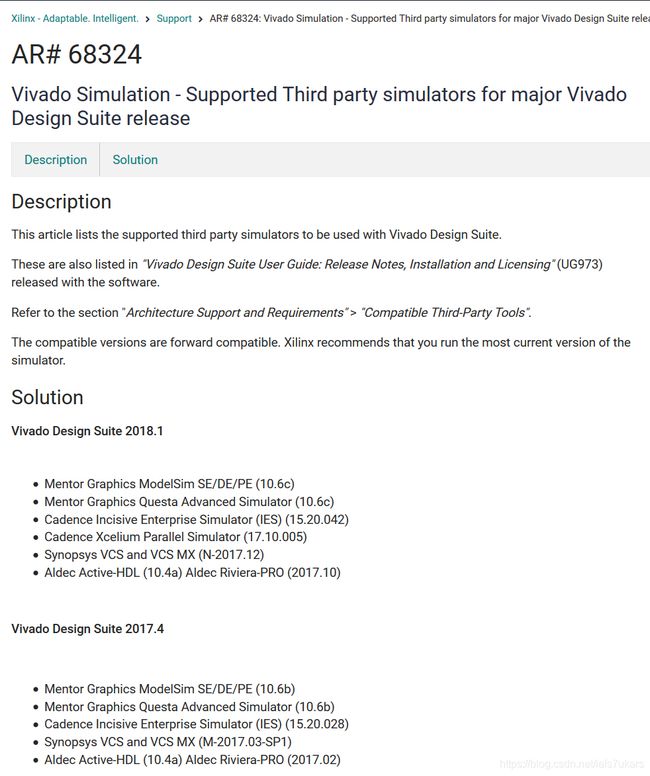

vivado可在xilinx官网查询匹配的modelsim最低版本,下载modelsim前记得选用合适的modelsim版本, 如图:

查询网址: https://www.xilinx.com/support/answers/68324.html

安装环境:win10 64位

软件版本:Vivado 2018.2 + Modelsimwin64SE_10.5

Vivado2018.2版本可以从xilinx官网下载获得,这里给出官网下载地址:https://www.xilinx.com/support/download.html

这里给出Vivado2018.1的百度云链接: https://pan.baidu.com/s/1cwGAFv5NUx3Lr0EUCqe7aA 提取码: apt4

modelsim10.5的链接见下。

安装Modelsim10.5及破解

安装文件链接及简介

相关安装文件链接: https://pan.baidu.com/s/1YQdcWvP83TENguquWKXU0g 提取码: ohi1

其中10.6c为pe版本的,试装了一下,可以进行安装和破解,但是Vivado没办法进行编译,具体原因不明,10.4c也进行了安装和破解,但是Vivado2018对其不支持,最低的版本貌似就是10.5了,所以本次教程使用10.5c进行安装和联合仿真。

各个版本之间的区别如下: ModelSim分几种不同的版本:SE、PE、LE和OEM,其中SE是最高级的版本。而集成在 Actel、Atmel、Altera、Xilinx以及Lattice等FPGA厂商设计工具中的均是其OEM版本。MODELSIM SE是主要版本号,也是功能最强大的版本,支持对Verilog和VHDL语言的混合仿真。除了主要版本外,Mentor公司还为各大FPGA厂商提供 OEM版本: XE是为Xilinx公司提供的OEM版,包括Xilinx公司的库文件;AE是为Altera公司提供的OEM版,包含Altera公司的库文件;在用特定公司的OEM版进行仿真时不需要编译该公司的库文件,但是仿真速度等性能指标都要落后于SE的版本。

SE版和OEM版在功能和性能方面有较大差别,比如对于大家都关心的仿真速度问题,以Xilinx公司提供的OEM版本ModelSim XE为例,对于代码少于40000行的设计,ModelSim SE 比ModelSim XE要快10倍;对于代码超过40000行的设计,ModelSim SE要比ModelSim XE快近40倍。

ModelSim SE支持PC、UNIX和LINUX混合平台;提供全面完善以及高性能的验证功能;全面支持业界广泛的标准;Mentor Graphics公司提供业界最好的技术支持与服务。

- ModelSim PE (Personal Edition) is the industry-leading, Windows-based simulator for VHDL, Verilog, or mixed-language simulation environments offering a very cost effective solution for RTL and gate level simulation.

- ModelSim DE (Deluxe Edition) includes full PE functionality plus PSL & System Verilog assertions, Code Coverage, Enhanced Dataflow, Waveform Compare, and support for Xilinx SecureIP as standard.

- ModelSim SE (System Edition) combines high performance and high capacity with the code coverage and debugging capabilities required to simulate larger blocks and systems and attain ASIC gate-level. ModelSim SE offers the ability to simulate very large designs.

安装破解

- 安装软件:注意:安装目录避免出现中文或空格(.可出现),安装过程一直点击 Yes 即可;

- 把 MentorKG.exe、mgls.dll以及patch64dll.bat 一起拷贝到modelsim安装目录的win32或win64下,例如【C:\modeltech6410.5\win64】;

- 进入安装目录下的win64 文件夹找到mgls.dll mgls64.dll两个文件,去掉只读属性;

- 运行patch64dll.bat,产生license后,放到任意目录下,例如【C:\modeltech6410.5\】;

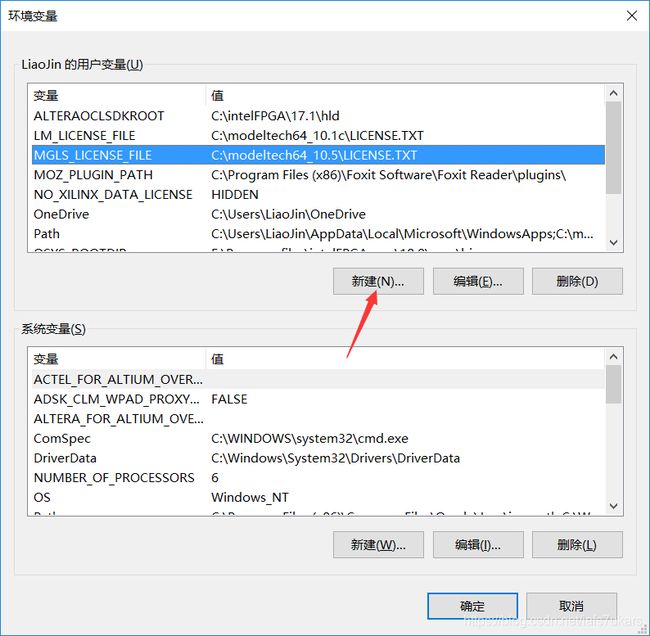

- 新建用户环境变量【MGLS_LICENSE_FILE】,变量值为license放置的目录,例如【C:\modeltech64_10.5\LICENSE.TXT】;

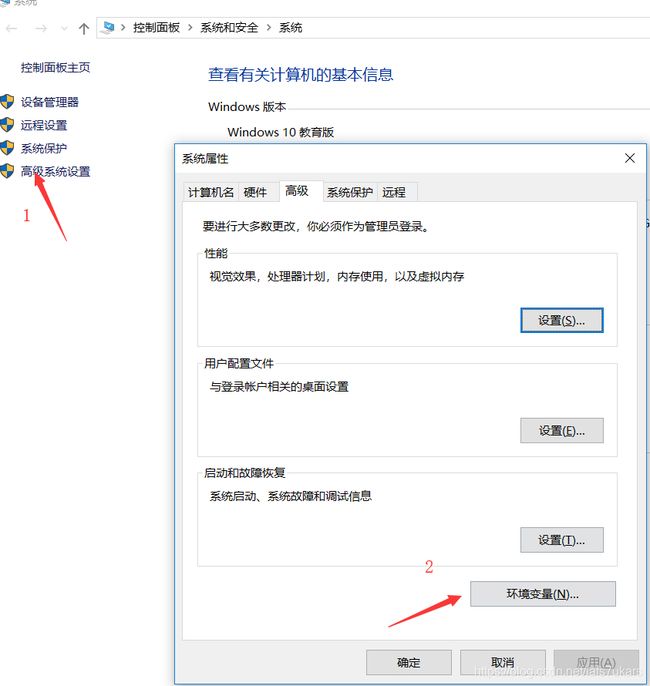

注:win10如何添加环境变量?

win10中,鼠标右键此电脑,选择属性,再选择高级系统设置,选择环境变量即可。

6. 安装破解结束,Over

Vivado2018.2和Modelsim10.5的联合仿真

(1)器件库编译

- modelsim安装路径中新建一个名为Vivado2018.2_lib的文件夹(路径和文件名可改)

- 接着选择vivado菜单“Tools”——>“Compile Simulation Libraries…”命令,如下图所示:

-

在弹出的对话框中设置器件库编译参数,仿真工具“Simulator”选择Modelsim Simulator,语言“Language”、库”Library“、器件家族”Family“均默认设置为All(当然也可以根据自己需求进行设置),然后在"Compiled library location"栏中设置编译器件库的路径,这里选前面新建的Vivado2018.2_lib文件夹,此外在"Simulator executable path"栏设置modelsim执行文件的路径,注意箭头部分不要勾选 ,如上图所示。

另:该部分也可用win10 tcl脚本实现,tcl命令如下:

例如:(1)仿真库编译到D:\Vivado2018.2_lib

(2)仿真工具使用Modelsim

(3)Modelsim安装在C:\modeltech64_10.5\win64

那么完整的tcl命令为:

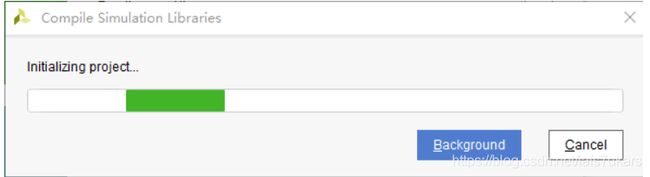

compile_simlib -directory D:\Vivado2018.2_lib -simulator modelsim -simulator_exec_path C:\modeltech64_10.5\win64设置好参数后点击“Compile”按钮开始器件库编译,下图所示为正在编译器件库的过程中,器件库编译结束后给出编译报告,这个过程应该是持续半个小时或者更长,依个人电脑性能而定。

编译报告可以从tcl console中得知,如下图所示,无Error(s)错误即可

打开modelsim安装路径下的vivado2018_lib文件夹,便可以看到已经产生了器件库,如下图所示:

生成如上图所示文件,要将modelsim设置为用户全局变量,那么下一次就不需要在此编译库了。步骤如下图所示,将变量名设置为MODELSIM,变量值为modelsim.ini的路径 。

(2)设置Modelsim(即第三方仿真工具)安装路径

Vivado菜单中选择“Tools”->“Setting…”,选择“Tool setting”->“3rd Party Simulators”选项卡,在“ModelSim”栏中输入或选择

modelsim工具的安装路径,如下图所示

(3)调用modelsim进行仿真

在vivado中关联了modelsim软件和编译器件库之后,就可以在vivado中调用modelsim软件对设计进行仿真了。不过,在对

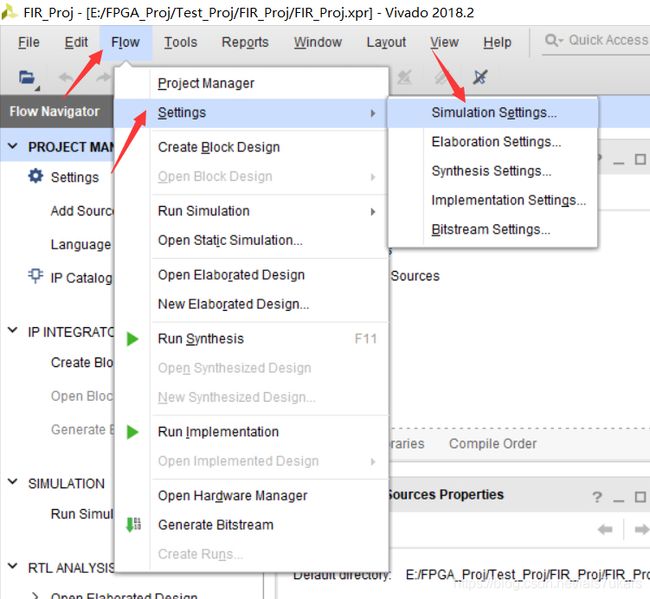

每一个新建的工程设计进行仿真时需要进行一些设置,选择vivado菜单“Flow”->“Simulation Settings…”命令或点击流程向

导中选择“Simulation Settings…”命令,分别如图所示。

在弹出的对话框中,设置仿真工具为modelsim、仿真语言为verilog或VHDL或混合,当设计中用到vivado中自带的仿真工

具时,还要指定器件库的路径,如下图所示

设置好仿真参数后,如果设计文件和仿真文件都已准备好,那么就可以开始对设计的功能进行仿真了,选择菜

单”Flow“->”Run Simulation“->"Run Behavioral Simulation"选择相应的仿真类型,或者电机流程向导中的”Run Simulation

“->选择相应的仿真类型进行仿真,如图所示

便会自动弹出modelsim,并显示波形

References

http://www.cnblogs.com/ninghechuan/p/8999078.html

https://blog.csdn.net/Pieces_thinking/article/details/83587695

hexo网站:jinliaosat.com

欢迎交流!