5G NR物理层各个步骤各项参数梳理记录

本文主要是对5G NR物理层知识的一个翻译和梳理,同时引用自己项目的各项参数作为一个例子,以供日后复习,也便于大家一起学习。

NR(5G)无线帧结构

- 5G子帧与LTE相比的独特特点:多种载波间隔类型,包括15,30,60,120,240,480,960 khz

- 帧结构层次:帧(无线帧)–> 子帧 --> 时隙 --> OFDM符号(与4G LTE相同)

- 一帧10ms包含10个子帧,一个子帧1ms包含8个slot(可能有变动),一个slot约0.125ms,包含14个OFDM符号(一般都是14个)。

- 1个RB内的子载波数:12(与LTE相同)

- 子载波间隔越大,时隙在时域中的长度越短

如果对NR(5G)无线帧结构有更进一步的学习需求,或者对其他候选帧结构有兴趣的,可阅读这里。

本文接下来的探讨学习基于此帧结构

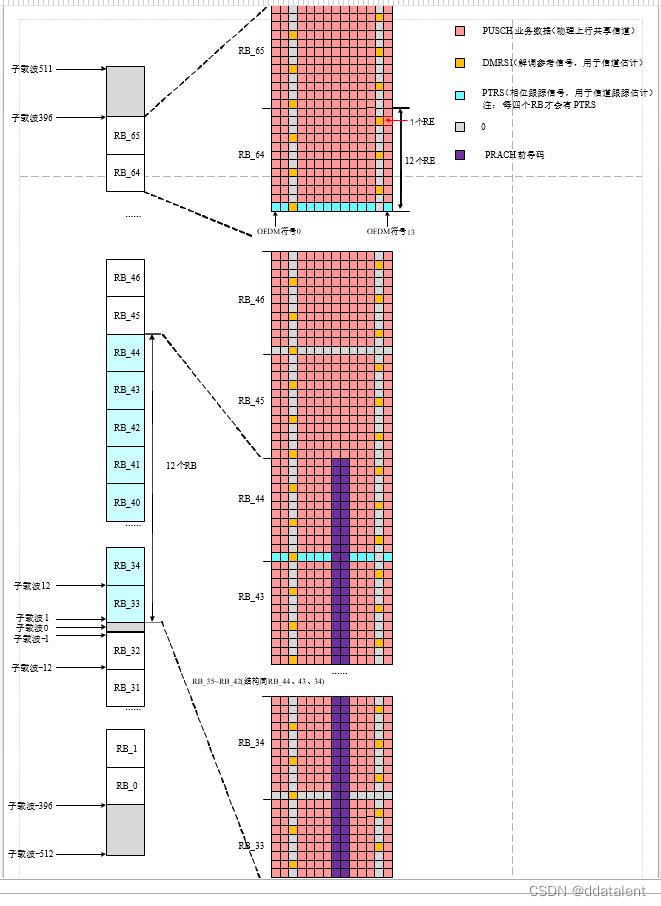

一帧10ms包含10个子帧,一个子帧1ms包含8个slot,一个slot约0.125ms,包含14个OFDM符号,每个OFDM符号都是1024点IFFT得到

每个OFDM符号有66个RB,每个RB有12个RE,子载波间隔120kHz。(100M带宽下,最多66个RB)。

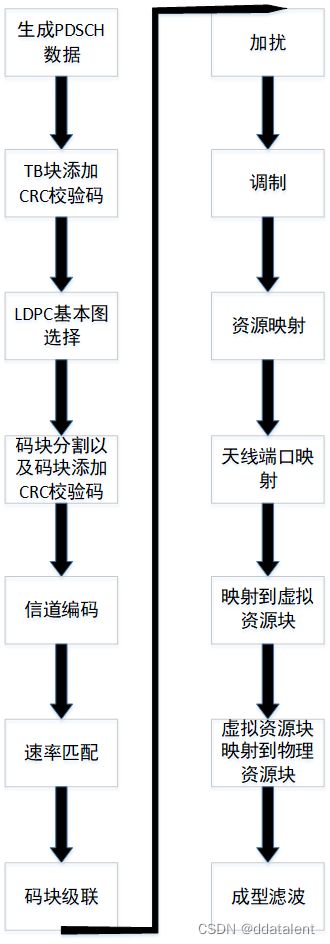

物理层流程简介

1.确定TBS(TB Size),生成TB块

【5G NR 物理层 流程一】PDSCH/PUSCH 如何根据帧结构生成TB块

根据帧结构,我们最终生成的传输块大小为 T B S s i z e = 49176 TBS_{size}=49176 TBSsize=49176bit。

此外,确定采用64QAM调制,码率R = 0.92578125

2.TB块添加CRC校验码

CRC校验的原理可以看我之前整理的这篇文章:CRC冗余校验的原理和FPGA实现思路

待添加的传输块比特表示为 a 0 , a 1 , . . . a A − 1 a_0,a_1,...a_{A-1} a0,a1,...aA−1,其中 A = 49176 A=49176 A=49176。

若是 A > 3824 A>3824 A>3824,则添加24位校验位,若是 A ≤ 3824 A≤3824 A≤3824,则添加16位校验位。

采用如下生成多项式,对传输块添加长度为 L = 24 L=24 L=24的CRC校验码。

g C R C 24 A ( D ) = [ D 24 + D 23 + D 18 + D 17 + D 14 + D 11 + D 10 + D 7 + D 6 + D 5 + D 4 + D 3 + D + 1 ] g_{CRC24A}(D)=[D^{24}+D^{23}+D^{18}+D^{17}+D^{14}+D^{11}+D^{10}+D^{7}+D^{6}+D^{5}+D^{4}+D^{3}+D+1] gCRC24A(D)=[D24+D23+D18+D17+D14+D11+D10+D7+D6+D5+D4+D3+D+1]

添加了CRC后的序列表示为 b 0 , b 1 , . . . b B − 1 b_0,b_1,...b_{B-1} b0,b1,...bB−1,其中 B = A + L = 49200 B=A+L=49200 B=A+L=49200。

3.LDPC基本图选择

关于LDPC参数的选择可以看我整理的这篇文章:关于LDPC编译码参数如何选择确定

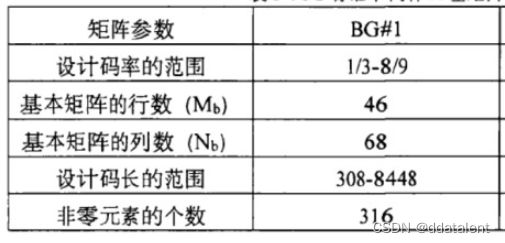

已知本项目的传输块大小 B = 49200 B=49200 B=49200,码率R = 0.92578125,因此此处选择BG1。BG1的要求的码长在308-8448之间。

4.码块分段及添加码块CRC

由于采用LDPC编码,故需要对待编码数据进行码块分段。同时对每个码块进行添加CRC操作。

已知CRC长度为 L = 24 L=24 L=24以及码块最大长度为 K c b = 8448 K_{cb}=8448 Kcb=8448 。可以得到分段后的码块个数为 C = [ B K c b − L ] C = [\frac{B}{K_{cb}-L}] C=[Kcb−LB] ("[]"表示向上取整)。由此可以得到 C = 6 C=6 C=6。即需要把长度 B = 49200 B=49200 B=49200的传输块分割成6块,每块分别添加CRC。

即 K ′ = B / C + L = 8224 K^{'}=B/C + L = 8224 K′=B/C+L=8224。但是这个不是最终的码块大小,8224这个大小并没有符合其大小的LDPC生成矩阵,因此要在此基础上寻找最接近,并且可以LDPC编码的码块大小。

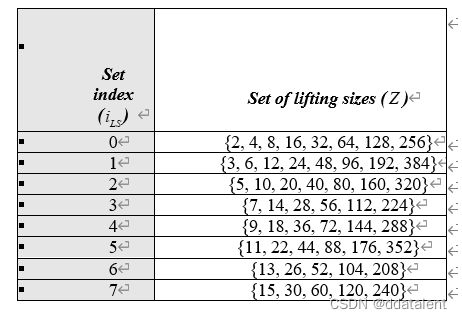

最终码块大小 K = 22 Z c K=22Z_c K=22Zc,而 22 Z c ≥ K ′ = 8224 22Z_c≥K^{'}=8224 22Zc≥K′=8224,从下图中找到满足条件的最小的 Z c = 384 Z_c=384 Zc=384,则最终码块大小 K = 22 Z c = 22 ∗ 384 = 8448 K=22Z_c=22*384=8448 K=22Zc=22∗384=8448,

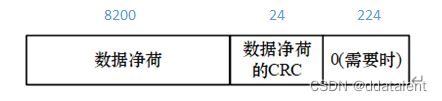

已知目前每一个码块包含 B / C = 8200 B/C =8200 B/C=8200个数据, L = 24 L=24 L=24个校验位,距离8448还差224位。因此在数据最后补充224个比特的0。

最终可以得到码块分段后:每个码块内包含8200比特的数据净荷+24比特CRC+224个比特0。共6块这样的码块。

5.信道编码(LDPC编码及打孔)

LDPC编码原理可以看我之前整理的这篇文章:LDPC码的编译码原理简述

关于LDPC参数的选择可以看我整理的这篇文章:关于LDPC编译码参数如何选择确定

在第三小节中已经确定,本项目选用BG1。

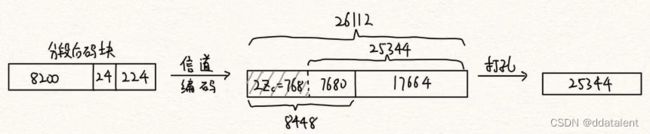

则对于每个长度为8448的码块,LDCP编码的结果为 N b ∗ Z c = 68 ∗ 384 = 26112 N_b*Z_c=68*384=26112 Nb∗Zc=68∗384=26112长度的输出。根据规定,需要将前 2 Z c 2Z_c 2Zc个信息比特打孔,得到编码输出 26112 − 2 Z c = 25344 26112-2Z_c=25344 26112−2Zc=25344。

6.速率匹配

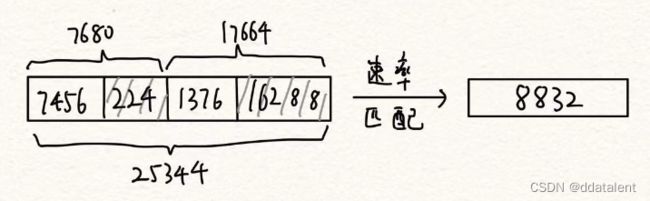

速率匹配的目的是调整信道编码器(LDPC)的输出数据速率,以匹配在PDSCH的时间-频率网格中分配用于传输的可用资源。根据帧结构,或者第一节中的描述,一个slot中所有可用的RE资源块数量为8832个。速率匹配就是要从25344个中留下8832个,将多余的低密度奇偶校验位删去。

LDPC编码后的输出是26112个,可以分为两部分,前面8448个和后面17664个。

前8448个又可以分为8200+24+224三部分。从8200中打孔丢掉768个,224个是LDPC编码前为了凑长度补的0,也可以删去。因此第一部分还剩下7456个,距离8832个还差1376个。

于是从第二部分的低密度奇偶校验位中留下1376个,多余的16288个删掉,即可凑满8832个。

于是我们可以得到六块速率匹配后的码块,每段码块都有8832bit。

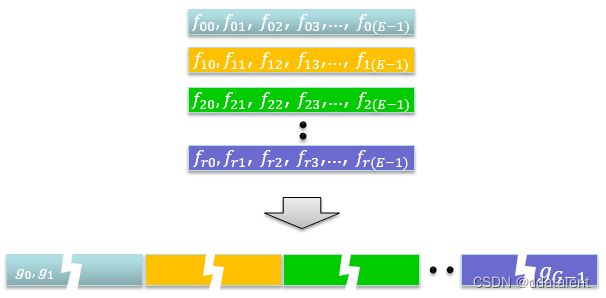

7.码块级联

这是将速率匹配后的多个代码块结合到单个数据流进行传输的步骤。

很简单,就是先放第一个码块,然后第二个码块连在后面,一直连接到第六个码块。

8.加扰

加扰过程是将随机性引入传输数据的步骤,以确保均匀的功率分配、干扰管理、数据隐私和准确的信道估计。加扰和解扰操作分别在发送器和接收器上执行,使用相同的加扰序列。加扰通过将伪随机二进制序列 (PRBS) 应用于数据流来为传输的数据引入随机性。此操作可确保传输的信号在不同的频率和时间资源上具有均匀的功率分布。加扰还有助于减轻小区间干扰、提高数据隐私并允许接收器 (UE) 执行准确的信道估计。

加扰的步骤主要是按位异或:加扰过程涉及输入数据流(由码块级联步骤产生)和加扰序列之间的按位异或 (XOR) 运算。这个操作的输出是一个加扰的数据流。

b ~ ( i ) = b ( i ) ⊕ c ( i ) = ( b ( i ) + c ( i ) ) m o d 2 , i = 0 , 1 , . . . M b i t − 1 \tilde{b}(i) = b(i) ⊕ c(i) = (b(i) + c(i) ) mod 2,i=0,1,...M_{bit}-1 b~(i)=b(i)⊕c(i)=(b(i)+c(i))mod2,i=0,1,...Mbit−1

其中 b ( i ) b(i) b(i)表示码块级联后的数据, M b i t = 8832 ∗ 6 = 52992 M_{bit}=8832*6=52992 Mbit=8832∗6=52992, c ( i ) c(i) c(i)表示扰码, b ~ ( i ) \tilde{b}(i) b~(i)表示加扰后的数据。

加扰不会改变数据速率,因为它只是通过引入随机性来修改数据流。