【电子技术综合设计】数字钟(包含计数模块、12/24进制切换模块以及闹钟模块)

工程文件:

https://pan.baidu.com/s/1PnYd2mwMUf0tgxczdcl2MA

提取码: ihrk

B站演示:

【电子技术综合设计】数字电子时钟(包含计数模块、12/24进制切换模块以及闹钟模块)_哔哩哔哩_bilibili

一、设计要求

1. 24小时制的时、分、秒计时;

2. 手动调时功能;

3. 闹钟功能;

4. 12/24小时制转换;

5. 星期显示。

二、总体框架设计

1. 设计60进制加法计数器,作为秒钟和分钟;

2. 设计24进制加法计数器,作为时钟;

3. 设计调时电路;

4. 设计7进制加法计数器,作为星期;

5. 组成7x24小时时钟模块;

6. 设计比较电路,作为闹钟模块;

7. 设计12进制(1-12)计数器;

8. 组合成数字钟。

三、设计步骤

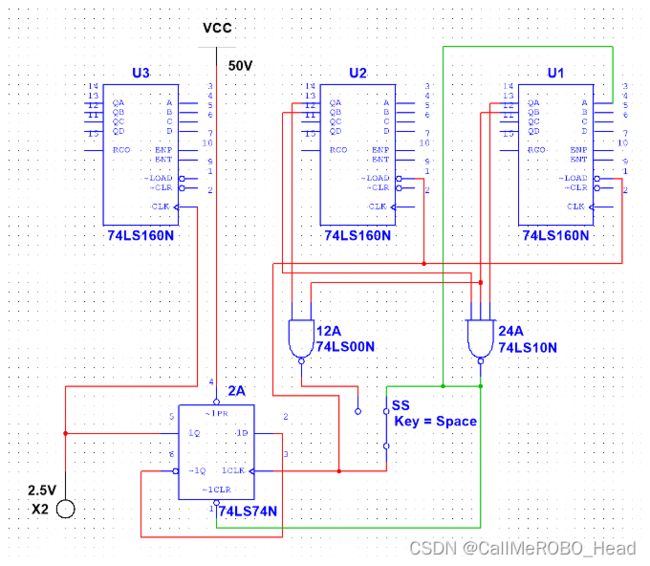

1. 设计12(1-12)/24(0-23)小时计时切换模块

采用置数法,使用2片74LS160N芯片,1片74LS00N芯片,1片74LS10N芯片,1片74LS74N芯片,实现12/24进制可切换加法计数器, 作为时钟显示电路:

(1)对于12进制,当计数到0001-0010(即12)时,置数回0000-0001(即1),故与非门12A接法如 图1 所示。

图1

与非门12A输入端接个位片U1输出端QB,十位片U2输出端QA。

当启用12进制并计满12位时,与非门12A输出信号为0,否则为1。

(2)对于24进制,当计数到0010-0011(即23)时,置数回0000-0000(即0),故三输入与非门24A接法如 图2 所示。

图2

三输入与非门24A输入端接个位片U1输出端QB、QA,十位片U2输出端QB。

当启用24进制并计满24位时,三输入与非门24A输出信号为0,否则为1。

(3)综上,两加法器的输入端接法如 图3 所示。

图3

个位片U1输入端B、C、D接地,输入端A接三输入与非门24A输出信号;十位片U2输入端均接地。

(4)为实现在12或24进制时都能置数的功能,引入单刀双掷开关SS,其接法如 图4 所示;

图4

单刀双掷开关SS输入端接入两个与非门的输出信号,输出端接入个位片U1与十位片U2的置数端LOAD’。

当启动12(24)进制并计满12(24)位时,单刀双掷开关SS输出信号为0,个位片U1与十位片U2同时进行置数。

(5)考虑到现实中若以12进制记录时间,则需要进行两次循环才能使星期显示进1位,故采用一个D触发器实现1位二进制计数器,其接法如 图5 所示。

图5

① 脉冲端CLK接单刀双掷开关SS输出端;

② 输入端D = 输出端Q’;

③ 输出端Q接次级加法器U3的脉冲端CLK作进位信号;

④ 控制端PR’接高电平,复位端CLR’接三输入与非门B的输出信号。

启用12进制时,PR=CLR=1,12位数计满两次才输出一次进位信号;启用24进制时,PR=1,CLR=0,只需计满一次即可输出进位信号;

(6)12/24小时计时切换模块的完整电路如 图6 所示。

图6

当启动12进制时,十位-个位从0001-0010跳变到0001-0011的一瞬间,个位片与十位片同时进行置数,回到0000-0001,完成12进制(1-12)计数;

当启用24进制时,十位-个位从0010-0011跳变到0001-0100的一瞬间,个位片与十位片同时进行置数,回到0000-0000,完成24进制(0-23)计数。

2. 设计7 x 12/24小时制时钟计时电路模块

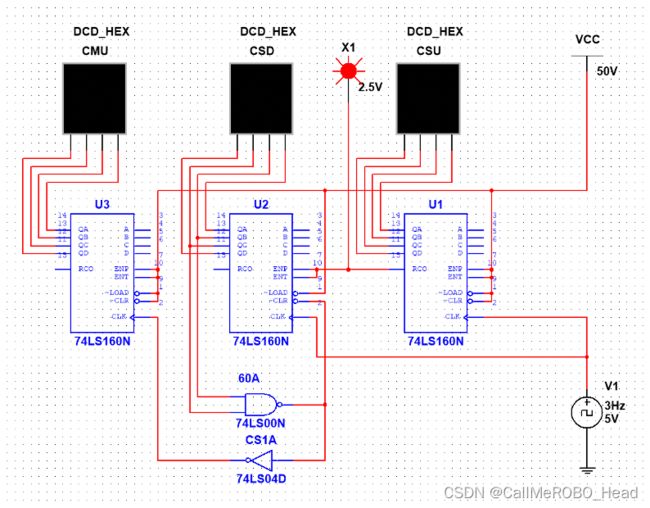

(1)使用2片74LS160N芯片,1片74LS00N芯片,设计60进制加法计数电路,作为秒钟显示电路:

① 秒钟个位片U1的进位端RCO接到秒钟十位片U2的使能端ENP和ENT充当进位允许信号,其接法如 图7 所示。

图7

当个位片计满一个循环后,十位片进一位;

② 实现60进制要对十位片采用清零法。U2输出端QC、QB通过与非门60A后,接回U2清零端CLR’作清零信号,其接法如 图8 所示。

图8

当计满60位时,与非门60A输出信号为0,秒钟十位片U2进行清零,秒钟个位片U1也刚好为0;

③ 非门CS1A输入端接与非门60A输出端,其输出端接入下一级分钟个位片U3的进位端CLK作进位信号,其接法如 图9 所示。

图9

当计满60位数时,本级清零,次级进一位;

④ 秒钟完整电路图如 图10 所示。

图10

当十位-个位从0101-1001跳变到0110-0000的一瞬间,个位片与十位片同时回到0000,完成60进制(0-59)计数;

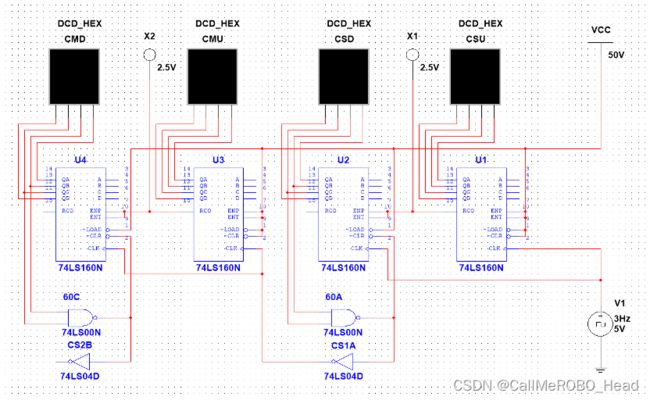

(2)使用2片74LS160N芯片,共用同一片74LS00N芯片,设计60进制加法计数电路,作为分钟显示电路,其接法如 图11 所示:

思路同上,其中分钟十位片输出端Q2Q1通过与非门60C;

图11

(3)以12/24小时计时切换模块为基础,使用1片74LS10N芯片,设计7进制(1-7)加法计数电路,作为星期显示电路:

7进制采用置数法。星期片U3输入端D0接高电平;输出端Q2Q1Q0接三输入与非门7A后,接入置数端LORD’作置数信号。当输出端Q3Q2Q1Q0从0111跳变到1000的一瞬间,芯片进行置数,重新回到0001,完成7进制(1-7)计数。

图12

(4)连接12/24进制切换模块:

分钟十位片U4输出端Q2Q1通过与非门C后,接入时钟个位片的进位端CLK作进位信号,其接法如 图13 所示。

注意:此时星期片、时钟十位片、时钟个位片分别为U7、U6、U5。

图13

当计满60位数时,本级清零,次级进一位;

问:为什么进位信号需要经过一个非门再接入次位的个位片?

答:因为74LS160为上升沿触发。当十位片不为0110(即6)时,与非门60A的输出信号为1,此时若不经过非门而直接接入次位的个位片,会使其直接进一位,这就是为什么当电路刚接通时时钟个位片和分钟个位片会显示为1的原因。

解决办法就是加上一个非门,这样就能保证次位的个位片能正确进位。

(5)设计时钟/分钟调时电路:

① 使用开关CS,用于控制秒钟电路;

② 使用单刀双掷开关MTS/CTS,其输入端一端接与非门的输出信号,另一端接脉冲信号,当切换为脉冲端时用作时钟/分钟的调时;

③ 使用单刀双掷开关WTS,用作星期的调整。

完整接法如 图14 所示;

图14

3. 设计闹钟模块

使用5片74LS85N芯片和蜂鸣器,设计时钟和分钟的比较电路:

(1)比较电路采用并联扩展法。5片芯片的比较输入端I(A=B)均接高电平,其余两个均接地,如 图15 所示;

图15

(2)4片时钟/分钟比较芯片从最低位(分钟个位)起步比较,其输出端F(A>B)、F(A 图16 (3)芯片输入端接入比较信号,用四通道开关(J1-J4)设置,以达到手动设置时间的功能,接法如 图17 所示; 图17 (4)蜂鸣器一端接入并联扩展芯片的输出端F(A=B),另一端接地;开关ACS用于控制输出信号的接收。具体接法如 图18 所示。 图18 当A3A2A1A0=B3B2B1B0时,并联扩展芯片输出端F(A=B)=1,蜂鸣器响起,直到时间变动或手动断开开关ACS才停止发出响声,以此实现闹钟功能。 (5)闹钟模块的完整电路如 图19 所示。 图19 4. 拼接各模块,组成具有闹钟功能和调时功能的12/24小时制数字钟 连接7 x 12/24小时制时钟计时电路模块与闹钟模块,将闹钟模块中4片比较芯片的输入端分别接入相对应的输出端(分钟个位对分钟个位,分钟十位对分钟十位,以此类推……),并进行线材整理,即完成了具备闹钟功能和调时功能的12/24进制数字钟。 图20 六、运行结果 1. 从7/23/58/00开始计数,此时闹钟指示灯熄灭; 2. 计到7/23/59/xx,此时等同闹钟时间,闹钟指示灯亮起,蜂鸣器发出响声; 3. 计满一个循环后,计数回到初始状态1/00/00/00,此时闹钟指示灯熄灭。