STM32F407重要外设学习(基于《野火STM32库开发实战指南》)——02RCC-使用HSE/HSI配置时钟

本文档为记录自己以STM32407为媒介学习关于Cortex-M4内核及其重要外设应用的学习记录

目录

前言

一、RCC主要作用(时钟部分)

二、时钟树

1.主要时钟

2.其他时钟

3.配置系统时钟流程

总结

前言

RCC-Reset Clock Control 复位和时钟控制器

一、RCC主要作用(时钟部分)

注意:

HCLK=SYSCLK=PLLCLK=168M,PCLK1=HCLK/2=84M,PCLK1=HCLK/4=42M。

以上是stm32f4库函数的标准配置,一般默认使用这个。

二、时钟树

以库函数函数SetSysClock() 的编写流程来讲解时钟树,这个函数也是我们用库的时候默认的系统时钟设置函数。该函数的功能是利用 HSE 把时钟设置为: HCLK = SYSCLK=PLLCLK = 168M, PCLK1=HCLK/2 = 84M,PCLK1=HCLK/4 = 42M。即图中黄色部分。

1.主要时钟

(1)HSE高速外部时钟信号

① 接外部晶振,频率4M~26MHz。

- 使用有源晶振时,时钟从OSC_IN引脚进入,OSC_OUT引脚悬空;

- 使用无源晶振时,时钟从OSC_IN和OSC_OUT进入,并且需要配谐振电容。

② STM32F4开发板使用25M无源晶振,使用HSE或HSE经PLL倍频之后的时钟作为系统时钟SYSCLK

- HSE发生故障时,HSE和PLL都会关闭,系统时钟由高速内部时钟时钟信号HSI接替,知道HSE恢复正常。

(2)锁相环PLL

① 锁相环时钟:PLLCLK;

② 来源:HSI、HSE。由PLLCLK位配置。

- HSE或HSI先经过一个分频因子M进行分频,然后再经过一个倍频因子N,再经过一个分频因子P,最后成为锁相环时钟。

- STM32F4中,PLLCLK = (HSE/M)*N/P = 25/25-336/2 = 168M;

③ 控制:RCC_PLLCFGR——RCC PLL配置寄存器

④ PLL48CK:为USB_FS、RANG、SDIO提供时钟;

(3)系统时钟(SYSCLK,最高为168M)

①来源:HSI、HSE、PLLCLK;

②控制:RCC_CFGR时钟配置寄存器的SW位。

(4)HCLK时钟

① HCLK作用: AHB(advanced high-performance bus)高速总线时钟,最高为168M。为AHB总线的外设提供时钟、为Cortex系统定时器提供时钟(SysTick)、为内核提供时钟(FCLK);

②来源:系统时钟分频得到;

③控制: RCC_CFGR 时钟配置寄存器的HPRE位。

(5)PCLK1时钟

① PCLK1作用:APB1低速总线时钟,最高为42M, 为APB1总线的外设提供时钟;

② 来源:HCLK分频得到,通常配置为4分频;

③ 控制: RCC_CFGR 时钟配置寄存器的PPRE1位。

(6)PCLK2时钟

① PCLK2作用:APB高速总线时钟,最高为84M, 为APB2总线的外设提供时钟;

② 来源:HCLK分频得到,通常配置为2分频;

③ 控制: RCC_CFGR 时钟配置寄存器的PPRE2位。

2.其他时钟

(1)RTC时钟

① RTC作用:为芯片内部的RTC提供时钟;

② 来源:HSE_RTC(HSE分频得到)、LSE(外部32.768KHZ的晶体提供)、LSI(32KHZ);

③ 控制:RCC备份域控制寄存器RCC_BDCR:RTCSEL位控制。

(2)独立看门狗时钟:IWDGCLK,由LSI提供;

(3)I2S时钟:由外部的引脚I2S_CKIN或者PLLI2SCLK提供;

(4)以太网PHY时钟:407没有集成PHY,只能外接PHY芯片,比如LAN8720,那PHY时钟就由外部的PHY芯片提供,大小为50M;

(5)USB PHY时钟:407的USB没有集成PHY,要想实现USB高速传输,只能外接PHY芯片,比如USB33000。那USB PHY时钟就由外部的PHY芯片提供;

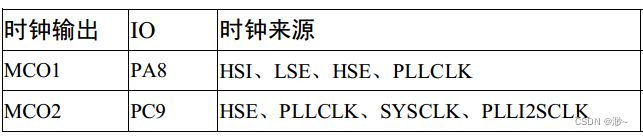

(6)MCO时钟输出

① 把控制器的时钟通过外部的引脚输出,可以外外部的设备提供时钟。MCO1为PA8,MCO2为PC9;

② 控制: RCC_CFGR 时钟配置寄存器的MCOX的PREx位;

3.配置系统时钟流程

(1)使用HSE/HSI时,配置系统时钟的步骤:

① 开启 HSE/HSI ,并等待 HSE/HSI 稳定;

② 设置 AHB、 APB2、 APB1 的预分频因子;

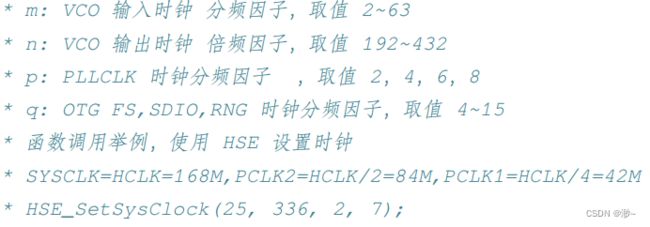

③ 设置 PLL 的时钟来源:

- 设置 VCO 输入时钟分频因子 PLL_M,

- 设置 VCO 输出时钟倍频因子PLL_N,

- 设置 PLLCLK 时钟分频因子PLL_P,

- 设置 OTG FS,SDIO,RNG 时钟分频因子 PLL_Q;

④ 开启 PLL,并等待 PLL 稳定;

⑤ 把 PLLCK 切换为系统时钟 SYSCLK;

⑥ 读取时钟切换状态位,确保 PLLCLK 被选为系统时钟

(2)正点原子STM32F4文件system_stm32f4xx.c中,系统时钟的配置(使用HSE,外部晶振频率25MHz)

总结

① 若使用STM32系列的芯片,外部晶振的配置如果是其他频率的,设置频率可以在上述文件中修改对应的因数。

② 若使用其他厂商的芯片,需要配置系统时钟时,可以先根据芯片手册的时钟树确定有哪些地方需要配置的,其次可以参照上述的流程进行系统时钟配置。