PCIe 均衡技术介绍(概要)

目录

1. PCIe 均衡技术介绍(概要)

1.1 信号均衡概念及意义

1.2 信号补偿技术

1.3 均衡系数协商

1.3.1 Phase 0

1.3.2 Phase 1

1.3.3 Phase 2

1.3.4 Phase 3

2. PCIe 均衡技术介绍(电气物理篇)

3. PCIe 均衡技术介绍(逻辑物理篇)

参考

除了本篇转载的博客外另有一篇讲解PCIE均衡的文章

PCIe5.0均衡简介(整理版)_pcie 均衡_wqh_硬件菜鸟的博客-CSDN博客

该篇转载出自阿里云开发者社区的MangoPapa作品,MangoPapa博客是主要是PCIE和UCIe系列文章。博客地址已在本人另一篇博客推荐的文章中收藏

1. PCIe 均衡技术介绍(概要)

1.1 信号均衡概念及意义

信号从发送端发出,经信道传输,到达接收端。在传输过程中,信号会发生失真,影响接收端对信号的正确判决。影响接收端接收信号质量的因素很多,比如传输速率,电磁干扰,信道质量等等。信号失真越严重,误码率 BER 越高,从而影响通信性能。

为了在接收端获取到易于判决的优质信号,可以在发送端、传输链路途中或者接收端信号判决之前对信号进行调理改善,从而减小信号失真对通信性能的影响。这种对信号的调理,称作信号补偿,或称均衡。

图 1 是不采用均衡与采用均衡接收端接收信号对比图,可见,采用均衡后,信号质量得到了较大改善,更容易接收端做出正确判决。

▲ 图 1: 接收端接收信号无均衡 vs. 有均衡

1.2 信号补偿技术

随着传输速率的提升,信号传输过程中趋肤效应及介质损耗越来越严重。为了在接收端正确恢复出发送的信号,需要对信号进行补偿。

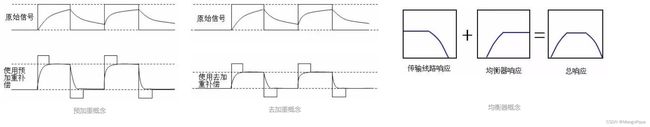

PCIe 信号补偿三大技术:发送端预加重(Pre-emphasis)、去加重(De-emphasis)和接收端均衡(Equalization)。预加重、去加重也被称为发送端均衡。各技术基本原理如图 2 所示。

▲ 图 2: 预加重、去加重、接收端均衡原理

无源传输线路像是一个低通滤波器,PCIe 高速串行信号经信道从发送端传输到接收端后,其高频分量比低频分量衰减要大,而高频分量主要集中在信号的上升沿及下降沿。为了补偿这种高频衰减,在信号发送的时候,有意增强信号跳变沿的信号幅度,增高高频分量,即信号预加重;相比于预加重的方案,去加重则是降低跳变沿之外的信号幅度,削弱低频分量,同样能够达到目的。

接收端均衡器相当于高通滤波器,来补偿失真的波形。

1.3 均衡系数协商

2.5 GT/s 及 5 GT/s 时,只在发送端进行固定参数的去加重均衡,无需进行均衡参数协商。传输速率上升至 8 GT/s 及以上后,收发端均衡更加复杂,收发端之间需要协商均衡系数,以获得最佳传输性能。收发端在链路训练的 Recovery.Equalization 状态进行均衡系数协商。整个 EQ 过程包括 4 个过程,称作 4 个 Phase。当速率为 8 GT/s 及以上时,EQ Phase 信息存放在了 TS1 的 EC 字段(Symbol 6,bit 0~1)。

1.3.1 Phase 0

Phase 0 发生于协商下一 EQ 速率但未进入下一速率之前。Phase 0 期间 USP 回传 Preset 及 Coefficients 给 DSP。DSP 没有 Phase 0。

1.3.2 Phase 1

PCIe 双方在 Phase 1 阶段通过互发 TS1 交换LF (Low Frequency,symbol7)、FS (Full Swing,Symbol 8) 、Post-cursor (Symbol 9) 进行均衡器的粗调,以获得 BER≤10-4的误码性能。

DSP 给 USP 发送 EC=10b 的 TS1 来发起到 Phase 2 的跳转。

1.3.3 Phase 2

Phase 2 时,USP 作为 Master,调节 DSP 的 Tx 系数,具体可分为 Preset 调节及 Coefficient 调节。USP 在每条 Lane 上独立调整 DSP 的 Tx 设置及其自身(USP)的 Rx 设置,以确保 USP 能接收到符合要求的比特流(比如每条有效 Lane 上获得 BER≤10-12 的误码率)。

DSP 建议其 Tx 系数及其使用的 Preset 值,在 Phase 1 阶段仅采用 Preset,在 Phase 2 采用 Preset 及 Tx 系数。USP 收到 TS1 后有可能会请求一组不同的系数或 Preset 设置,然后进行进一步评估,直到得到最优的设置。

USP 完成 Phase 2 后,给 DSP 发送 EC=11b 的 TS1 进入 Phase 3。

1.3.4 Phase 3

Phase 3 时,DSP 作为 Master,调节 USP 的 Tx 系数。DSP 在每条 Lane 上独立调整 USP 的 Tx 设置及其自身(DSP)的 Rx 设置,调整方式与 Phase 2 相似。DSP 发送 EC=00b 的 TS1 来标志 Phase 3 及 EQ 的结束。

以上四个 Phase 中,Phase0/1 采用 Preset 粗调,Phase2/3 精调。如果粗调阶段就达到了信号质量需求,也可以不进行精调。

除非有特别配置,8 GT/s 以上速率时必须进行 EQ,至少在最高速率上要进行 EQ,中间速率可以跳过 EQ。当然仿真的时候可以设置 bypass_eq,或者设置 bypass_eq_to_highest_rate,仅在最高速率时进行 EQ。比如最高支持 32 GT/s,那么在 8 GT/s,16 GT/s 的时候可以跳过 EQ。从 32GT/s 降速时,需要重新进行链路训练并做 EQ。

注意:Phase 2 及 Phase 3 中,DSP/USP 到底是谁作为 Master 调节谁的 Tx ?有些文章解读跟本文相反,读者请查看 PCIe 官方 Spec,来判断谁对谁错。

2. PCIe 均衡技术介绍(电气物理篇)

链接:PCIe 均衡技术介绍(电气物理篇)

3. PCIe 均衡技术介绍(逻辑物理篇)

链接: PCIe 均衡技术介绍(逻辑物理篇)

参考

- PCI ExPress Base Spec 5.0, Chapter 4.2.3, Chapter 4.2.6.4.2, Chapter 8.3.3, …

- PCIe Express Technology, Mindshare Inc, Chapter 13

- SNPS PHY databook,chapter 5.11

- 芯片中的数学——均衡器EQ和它在高速外部总线中的应用

- pcie equalization学习笔记

- PCIE 3.0中使用的动态均衡概念

- 理论篇|如何实现PCIe Gen3/Gen4接收端链路均衡测试?

- 实践篇|如何实现PCIe Gen3/Gen4接收端链路均衡测试?)

- PCIe Electrical PHY(2)-SerDes中的均衡技术