FPGA可重配置原理及实现(1)——导论

一、概述

可重配置技术是Xilinx提供的用来高效利用FPGA设计资源实现FPGA资源可重复利用的最新的FPGA设计技术,这种技术的发展为FPGA应用提供了更加广阔的前景。

术语“重构”是指FPGA已经配置后的重新编程。FPGA的重构有两种类型:完全的和部分的。完全重构将整个FPGA重新编程,而部分重构只取代设计的一部分,设计的剩下部分仍正常工作。部分重构不被视为完全重构的特殊情况,因为两者基本相同。对FPGA执行部分重构通过使用与完全重构(JTAG、CAP或SelectMAP接口)相同的方法来进行,如上一节所述。比特流的结构对于完全和部分重构来说都是相同的。

二、可重配置导论

1、可重配置的概念

当系统变得越来越复杂的时候,设计者需要用尽可能少的成本来做更多的事情,FPGA的灵活性成为了一个关键的“财富”。为什么这么说?因为xilinx的FPGA总是提供现场设备可重编程的灵活性。当今,越来越苛刻的成本、电路板的空间和功耗限制要求更高效的设计策略。

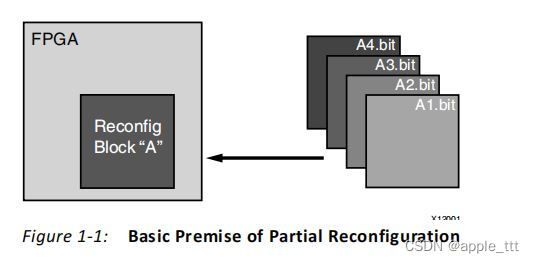

FPGA技术提供了现场编程和重新编程的灵活性,而无需经过修改设计的重新制作。部分可重构(PR)进一步提高了这种灵活性,允许通过加载部分配置文件,通常是部分BIT文件来修改一个操作中的FPGA设计。下图是部分可重构的结构图:

如图所示,通过将A1.bit、A2.bit、A3.bit和A4.bit中的任意一个部分可重配置文件下载到可重配置块“A”中,就可以实现可重配置块“A”的功能。

FPGA设计中的逻辑分为两种不同的类型,可重构逻辑和静态逻辑。FPGA块的灰色区域表示静态逻辑,标记为重新配置块“A”的块部分表示可重构逻辑。静态逻辑保持工作,不受加载部分BIT文件的影响。可重构的逻辑将被部分BIT文件的内容所取代。

2、相关术语介绍

以下术语特定于部分重新配置功能,并在本系列中使用。

2.1 Bottom-Up Synthesis(自底向上综合)

自底向上综合是基于模块设计的综合,无论是在一个项目还是多个项目中。在Vivado中,自底向上的综合被称为out-of-context(OOC)综合。OOC综合为每个OOC模块生成一个单独的网表(或DCP),这是部分重新配置所必需的,以确保没有在模块边界上进行优化。在OOC综合中,顶层(或静态)逻辑与每个OOC模块的黑盒模块定义一起合成。

我们对此进行一个简单的总结:

(1)模块间独立综合工程,产生多个网表

(2)自底向上综合要求为每个分区分配一个独立的网表

(3)没有跨越边界的优化。这样,可以对设计的每个分区进行独立的综合

(4)对带有用于分区的黑盒顶层进行综合

2.2 Configuration(配置)

一个配置是一个完整的设计,包括静态逻辑,以及用于每个可重构分区的一个可重构模块。

在一个部分重构FPGA项目中,可能有多个配置。每个配置生成一个充分的比特流文件,以及用于每个可配置模块的一个部分比特流文件。

2.3 Configuration Frame(配置帧)

配置帧是FPGA配置内存空间中最小的可寻址段。重构配置帧是由这些最底层元件构建的。在Xilinx设备中,基本的可重构帧的大小为一个元件(CLB、BRAM、DSP)宽度和一个时钟区域高度。这些帧中的资源数量因设备系列而异。

2.4 Internal Configuration Access Port ,ICAP(内部访问访问端口)

内部配置访问端口(ICAP)本质上是SelectMAP接口的内部版本。有关详细信息,请参见7系列FPGAs配置用户指南(UG470)[参考文献7]或UltraScale体系结构配置用户指南(UG570)

2.5 Media Configuration Access Port ,MCAP(媒体配置访问端口)

在UltraScale 设备中,MCAP是从一个特定的PCIe块到ICAP的专用链接,在配置Xilinx PCIe IP时,可以启用此接入点。

2.6 Partial Reconfiguration ,PR(部分可重配置)

部分可重配置是通过下载部分比特流来修改操作FPGA设计中的逻辑子集。

2.7 Partition(分区)

分区是设计的一个逻辑部分,设计者在层次边界上定义,这个定义用于设计重用。一个分区要么作为新的实现,要么从以前的实现中保留。保留的分区不仅维护相同的功能,而且还维护相同的实现。

2.8 Partition Definition ,PD(分区定义)

这是一个仅在工程流程中使用的术语。一个分区定义定义了一组与模块实例(或可重构分区)相关的可重构模块。一个PD应用于模块的所有实例,但是不能与模块实例的子集相关联。

2.9 Partition Pin(分区引脚)

分区引脚是在静态和可重配置逻辑之间的逻辑与物理的连接。

2.10 Processor Configuration Access Port,PCAP(处理器配置访问端口)

处理器配置访问端口(PCAP)类似于内部配置访问端口(ICAP),是用于配置Zynq-7000 AP SoC设备的主端口。有关更多信息,请参见Zynq-7000所有可编程技术参考手册(UG585)[参考文献9]

2.11 Programmable Unit,PU(可编程单元)

在UltraScale结构中,这是用于可重配置所需的最小资源。PU的大小因资源类型而异。在UltraScale中,由于相邻的位置共享一个布线资源(或互联块),因此成对定义PU。

2.12 Reconfigurable Frame(可重配置帧)

可重构帧(在本指南中除“配置帧”之外的所有参考文献中)表示FPGA中最小的可重构区域。可重构帧的比特流大小取决于帧中所包含的逻辑类型。

2.13 Reconfigurable Logic(可重配置逻辑)

可重构逻辑是作为可重构模块的一部分的任何一个逻辑元素。当加载部分比特流文件时,会修改这些逻辑元素。可以重新配置逻辑组件的许多类型,如LUTs、触发器、BRAM和DSP块。

2.14 Reconfigurable Module,RM(可重配置模块)

在可重配置分区内,RM是网表或者HDL描述的实现。每个可重配置分区内可以有很多个可重配置的模块。

2.15 Reconfigurable Partition,RP(可重配置分区)

RP是在一个例化中的属性设置,其定义了该实例是可重配置的。RP是设计层次中的一个层次,在这个层次上可以使用不同的RM进行实现。例如,一些Tcl命令,如opt_design、place_design和route_design,用于检测实例上的“HD.RECONFIGURABLE”属性,并且正确地处理它。

2.16 Static Logic(静态逻辑)

所有设计内的逻辑是不可重配置的,它不是可重配置分区的一部分。当对可重配置分区进行重新配置时,静态逻辑总是活动的。

2.17 Static Design(静态设计)

静态设计时设计的一部分,它在部分可重配置的过程中不会发生变化。静态设计包括顶层和没有定义为可重配置的所有模块。静态设计由静态逻辑和静态布线所建立。

三、可重构的应用

部分可重构的基本前提是,设备的硬件资源可以像微处理器切换任务一样进行时间上的多路复用。因为设备是在硬件中切换任务,所以它具有软件实现的灵活性和硬件实现的性能优点。这里提出了几个不同的场景来说明这项技术的优势。

1、Networked Multiport Interface(网络多端口接口)

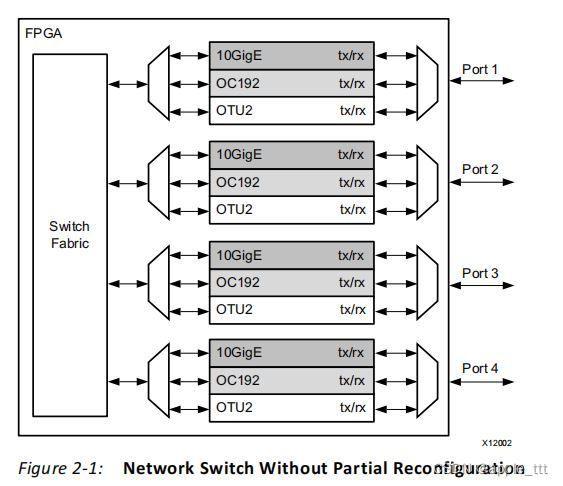

下面以网络多端口接口的设计为例,说明可重构的优势。如下图所示:

这是一个40G OTN交换机应用程序。交换机客户端端口支持多种接口协议。但是,在配置FPGA之前,系统无法预测将使用哪个协议。为了确保FPGA不需要重新配置,以及因此禁用所有端口的情况,对每个端口都实现了每个可能的接口协议。

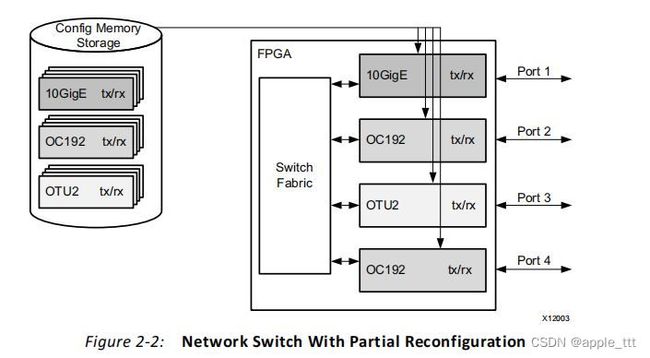

从上图就可以看出,该设计的效率很低,这是因为每个端口只使用一种协议。如下图所示:

通过使每个端口成为可配置的模块来实现更高效的设计。这样,就消除了将多个协议引擎连接到一个端口上需要使用MUX元件的问题。

除了效率之外,部分可重构的设计还有其他优点。在图2-2的示例中,可以在任何时候支持一个新的协议,而不影响静态逻辑,即本例中的交换机结构。当为任何端口加载一个新标准时,其他现有端口都不会受到任何影响。可以创建其他标准并添加到配置内存库中,而不需要完全重新设计。这使得交换机结构具有更大的灵活性和可靠性,同时减少了交换机结构和端口的停机时间。可以创建一个调试模块,以便如果一个端口遇到错误,则可以为一个未使用的端口加载分析/校正逻辑来实时处理问题。

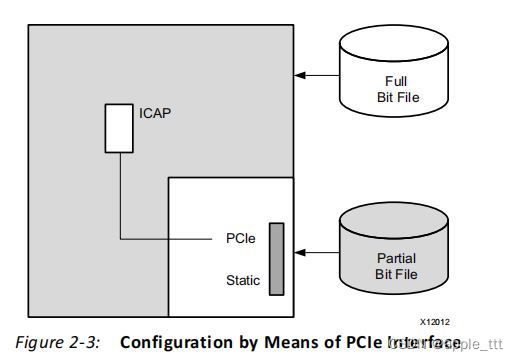

2、Configuration by Means of Standard Bus Interface(采用标准总线接口进行配置)

部分重构可以使用与系统体系结构更兼容的接口标准来创建一个新的配置端口。例如,FPGA可以是PCIe总线上的外设,系统主机可以通过PCIe连接配置FPGA。开机复位后,FPGA必须配置一个完整的BIT文件。但是,完整的BIT文件可能只包含PCIe接口和与内部配置访问端口(ICAP)的连接。

系统主机可以使用通过PCIe端口下载的部分比特流文件来配置大部分FPGA功能

PCIe标准要求外设(在本例中是FPGA)确认任何请求,即使它不能为该请求提供服务。重新配置整个FPGA将违反此要求。因为PCIe接口是静态逻辑的一部分,所以在部分重新配置过程中它总是活动(active)的,从而确保FPGA即使在重新配置期间也能响应PCIe命令。

串联配置是一个相关的解决方案,乍一看似乎是相同的,在这里显示。然而,使用部分重新配置的解决方案与串联配置在两个方面有所不同:

(1)首先,使用PR的配置过程是一个完整的设备配置,通过压缩变得更小更快,然后是一个部分比特流,覆盖黑盒区域以完成整体配置。串联配置是一个两阶段的配置,其中每个配置帧被精确地编程一次。

(2)第二,7系列设备的串联配置不允许用户应用程序的动态重新配置。使用部分重新配置,可以使用不同的用户应用程序或字段更新重新加载动态区域。UltraScale的串联配置一般允许现场更新和与PR兼容。整个流程是一个两阶段初始负载的串联配置,然后是部分重新配置,以动态修改用户应用程序。

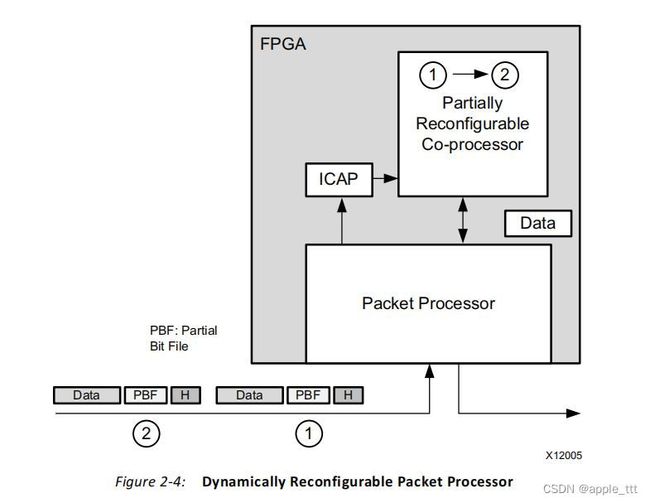

3、Dynamically Reconfigurable Packet Processor(动态可重配置包处理器)

包处理器可以使用部分重新配置来根据接收到的包类型快速更改其处理功能。在下图中,数据包包含头部(PBF),或者特殊数据包包含部分比特流文件。处理部分比特流文件后,它用于重新配置FPGA中的协处理器。

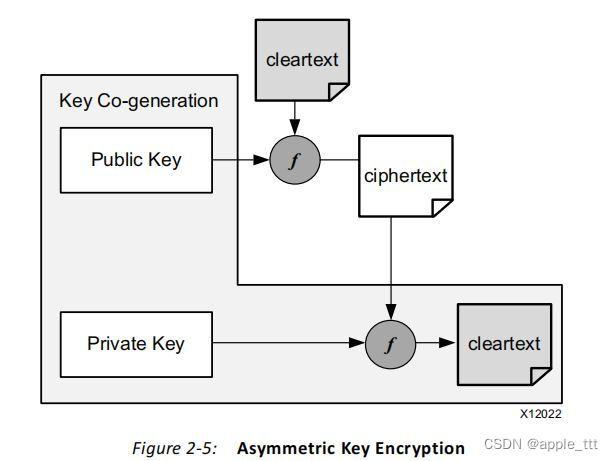

4、Asymmetric Key Encryption(非对称密钥加密)

有一些新的应用程序,如果没有部分重新配置,它们是不可能实现的。当部分重新配置和非对称加密相结合时,可以构建一种非常安全的保护FPGA配置文件的方法。

阴影框中的一组功能可以在FPGA的物理包中实现。明文信息和私钥永远不会离开一个受良好保护的容器。

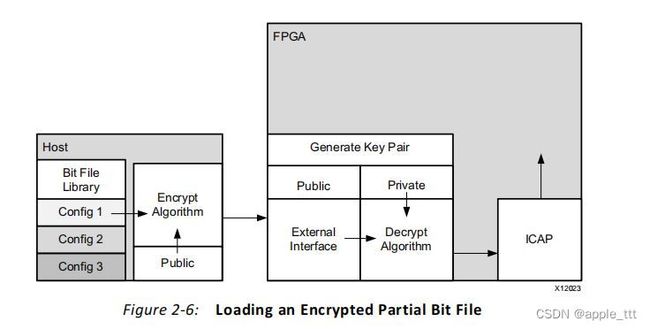

在真正实现这个设计时,初始的比特流文件是一个未加密的设计,它不包含任何专有的信息。初始设计只包含产生公钥和私钥对的算法,以及主机、FPGA和ICAP之间的接口连接。

在加载初始文件后,FPGA产生公钥和私钥对。公钥发送给主机,用来加密部分比特流文件。

如下图所示,加密的部分BIT文件被下载到FPGA,在那里它被解密并发送到ICAP,以部分重新配置FPGA。

部分BIT文件可能是FPGA设计的绝大多数,而静态设计中的逻辑只消耗了整个FPGA资源的很小部分。

四、小结

本文着重介绍了FPGA的可重构技术,可重配置技术是Xilinx提供的用来高效利用FPGA设计资源实现FPGA资源可重复利用的最新的FPGA设计技术,这种技术的发展为FPGA应用提供了更加广阔的前景。在此基础上,我们简单介绍了与此技术相关的术语含义,最后介绍了FPGA可重构技术的应用。