VIRTEX II 系列FPGA的配置部分文档的翻译阅读参考

最近想要阅读了一下VIRTEX II系列的手册,英语水平实在有限没法直接阅读,只能一点点拿软件翻译过来阅读。为了以后读着方便现在发出来,也可以供大家阅读时参考使用,现在把翻译结果发出来。

原版内容也挺难找的,我是在这个人的资源这里下载的。UG002 VIRTEX II用户手册

本文内容开始字317页配置细节部分

目录

- 配置存储单元:列和帧

-

- IOB列

- IOI列

- CLB列

- BlockRAM列

- BRAM互联资源列

- GCLK列

- 配置存储单元寻址

-

- 比特流数据包

- 配置控制逻辑

- 数据包处理器

- 配置存储器

-

- CRC寄存器

- FAR帧地址寄存器(Frame Address Register)

- FDRI/FDRO帧数据输入输出寄存器(Frame Data Input/Output Register)

- CMD命令寄存器

- CTL控制寄存器

- MASK 掩码寄存器

- STAT 状态寄存器

- LOUT (Legacy Output Register)

- COR配置选项寄存器(Configuration Options Register)

- MFWR多帧写入寄存器(Multiple Frame Write Register)

- FLR帧长度寄存器(Frame Length Register)

- KEY初始秘钥地址寄存器(Initial Key Address Register)

- CBC密码块连接寄存器(Cipher Block Chaining Register)

- DEVICE ID寄存器

- 配置

-

- 默认的初始化配置流程

- 开机重配置和关机重配置Active and Shutdown Reconfiguration

- 部分重配置 Partial Reconfiguration

- 部分重配置过程

- 部分重配置应用程序和软件流

-

- 基于差异的BitGen -r流

- 模块化设计流

- BitGen的PartialMask功能

- BlockRAM “Savedata”

- 回读Readback

-

- 准备一个设计用于回读

- 回读命令序列

-

- 读配置寄存器的过程(SelectMAP)

- 读配置存储空间的过程(SelectMAP)

- 使用JTAG接口方位配置寄存器

- 读配置寄存器的过程(JTAG)

- 读配置存储单元的过程(1149.1 JTAG)

- 读配置存储空间的过程(1532 JTAG)

- 回读文件

- 验证回读数据

-

- 将回读数据与.rbd“golden”回读文件进行比较,使用.msd掩码文件。

- 使用.bit文件和.msk文件

- 回读捕获

- 使用ChipScope ILA

在一个VIRTEXII 设备中,所有用户可编程特性都是由配置存储单元控制的,这些配置存储单元是易变的,必须启动时被配置。这些配置单元被称为配置存储器,他们定义了查找表内容,信号布线路径,IOB电平标准,以及所有用户设计的其他方面。

为了编程这个配置存储单元,配置控制逻辑的指令和配置单元的内容被以比特流(bitstream)的形式提供,比特流是通过JTAG或SelectMAP或Serial configuration之一的接口提供给设备(FPGA)的。比特流的组成在很大程度上与配置方法无关,但是,某些操作比如回读(Readback)只能通过SelectMAP 或 JTAG的接口进行。

配置存储单元:列和帧

VIRTEXII的配置存储单元被按垂直帧排布,一帧的数据宽度是1bit,这些配置存储单元从设备顶部延伸到设备底部。这些帧是VIRTEXII配置存储单元中的最小的可寻址段;因此,所有动作都必须对整个帧进行操作。配置存储单元的帧不直接映射到任何一块硬件,相反,他们配置了一个窄的垂直slice上的许多物理资源。

VIRTEXII的帧取决于设备的大小,在表4-15中被展示

VIRTEXII设备不需要任何指定大小的比特流。比特流的长度可以随设备的Stepping Level和比特流的生成设置BitGen而变化。

配置帧被分为六种列类型,它们大致对应于物理设备资源。所有VIRTEXII设备都具有相同的配置列类型:IOB,IOI,CLB,GCLK,BlockRAM和BlockRAM 互连资源。图4-31中展示了物理设备资源和配置存储单元的联系。

所有的VIRTEXII设备都含有相同数量的IOB,IOI,和GCLK列。然而,CLB,BRAM和BRAM互联资源列的数量因设备大小而不同。对于所有设备,每列类型的帧数保持不变,表4-16中展示了每个设备的列数和每列的帧数。

IOB列

IOB列配置了设备左右两边IO的电平标准。在设备顶部和底部的IOB被垂直对齐的CLB列配置。每个设备商有两个IOB列。

IOI列

IOI列配置了在设备左边和右边上的IOB的寄存器,复用器和三态缓冲器(3-state buffers)。在设备顶部和底部的IOB被垂直对齐的CLB列配置。每个设备有两个IOI列。

CLB列

CLB列对可配置逻辑块,布线进行编程,大多数位于设备顶部和底部的IOB也是被CLB编程的。CLB配置列的数目与设备中的物理CLB列对应。

BlockRAM列

BlockRAM配置列只编程BlockRAM中的用户存储空间。BlockRAM配置控制逻辑与用户设计中访问BlockRAM的方式相同:通过BlockRAM原语上的地址和数据引脚。因此,当配置逻辑正在访问块RAM列时,用户设计无法访问BRAM。因此,不要在BRAM上进行主动重新配置和回读(active reconfiguration and readback)。BRAM配置列的数目与设备中的物理BRAM列对应

BRAM互联资源列

BRAM互连列编程所有其他BRAM和乘法器的特性,包括纵横比。BRAM互连资源列的数目和设备中的物理BRAM列对应。

GCLK列

GCLK全局时钟列编程大多数的全局时钟资源,包括clock buffers和DCM。每个设备上有一个全局时钟列。

配置存储单元寻址

每一个配置真都有一个唯一的32位的地址,这个地址由块地址(BA),主地址(MJA),次地址(MNA)和字节数构成。内容被展示在图4-32中。主地址标识块中特定的列,次地址标识列上特定的帧。

字节数仅在VIRTEXII的配置逻辑(后面叙述)中被使用。用户不能在帧内寻址字节,必须始终设置帧地址中的后九位为0。

VIRTEXII 配置存储单元被分为三个独立寻址的块:

Block Address0(BA00)包括所有GCLK,IOB,IOI和CLK配置列

Block Address1(BA01)包括所有BRAM列

Block Address2(BA02)包括所有BRAM互联资源列

图4-33稀释了VIRTEX的配置存储单元。每个类型的块的MJA是设备大小的函数,由CLK列的数量n和BRAM列的数量m决定。在配置期间,帧按照增加块,主地址(MJA),次地址(MNA)的顺序编程。(例如图4-33中从左到右的顺序)

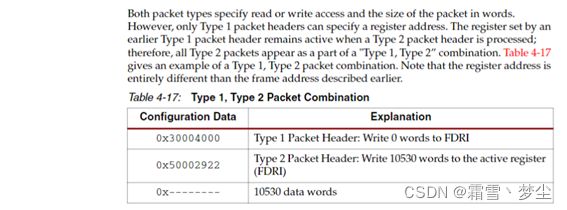

比特流数据包

VIRTEXII 比特流由32位同步字0xAA995566和大量的数据包组成。同步字的目的是为了将设备配置逻辑与比特流中第一个数据包的开头对齐。每一个数据包针对特定的配置寄存器设置配置选项,编程配置存储单元,或者切换内部信号。比特流数据包由一个32位的头和一个可变长度的身体组成,有两种数据包的类型:

第一类,用于小包(最多2^11-1个word)

第二类,用于大包(最多2^27-1个word)

配置控制逻辑

VIRTEXII的配置控制逻辑由数据包处理器,一组寄存器,和由配置寄存器控制的全局信号组成。数据包处理器控制从配置接口(SelectMAP,JTAG或Serial)到相应寄存器的数据流,而控制寄存器控制所有其他方面的配置。这一节描述了配置控制逻辑如何处理比特流数据包

数据包处理器

在上电后,数据包处理器等待同步字从配置接口输入,在这之前不解释任何数据。设备同步之后,数据包处理器等待一个有效的数据包包头;在接收到一个数据包包头之后,它将传入的数据传输至相应的配置寄存器,直到数据包指定的数据数达到0为止。在数据包结束后,数据包处理器等待新的数据包头。

在所有数据包头在到达数据举报处理器之前,都经过一个64bit的缓冲区;数据包处理器本身以32bit的字解释所有命令。为了从缓冲区中刷新出序列的最后一个命令,配置命令序列必须以至少四个32bit的NOOP命令结尾。通常,这会在比特流的末尾被找到,像图4-18中那样。JTAG的读取操作必须由命令序列中的偶数个字(word)组成。

这意味着读取命令序列必须以两个或恰好三个NOOP结尾,取决于NOOP命令之前发送的word数(奇偶)。不要在此计数中包括同步字或它之前的任何内容,并且作为完成发送JTAGread命令的标志的NOOP数只能是两个或者三个,不可以是别的数目。见349页配置寄存器读取过程(JTAG)和351页配置存储单元读取过程(1149.1 JTAG),作为例子。

配置存储器

所有配置操作都是通过对配置寄存器的读写来执行的。表4-19中汇总了这些寄存器,为每个寄存器做了详细的解释。

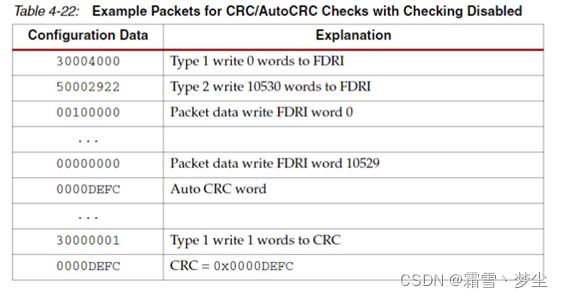

CRC寄存器

配置数据的完整性由16位CRC检验保证。CRC校验必须在设备启动前执行。党配置数据写入除LOUT以外的任何寄存器时,使用寄存器数据和地址位计算CRC值。在写入CRC寄存器后,通过将计算值与寄存器值比较,执行CRC检查。如果两个值不同,配置逻辑进入错误状态,通过将INIT_B引脚拉低并写入STATUS寄存器中的CRC_ERROR位来指示错误。

CRC校验以两种方式执行:

1显式写入CRC寄存器

2“自动CRC”功能(The “AutoCRC” feature)

显式CRC检查是通过将预计算的CRC值写入不同数据包的CRC寄存器来执行的。

自动CRC检查是一种隐式CRC写入,它发生在写入寄存器FDRI之后(Frame Data Input Register)。写数据包中的最后一个32bit字自动被解释为CRC值。数据包字数计数中不不包括CRC字。注意:如果整个比特流都写在一个类型2的数据包中,那么只有一个AutoCRC值。Table 4-21 shows an AutoCRC check.

通过在Bitgen中设置-g,CRC:Disable 选项来禁用CRC检查这个选项。这个选项将COR寄存器(Configuration Options Register)中的CRC_DISABLE设置为1。当CRC检查被禁用时,AutoCRC和隐式CRC检查仍然会发生,此时他们使用默认的CRC值0x0000DEFC,如表4-22中展示。

FAR帧地址寄存器(Frame Address Register)

配置帧由帧地址寄存器(FAR)中的值来处理。根据FAR寄存器中指定的地址写入到FDRI寄存器和从FDRO寄存器读取。FAR寄存器时刻被新值更新,CMD命令寄存器中的命令也被执行。

在写入FDRI寄存器或从FDRO寄存器读出期间,FAR寄存器自动递增;写入读出动作指FLR寄存器中指定的数量的字数为移入FDRI寄存器或移出FDRO寄存器。注意只有起始帧的地址是在写入FDRI寄存器之前写入的(334页)。帧地址组合如前面图4-32所示。

FDRI/FDRO帧数据输入输出寄存器(Frame Data Input/Output Register)

配置数据帧以将帧数据移入FDRI寄存器的方式写入配置存储单元。移入到FDRI中的数据依据FAR寄存器中指定的地址写入配置存储单元。在写入FDRI之前,必须使用WCFG命令加载CMD寄存器,并且必须已将正确的设备ID写入IDCODE寄存器。

写操作通过帧缓冲器流水线化,以便第一帧数据被写入配置存储单元时,第二帧数据被移入帧缓冲区。出于这个原因,FDRI寄存器在一次写入配置存储单元结束时必须用一帧pad将最后一帧数据冲出缓冲区,以保证最后一帧能被加载如配置存储单元。因此,最小的一次FDRI写操作需要两帧数据:一帧被加载入配置存储单元的数据和一帧pad用来将前一帧数据冲出FDRI寄存器(图4-36)。配置过程将在配置部分中详细说明。

在FLR寄存器中指定数量的数据被移入FDRI之后,FDRI寄存器中的帧数据被并行加载到FAR指定地址的帧中。在一次写入FDRI操作结束之后,VIRTEXII自动将下一个32bit的字看做AutoCRC值(见CRC部分)

配置数据帧经过FDRO寄存器从配置存储空间中被读出。在从FDRO读取之前,必须使用RCFG命令加载CMD寄存器,从FDRO读取的数据包长度有FDRO读取数据的包头指定。

读操作通过帧缓冲器流水线化,第一帧数据被移入配置接口时,第二帧数据被从配置存储单元中读出。因此,从设备中读出的第一帧数据不是有效数据;回读数据从设备中读出的第二帧开始。因为帧缓冲器的存在,最小的一次FDRO读操作需要两帧数据:第一帧用来清空帧缓冲器,后面跟一帧配置数据。回读过程将在回读部分详细说明。

从FDRO寄存器中读不产生CRC值,在读完FDRO之后也不产生AutoCRC值。

CMD命令寄存器

CMD寄存器被用于指示配置控制逻辑选通全局信号并执行其他配置功能。在写入CMD寄存器之后,命令被立刻执行。另外,每次写入FAR寄存器时,最后一次写入CMD寄存器的命令都会被再次执行。表4-23中给出了命令的类型和他们的代码。

CTL控制寄存器

CTL寄存器被用来设置配置的安全级别,持久化设置(the persist seting)和切换全局三态信号。对控制寄存器的写入被掩码寄存器中的值屏蔽,这允许GTS_USR_B信号在不重新指定Security位和Persist位的情况下切换。这些字段在图4-37中展示,在表4-24中被定义

MASK 掩码寄存器

MASK掩码寄存器过滤写入到控制寄存器中的内容。掩码内某位置上的1允许控制寄存器CTL写入相应的位置。MASK寄存器的默认是全为0。

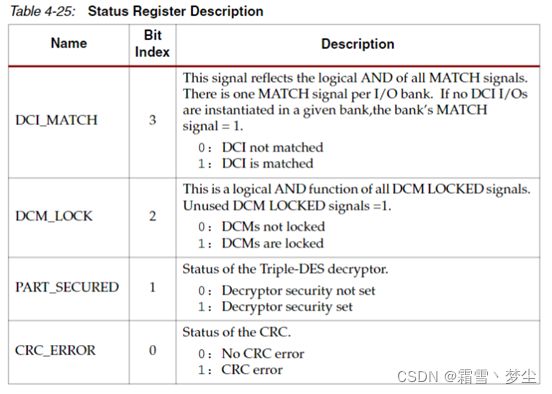

STAT 状态寄存器

STAT寄存器表明全局信号的值。这个寄存器可以通过SelectMAP或者JTAG接口读到。图4-38中给出了STAT寄存器中每一位的名字,每一位的详细位置在表4-25中详细介绍。

LOUT (Legacy Output Register)

在串行配置菊花链中配置下游设备时,传统输出寄存器LOUT被用于将数据写入DOUT引脚。LOUT寄存器不能在SelectMAP和JTAG配置模式下被读到。

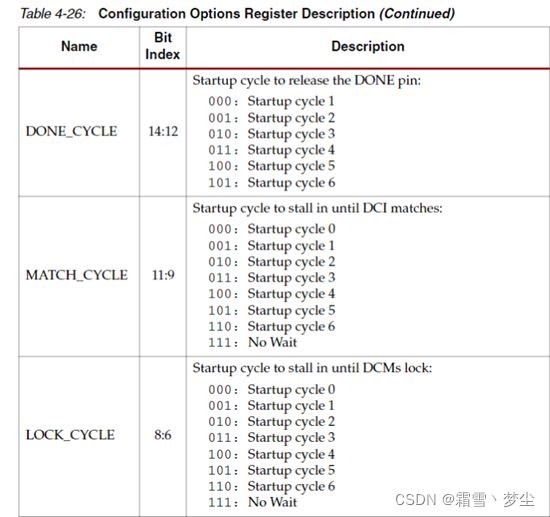

COR配置选项寄存器(Configuration Options Register)

配置选项寄存器COR被用于设置设备的某些配置选项。COR中每个位置的名称如图4-39所示,并在4-26中描述。

MFWR多帧写入寄存器(Multiple Frame Write Register)

MFWR寄存器在比特流压缩选项被使能时(Bitgen -g Compress:yes)启用。当多个帧具有相同的数据时,帧数据可以一次加载到MFWR寄存器中然后复制到多个配置存储单元的地址上。在某些情况下,这会大大减小比特流的大小。

为了写具有相同数据的多帧数据,BitGen使用下面的命令产生比特流。

1将WCFG命令写入CMD寄存器

2向FDRI中写入需要的帧

3向FAR寄存器中写入第一个需要的地址

4向CMD寄存器写入MFWR命令

5写两个pad到MFWR寄存器

6向FAR寄存器写入第二个需要的地址

7写两个pad到MFWR寄存器

8重复第六第七步直到最后一个需要的地址。

因为配置帧是垂直排列的,所以使用尽可能少的配置帧的设计可以实现更好的压缩。相同的帧通常存在于使用相同值初始化的BRAM列中,或者存在于未使用的CLB和BRAM列中。要估计实现的压缩量,请执行一下操作:

1确定相同的CAL或者BRAM列的数量。CLB列只有在未使用并且没有布线经过他们的时候才是相同的。如果不同的BRAM使用的相同的初始化值,那么这些BRAM列是相同的(一些计算公式这里不打了)

FLR帧长度寄存器(Frame Length Register)

VIRTEXII 帧的长度不会被硬编码到设备中,因为相同的配置逻辑需要被所有设备使用。帧长度必须在操作FDRI或者FDRO寄存器之前被编进设备中。

FLR寄存器存储了设备的帧长度,必须在操作FDRI或者FDRO寄存器之前被编进设备中。

注意被写进FLR寄存器的值必须比实际帧的长度小1.例如,实际写入到XC2V40的帧的长度是26个字,那么被写入到FLR寄存器中的数是0x00000019,或者25。

KEY初始秘钥地址寄存器(Initial Key Address Register)

KEY寄存器里记录了被用于比特流加密的DES数。这是一个只写的寄存器,没有任何配置接口或者用户逻辑资源可以读到它。

CBC密码块连接寄存器(Cipher Block Chaining Register)

CBC寄存器存储了DSE加密秘钥。这是一个只写的寄存器,没有任何配置接口或者用户逻辑资源可以读到它。

DEVICE ID寄存器

DEVICE ID寄存器包含了设备独特的识别码。这个寄存器与JTAG的IDCODE寄存器是分开的,尽管他们使用的是相同的32位识别码。这个寄存器的目的是为了保证下载的比特流是为了正确的设备而产生的。

在像IDCODE寄存器写入值后,它将自动进行比较;如果它和期望的IDCODE值不匹配,那么ID_ERROR信号将会产生,并暂停配置。这可以阻止向VIRTEXII中编入大小规模不正确的比特流——例如,这个机制可以防止XC2V40的比特流被编入XC2V80设备中。在写入帧数据之前,需要成功写入DEVICE ID。表4-29中列出了VITERXII的IDCODE。

配置

配置可以在设备上电并且初始化完成后开始,这个可以开始的标志是INIT引脚被释放。在初始化之后,数据包处理器忽略所有来自配置接口的数据,直到它接收到同步字;在同步之后,数据包处理器等待一个有效的数据包包头开始。

默认的初始化配置流程

在SelectMAP或者Serial配置模式时,使用默认比特流(一个使用默认BitGen设置产生的比特流)进行的配置初始化从拉动PROG_B引脚开始,或者在JTAG模式下为从发出JPROG_B指令开始。配置流程包括:

1设备同步:VIRTEXII设备以像配置逻辑发送同步字0xAA995566的方式进行同步。同步字告知设备开始解析数据包。

2重置CRC寄存器:CRC寄存器被重置以保证进行一次正确的CRC计算。详见前文对CRC寄存器的介绍。

3写入帧长度寄存器FLR:VIRTEXII设备帧的长度不会被硬编码到设备中,在配置之前,必须向FLR寄存器中写入这样一个值,其值等于没帧数据字数-1。详见FLR寄存器的介绍。

4写入配置选项寄存器COR(启动序列选项等等):详见COR寄存器介绍部分。

5写入DEVICE ID寄存器

成功写入正确的DEVICEID 才会开始写入帧数据。详见DEVICEID寄存器介绍部分。

6写入掩码寄存器MASK(取决于用户的设置):在配置之前,CTL寄存器中的SBITS 和PERSIST是被掩盖的,所以GTS_USR_B信号可以在配置之后被(be pulsed)如果需要的话。

7向CMD寄存器写入SWITCH命令(只有Master配置模式需要):SWITCH命令根据BitGen -g configate 配置设置,修改CCLK的输出频率。这个命令在slave和JTAG配置模式下无效。

8向FAR寄存器中写入起始帧地址(0x00000000):在初始化配置中,FAR寄存器被设置为起始的帧地址。在配置中只需要写入起始帧地址,FAR会在每帧写入FDRI后自动递增。

9向CMD寄存器写入WCFG命令。WCFG命令允许帧数据被写入到配置存储单元。

10向FDRI中写入配置帧,包括一帧pad:一帧pad必须被写入到,为了冲刷帧缓冲器,如前文中所述。为了完整的配置,FDRI的写入长度是:

#FDRI Words = (frames+1pad frame)*(frame length in words)

在最后一帧数据被发送给设备之后,一帧pad在同一轮写入操作中被写入,为了将最后一帧数据从帧缓冲器中冲出。这个pad帧也被算在数据包包头里的帧字数中。pad帧中包含的数据不重要。

在写入FDRI结束后,接下来的32位字被设备看做AutoCRC值。AutoCRC值不被包含在包头的帧字数中。

11向CMD寄存器中写入GRESTORE命令:GRESTORE命令更新所有Slice和IOB寄存器 以及他们的初始值。

12向CMD寄存器写入LFRM命令:LFRM(Last Frame)命令取消内部的GHIGH信号,激活所有内部互连。GHIGH信号在初始化期间(即PROG引脚be pulsed之后),并且保持激活直到发出LFRM信号。

如果需要 -g FreezeDCI Yes功能,那么进行13到15步,否则跳到16步。

13向CMD寄存器中写入WCFG命令。如果 -g FreezeDCI Yes选项在BitGen中被选择(默认是被选择),比特流中将会第二次写入FDRI寄存器。FDRI寄存器的写入以WCFG命令为起点。如果 -g FreezeDCI No 那么13到15步不会进行。

14将FAR寄存器设置到第一列IOI列。

15向FDRI中写入两帧(用于配置的一帧和pad帧)。这帧将重新配置使DCI振荡器关闭。

16发送START命令,使设备进入启动序列。START命令启动SelectMAP和Serial配置模式的启动序列,使用CCLK或者USRCLK作为序列的时钟。对于JTAG,必须发出JSTART命令以便JTAG 的TCK作为序列的时钟

17写入CTL寄存器,见CTL寄存器部分的说明。

18执行最后的CRC检查。CRC值始终都会被计算,即使CRC检验功能被BitGen禁用。当CRC检验被禁用时,默认的CRC值0x0000DEFC被写入到CRC寄存器中。

19发送DESYNCH命令。DESYNCH命令取消同步配置逻辑。更多的配置数据会被忽略直到接收到新的同步字。

20写至少64位的pad数据(NOOP command)。必须使用64位的pad数据冲刷数据包缓冲区。对于这一系列的命令来说,pad数据将DESYNCH命令冲出缓冲器进入数据包处理器。

21继续发送CCLK或者TEK直到DONE变高。取决于启动选项和外部状态(例如,如果DONE引脚被从外部拉低),需要有额外的CCLK时钟将设备带出启动序列。参考308页有关边界扫描和使用JTAG配置接口的内容。

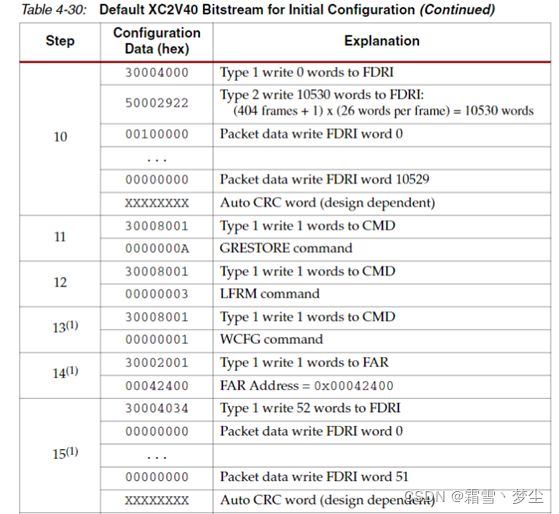

除了同步(第一步)和大FDRI写入(步骤10)之外,这些步骤中的每一步都由单个配置数据包编程,其由类型1,类型2 两种数据包组合执行。表4-30显示了如何在XC2V40的比特流中写入默认步骤。

开机重配置和关机重配置Active and Shutdown Reconfiguration

Reconfiguration这个概念描述了一个不拉低PROG引脚或者重新上电的重新对设备进行编程的概念。Reconfiguration重配置可以涉及整个设备,或者只是设备的一部分,并且可能在设备处于关闭状态(关机重配置)下发生,或者在设备保持运行时(开机重配置)发生。

由于在开机重配置器件,用户的设计还在继续运行,所以必须小心使用这一类重配置。通过开机重配置,将新设计覆盖覆盖旧设计可能产生内部冲突,可能损坏设备。此外,所有SRL16,分布式RAM,和BRAM内容都是通过完整的比特流重新初始化,会清除用户设计写入这些内存元素的任何数据。

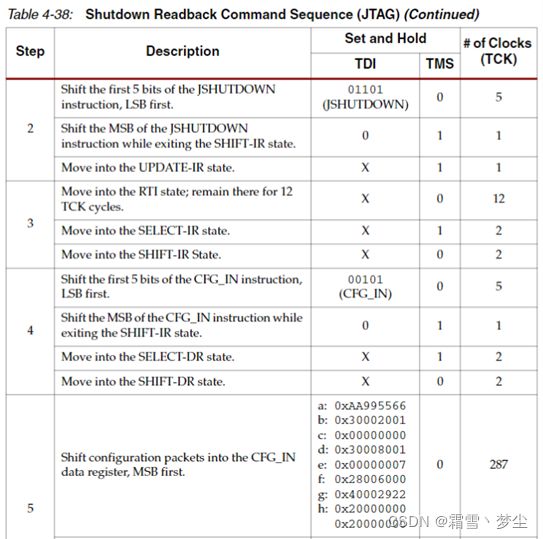

为了通过SelectMAP接口让设备关机,配置逻辑被同步然后SHUTDOWN命令被写入到CMD寄存器中(表4-31)。为了通过JTAG接口让设备关机,需要发出JTAG JSHUTDOWN命令,然后TAP控制器进入RTI状态12个TCK时钟周期。

关机序列的顺序与启动序列相反;

1撤销断言EOS

2拉低DONG引脚

3断言GTS,将除了当前的配置引脚之外都拉低

4撤销GWE,阻止RAM和触发器改变状态。

如果断言CRC_ERROR,无论是启动序列还是结束序列都无法完成。为了保证关机序列能成功完成,它应该始终以RCRC(重置CRC)命令开头。

要使设备脱离关机状态,必须使设备通过启动序列。

关机重新配置程序与上述默认的配置顺序相同,只是同步之后立即向设备发送关机指令。

部分重配置 Partial Reconfiguration

VIRTEXII 设备允许部分重配置:通过关机重配置或开机重配置,重新写一部分配置帧。执行部分重配置的理由有两个:

1修改设计而不需要重新配置整个设备

2纠正高辐射环境中存在的内存问题。

本文件针对希望改变设计的商业用户需求,航空航天客户如果需要了解高辐射环境下使用部分重配置功能纠正配置内存问题的信息,应联系Xilinx FAE 或销售代表,或打开咨询服务网站 http://www.support.xiinx.com

由于Xilinx没有记录每个帧内配置位的功能,用户经常将部分Partial Reconfiguration Process部分中的信息与下面Partial Reconfiguration Process部分中的内容结合起来。

部分重配置过程

本节解释部分重配置单个数据帧中的配置数据的机制。与完全重新配置类似,用户设计可以在继续运行时或者关闭设备后进行部分重配置。只能通过SelectMAP和JTAG接口进行部分重配置。对于SelectMAP,必须启用“persist”设置,以在配置后保留SelectMAP引脚的功能。(这些动作序列感觉内容都差不多,大概了解一下寄存器就看明白了,所以不费劲翻译了)

配置帧数据的连续帧可以以单个数据包的形式被写入到FDRI中(关机重配置中的步骤10和开机重配置中的步骤7),因为当每个帧被写入配置存储单元时,FAR会自动增加。在一些情况下,写入不连续的帧是有必要的;在这种情况下,新的帧地址必须显式写入FAR寄存器并且重复步骤8-11。与往常一样,一帧pad数据必须被添加到每个FDRI数据包后,每个FDRI数据包后面的字也会被看做AutoCRC。

适用于完全开机重配置的注意事项(见337页开机和关机重配置节)也适用于部分重配置。表4-33展示了在XC2V40设备上开机重配置单个帧所需的配置数据包。

部分重配置应用程序和软件流

想使用部分重配置的设计师面临的一个挑战是确定要重配置的帧以及这些帧的内容。有四种软件流可供部分重配置用户使用:基于差异的BitGen-r流,模块化设计流,BitGen”PartialMask”流,和BRAM”savedata”功能。

基于差异的BitGen -r流

在基于差异的BitGen -r流中,用户提供两个输入设计文件(.ncd)给BitGen,指定一个作为初始配置,另一个作为辅助配置。BitGen产生一个只配置了两个文件中不同的帧的开机配置部分比特流。这个部分比特流仅用于下载到一个已经被配置了初始配置的设备中。基于差异的比特流非常适合部分重构,只有很少的设计需要修改的应用场合,如在线修改查找表。

使用BitGen -r设置生成的部分比特文件自动使用多帧写入功能,因此是压缩的比特流。基于差异的流在应用手册XAPP290的Two Flows for Partial Reconfiguration: Module-Based or Difference-Based中有更详细的描述。

模块化设计流

XAPP290中描述的部分重配置的模块化重配置流,是为了将较大设计变更的部分重配置到新系统中。这个流程提供了一个静态的,不可重构的设计区域和一个动态的,可重构的区域,该可重构的区域可以通过两个或多个部分部分重配置模块进行重构

BitGen的PartialMask功能

BitGen的PartialMask功能允许用户选择开机重配置比特流中包含哪些配置列。PartialMask比特流仅可用于开机重配置中,而且必须与 -g activereconfig:yes这个BitGen开关一起使用。使用这个方法创建的比特流不能被用于初始化配置,因为它没有START命令也没有启动序列的许可。

根据《Development System Reference Guide》,有六个PartialMask设置。

1PartialGCLK:

将中心全局时钟列添加如需要被写入到部分比特流的列列表中。相当于PartialMask中的0:1设置

2PartialLeft:

增加在设备左端除了全局时钟之外的列,写入到部分比特流的列列表。

3PartialRight:

增加在设备右端除了全局时钟之外的列,写入到部分比特流的列列表。

4PartialMask0

增加在BA0中(Block Address 0:GCLK,IOB,IOI和CLB列)用16进制掩码表示的列,写入到部分比特流的列列表。

5PartialMask1

增加在BA1中(Block Address 1:BRAM列)用16进制掩码表示的列,写入到部分比特流的列列表。

6PartialMask2

增加在BA2中(Block Address 2:BRAM互联资源列)用16进制掩码表示的列,写入到部分比特流的列列表。

对于PartialMaskN的设置,是一个十六进制字符串,它指定了存储块中的哪一列需要被写入到部分比特流。在十六进制中的比特字符串映射到配置列,1表示需要包含在部分比特流中的列,0表示不需要包含在部分比特流中的列。半字节通过在没有相应的配置列的比特位置追加0来四舍五入。图4-40说明了比特位置和配置列之间的映射。

下面两个示例用于派生XC2V40设备的掩码。见表4-16。XC2V40设备有8个CLB列,2个BRAM列和两个BRAM互联资源列。

PartialMask 例子1:除了BRAM列外,其他列都被包含在比特流中。

要包含BA0和BA1中的所有列,PartialMask0和PartialMask1的里全是1。对于BA2,PartialMask2中的都是0。图4-41中展示了如何派生值。

![]()

PartialMask 例子2:只在比特流中包含BRAM

BlockRAM “Savedata”

通过在原始配置比特流中设置BRAM”Savedata”选项,可以在关机期间重新配置期间禁用对VIRTEXII 中BRAM的写入。使用FPGA Editor启用Savedata选项,如XAPP290中所述。

Savedata选项不能被用于开机配置,因为它可能干扰BRAM的操作。Savedata选项在使用关机重配置时是安全的。

回读Readback

VIRTEXII 设备允许用户通过SelectMAP或者JTAG接口读配置存储单元。有两种类型的回读:回读验证和回读捕获。

在回读验证期间,用户读取所有配置存储单元,包括所有用户配置存储单元上元素(LUT RAM,SRL16,BRAM)上的当前值。

回读捕获包括回读验证的内容,:除了读取所有配置存储单元,所有内部CLB和IOB寄存器的当前状态也会被读取,这对设计调试很有用。FPGA设计在工作中或关闭状态下都可以进行回读,但是建议用户避免在工作中回读,因为这可能会破坏BRAM,分布式RAM 和SRL16的内容。在主动回读期间,用户设计在读取配置存储单元时继续运行。

要读取配置存储单元,用户必须向设备发送一系列命令,指示要从配置存储单元回读的地址和字数。一旦启动,设备将指定配置存储单元的内容发送的SelectMAP或JTAG接口。线面的各节描述了读取配置存储单元的步骤:

用户可以从微处理器,CPLD或基于FPGA的系统发送回读命令序列,或者使用IMPACT来执行基于JTAG的回读验证。IMPACT是ISE提供的设备编程软件,能够执行VIRTEXII的所有回读和比较功能,并向用户报告是否存在任何配置错误。然而,IMPACT不能执行回读捕获,回读捕获在Xilinx网站单独出售的Chipscope ILA使用,它提供了卓越的设计调试功能。有关更多的信息请参阅360页如何使用Chipscope ILA

从设备读取配置存储单元后,下一步是比较回读比特流和配置比特流来确定是否存在错误。关于如何进行此操作的说明参见356页验证回读数据内容。

准备一个设计用于回读

回读有两个必须的比特流设置:必须设置BitGen安全设置为不禁止回读(-g security:none),并且不能使用比特流加密。此外,如果通过SelectMAP接口执行回读,那么端口必须在BitGen中设置”persist”选项之后(-g Persisit:Yes)被设置,以保持其功能。否则,SelectMAP数据引脚将被恢复为用户IO,从而排除进一步的配置操作。除了这些安全和加密的要求之外,无需特别考虑通过边界扫描端口启用回读。

如果需要回读捕获功能,则必须在用户设计中实例化VIRTEXII原语(图4-48)。为了捕获用户寄存器的状态,用户设计触发此原语上的CAP输入,在配置存储单元中记录当前寄存器的值。寄存器值随后与所有其他配置数据一起从设备中被读出。有关更多信息请参阅359页回读捕获内容。

回读命令序列

VIRTEXII 配置存储单元从FDRO寄存器被读出,该寄存器可以被JTAG或SelectMAP接口读到。FPGA设计在开机状态或者关闭状态时都可以进行回读,但是建议用户避免在开机状态下进行回读,因为这可能会破坏BRAM,分布式RAM和SRL16中的内容。

读配置寄存器的过程(SelectMAP)

最简单的读取操作是针对配置寄存器,如COR或SATA寄存器。任何可读的寄存器都能通过SelectMAP接口读取,但不是所有寄存器都是可读的。如表4-19中所示。通过SelectMAP接口读取STAT寄存器的过程如下:

要读取STAT以外的寄存器,应修改4-34步骤2中1类数据包包头中指定的地址。并在必要是修改字数。从FDRO寄存器读取是一种特殊情况,如下所述。

读配置存储空间的过程(SelectMAP)

从FDRO寄存器读取配置存储单元的过程与从其他寄存器读取的过程类似。但是需要额外的步骤来适应配置逻辑。来自FDRO寄存器的配置数据通过帧缓冲器,因此,应丢弃回读数据的第一帧。(参阅关于FDRO和FDRI寄存器的介绍)

![]()

除了同步(步骤1)和大FDRO读取(步骤7)之外,这些步骤中的每一个都由单个配置数据包执行。步骤1和步骤7由类型1和类型2数据包组合执行。

对于主动回读,省略步骤2,步骤4,和步骤10。请记住,包含SRL16或分布式RAM的的BRAM帧和CLB帧不能被主动回读。实际上,主动回读应该在倒数第二个CLB帧停止,因为回读最后一个CLB帧将导致FAR增加到第一个BRAM帧中,从而破坏BRAM中的内容。表4-35中展示回读命令序列

使用JTAG接口方位配置寄存器

JTAG可以JTAG的CFG_IN和CFG_OUT寄存器访问VIRTEX配置逻辑。注意CFG_IN和CFG_OUT不是配置寄存器,他们是JTAG的寄存器,和BYPASS和BOUNDARY_SCAN一样。移入CFG_IN寄存器的数据进入配置数据包处理器,在那里他们的处理方式与来自SelectMAP接口的命令的处理方式相同。

回读命令通过CFG_IN寄存器写入配置逻辑,。配置存储单元通过CFG_OUT寄存器读取。JTAG状态转换访问CFG_IN和CFG_OUT寄存器的步骤如表4-36所示:

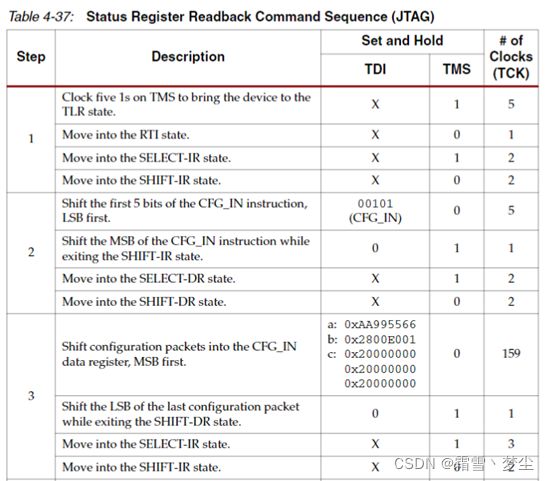

读配置寄存器的过程(JTAG)

最简单的读操作是读配置寄存器,如COR何STAT寄存器。任何可读的配置寄存器都可以通过JTAG接口读取,但是不是所有配置寄存器都是可读的。如表4-19所示。通过JTAG接口读取STAT寄存器的过程如下:

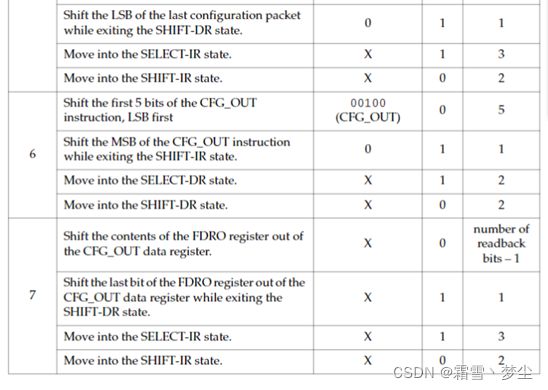

读配置存储单元的过程(1149.1 JTAG)

通过JTAG接口从FDRO寄存器读取配置内存的过程与从其他寄存器读取的过程类似。然而需要额外的步骤来适应帧逻辑。来自FDRO寄存器的配置数据经过帧缓冲器;因此回读数据的第一帧是pad,应该丢弃。建议大多数用户使用1149.1JTAG来进行回读。

![]()

读配置存储空间的过程(1532 JTAG)

IEEE1532 JTAG的回读程序与IEEE1149.1的JTAG回读程序略有不同,因为回读命令不会通过JTAG中的CFG_IN寄存器,而是ISC_READ 这个JTAG寄存器直接读配置存储单元。

在1532JTAG回读结束时,必须通过重置CRC命令或将正确的CRC值写入CRC寄存器来清除CRC错误状态。

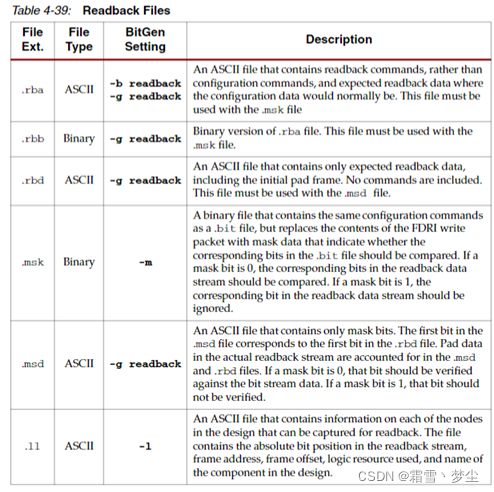

回读文件

Xilinx的比特流产生器可以产生多个文件来帮助用户读取和比较配置存储单元。这些文件再表4-39中被描述了。

.rba和.rbb文件将回读命令和预期的回读数据相结合,而.rbd文件仅包含预期的回读数据。使用.rbd文件来回读的系统必须在其他位置存储readback命令。实际的回读数据必须被.msk或.msd文件遮掩(be masked),因为这些位在rba,.rbb和.rbd文件期望的回读数据流中需要被忽略。

回读命令设置文件不会表明什么时候用户必须把SelectMAP或JTAG接口从写切换到读。用户必须根据上面说的回读命令序列来处理这个问题。

验证回读数据

回流数据流中包含配置帧数据,这个配置帧数据前面有一帧pad数据,像前文叙述的那样。这个回读数据流不包含配置比特流中的任何命令或数据包信息,并且回读器件也不进行CRC计算。回读数据流在图4-45中被展示:

通过将回读数据流与编程到设备中原始配置帧数据进行比较的方式,来验证回读数据流。但是不能比较回读数据流中的某些位,因为这些位可能对应用户存储空间或者空的存储空间。回读数据流中“不在乎”的这些位由掩码文件给定,即.msk文件和.msd文件。这些文件具有不同的格式,尽管两者传递的信息基本相同。从一旦从设备中获得回读数据后,下面的几种比较程序都是可以被使用的。

将回读数据与.rbd“golden”回读文件进行比较,使用.msd掩码文件。

验证回读数据流的最简单的额方式是将其与数据流进行比较。.rbd”golden”回读文件,并使用.msd文件作为掩码。这种方式很简单,因为回读数据流的起始和.rbd文件和.msd文件之间是由1:1的对应关系。这是调整回读数据,掩码,和预期数据变得容易。

这个.rbd和.msd文件包含了回读和掩码数据的ASCII表示,以及一个表示文件名的文件头。这些文件头信息应当被忽略或删除。在.rbd文件和.msd文件中ASCII码表示的’1’和’0’对应来自设备的二进制回读数据。注意将这些文件理解为文本,而不是二进制的。用户可能希望使用脚本或文本编辑器,将.rbd文件和.msd文件转换为二进制的形式,因为这可以简化某些系统的验证过程,并将文件大小减小八倍。

这种方法的缺点是不只是初始化配置比特流和.msd文件,golden的.rbd文件也必须被存到个地方,这增加了总体的存储需求。

使用.bit文件和.msk文件

回读捕获

配置存储单元的回读命令在回读验证和回读捕获中是相同的,但是回读捕获需要额外的步骤对内部寄存器值进行采样。用户可以通过在其设计中实例化CAPTURE_VIRTEX2原语,并在设计运行时断言改原语上的CAP输入,对CLB和IOB寄存器进行采样。在CAPTURE_VIRTEX2 CLK输入的下一上时钟上升沿,断言内部GRDBK信号,将所有CLB和IOB寄存器值存储到配置存储单元中。然后通过上述的回读过程读取配置存储单元,可以将这些值与IOB和CLB配置列一起从设备中读取。回读捕获序列使当前寄存器的值被存到相应配置存储单元的初始值寄存器中。如果GRESTORE命令在回读捕获序列更改此配置存储单元的状态之后被发送,那么寄存器可能不会返回到预期的状态上。(因为设定的初始值被改变了)

回读捕获操作也可以向CMD寄存器中写入GCAPTURE命令进行。

如果CAP信号在多个时钟周期内保持断言,则捕获单元(那个初始值寄存器)将会在每个时钟上升沿都更新为寄存器的值。要将捕获操作限制在第一个时钟的上升沿,用户可以向CAPTURE_VIRTEX2原语中增加ONEHOT属性。详见《Constraints Guide》

一旦配置存储单元帧被从设备中读出,用户可以从回读数据流中捕获寄存器值。捕获位的位置在逻辑分配文件(design.ll)中被给出,如下所述:

图4-49显示了ISE jc2_top示例设计的逻辑分配文件的一个片段。为清晰起见,标题注释中解释行格式已移至位偏移数据的开头。字段给出从配置存储单元开始的绝对位偏移量(0x00000000)。字段给出捕获位所在的帧地址,给出从帧开始的位偏移量。字段给出位与用户设计的对应关系——例如被放在X8Y15 Slice的DIR寄存器(图4-49)被放在offset 100790处。