PCIe学习笔记(一)-------1.2 PCIe总线简介

目录

1,PCIe概览

2,PCIe带宽

3,PCIe拓扑结构

4,PCIe Transaction

4.1,PCIe 事务的分类

4.2,Non-Posted Read Transaction

4.3,Non-Posted Read Transaction for Locked Requests

4.4,Non-posted Write Transactions

4.5,Mwr

4.6,Poster Message Transaction

1,PCIe概览

PCIe是第三代外围设备总线,英文缩写为PCIe或者PCI Express。PCIe是点对点,全双工的差分传输信号总线。点对点互连表示链路上的电气负载有限,从而使发送和接收频率可扩展到更高。PCIe目前成熟的版本有GEN1,GEN2,GEN3,GEN4和GEN5,每一代相较上一代传输速率和传输带宽都有了很大幅度的提升。PCIe每个Function的配置空间从PCI的256B扩展到了4KB,但前64B(PCI Header)配置寄存器仍然是相同的。

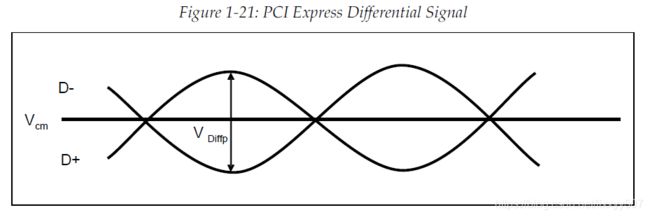

差分信号对:PCIe采用差分对来串行传输数据。

D+和D-之间电压差为正表示1,D+和D-之间的电压差为负表示0。两者之间没有电压差意味着处于第三态---高阻态,这种状态称为链路的electrical-idle状态。

选择一个参考地后,差分信号两个电压的相对差值(D+ - D-)就是差模电压,两电压的绝对高度的平均值((D+ + D-) / 2)就是共模电压。PCIe差分信号峰峰值的电压范围是800mV~1200mV,共模电压可以为0V~3.6V之间的任何电压。也就是说,差分信号相交的地方(Vcm)不一定是绝对零。

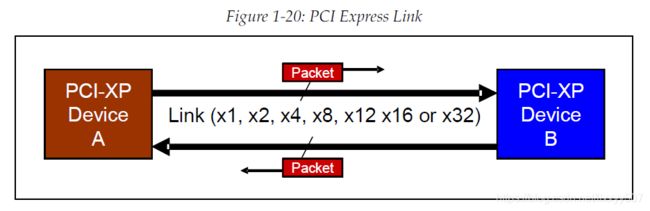

链路:PCIe链路是两台设备之间的物理连接。

Lane:一条链路在每个方向上可以有x1,x2,x4,x8,x16或者x32个信号对,这些信号对称为lane。每个信号对分为TX和RX,因为是差分信号,所以每个信号对总共有四根信号,分别为TX+,TX-,RX+,RX-。

下图中PCI-XP表示PCIe。

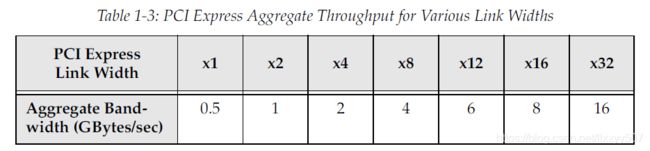

2,PCIe带宽

PCIe GEN1在链路上的传输速率为2.5Gb/s。PCIe在GEN1和GEN2采用了8b/10b编码方式,也就是说链路上传输10b数据,实际传输的有效数据只有8b。对于GEN1 x1的PCIe链路,传输的有效带宽为:

2.5Gb/s * 2 * 8b/10b * B/8b = 0.5GB/s 2代表TX和RX

3,PCIe拓扑结构

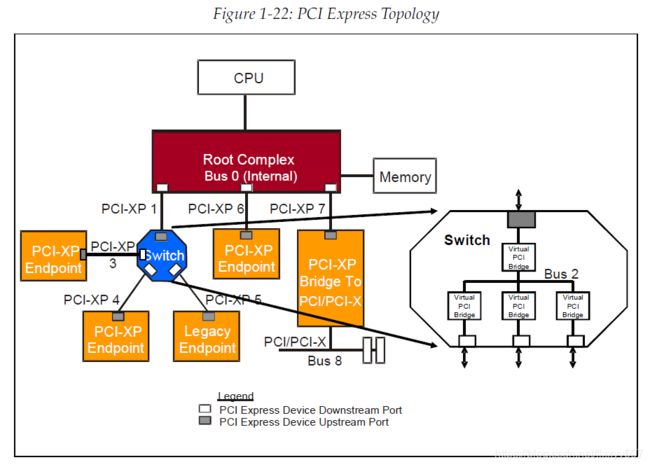

PCIe主要的组件有RC(Root Complex),SW(Switch),EP(Endpoint)。RC可以和所有device进行通信,一个EP也可以和一个PCIe系统中的EP来通信(Peer-to-Peer)。协议规定SW需要支持Peer-to-Peer,但对于有多个port的RC并没有要求。也就是说下图中 PCIe4 和 PCIe5 可以进行数据通信,但 PCIe4 和 PCIe6 就不一定能进行数据传输。

RC是指连接CPU和存储器子系统以及PCIe结构的设备,可以支持一个或多个PCIe Port,下图中RC支持3个PCIe Port,每个Port连接EP或者SW,SW形成一个子层,又可以挂接其他PCIe设备。

RC上的port可以进行数据交互,但协议并没有规定必须支持。

SW是PCIe链路上进行转接的一类设备,拥有一个upstream prot和多个downstream port。可以将SW当作多个PCIe桥组成的设备。

EP是PCIe链路的末端,有两种类型:Legacy Endpoint 和 PCIe Endpoint。传统EP支持IO事务,而且还需要能接收锁定事务。而PCIe EP不必支持IO事务和接收锁定事务,但必须支持MSI中断。

upstream port:在一个PCIe 设备上靠近RC方向的port。

downstream port:在一个PCIe 设别上远离RC方向的port。

Ingress port(入端口):接收数据包的端口。

Egress port(出端口):发送数据包的端口。

在一个PCIe系统中,upstream port 和 downstream port是固定的,但是Ingress port 和 Egress port 是不固定的,和数据包的传输方向相关。例如:图中RC发起 MWr 事务到PCI-XP 4,那么SW上的upstream就是Ingress port,downstream就是Egress port。而当PCI-XP4发起 MWr到 RC时,那么SW的downstream就是 Ingress port,upstream就是 Egress port。

4,PCIe Transaction

事务:Transaction指 requester 和 completer 之间完成一次信息传送时所需要完成的一系列或多个数据包传送的过程。

PCIe支持的事务类型与PCI、PCI-X支持的事务类型相同,包括存储器读和存储器写,IO读和IO写,配置读和配置写,此外还增加了一种新事务:消息(message)。

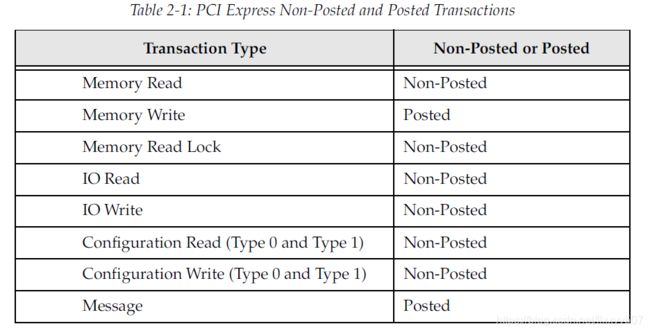

4.1,PCIe 事务的分类

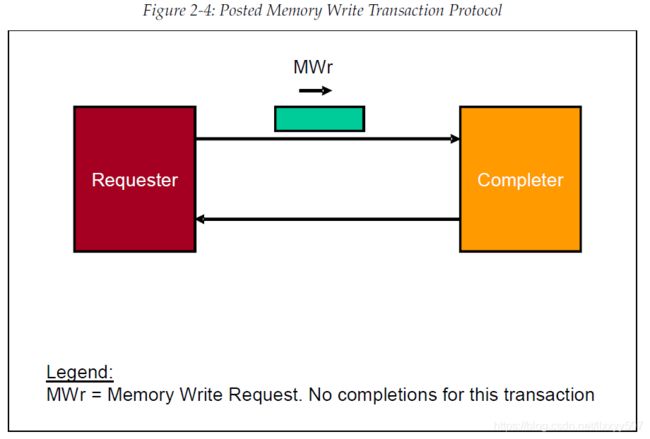

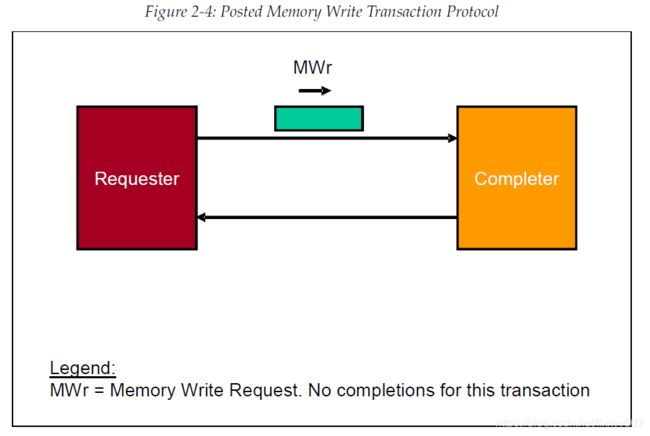

PCIe事务可以分为Non-Posted 和 Posted。Non-Posted指 requester 发送TLP请求包给completer时,completer需要返回一个TLP完成数据包给requester。Posted指requester 发送TLP请求事务包给 completer时,completer不需要回复TLP完成数据包给requester。

PCIe的数据传输以数据包的形式进行传输,通信涉及一种称为处理层数据包(Transaction Layer packet, TLP)的数据包发送和接收。TLP包可以分为TLP请求的数据包和TLP完成的数据包。TLP请求的数据包依据PCIe事务的不同而不同,对于Non-Posted事务,需要completer 返回 TLP完成包给requester。TLP完成包带数据信息的称为CPLD,不带数据信息的称为CPL。

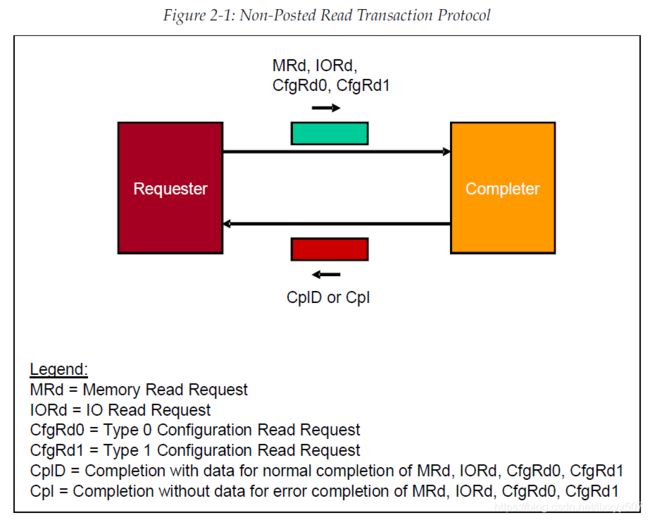

4.2,Non-Posted Read Transaction

requester : RC , EP(EP不能发起CfgRd0,CfgRd1)

completer:RC,SW,EP

当链路出现错误,completer不能获得requester 所需要读取的数据信息,completer将会返回一个CPL包(没有数据信息)和一个错误状态指示。

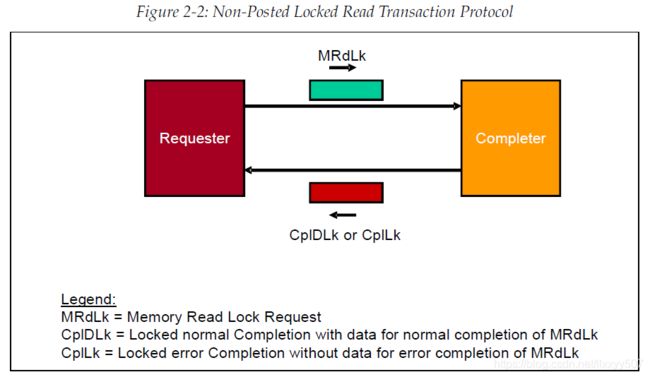

4.3,Non-Posted Read Transaction for Locked Requests

requester: RC

completer: Legacy EP

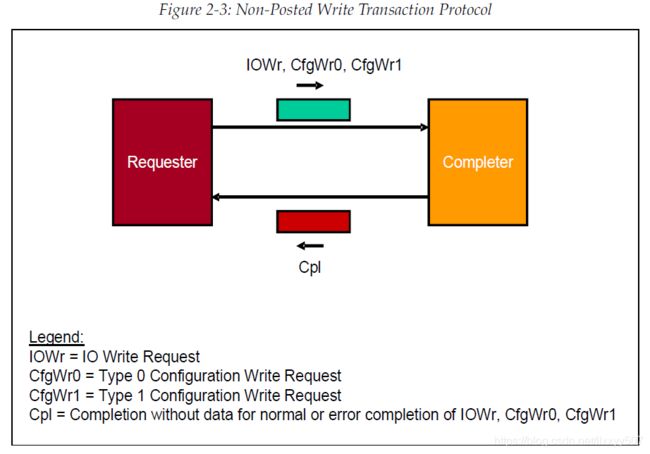

4.4,Non-posted Write Transactions

requester:RC,EP(EP不能发起CfgWr0,CfgWr1)

completer:RC,SW,EP

4.5,Mwr

requester:RC,EP

completer:RC,SW,EP

4.6,Poster Message Transaction

消息请求TLP有两类:Msg 和 MsgD。消息的传播方式有三种:(1)requester 发送给 completer

(2)RC广播给所有的EP requester:RC completer:所有EP

(3)EP发送给RC requester:EP completer:RC