FPGA 22 嵌入式块Ram 应用之 FIFO (专题:单时种FIFO 和 双时钟FIFO的使用)

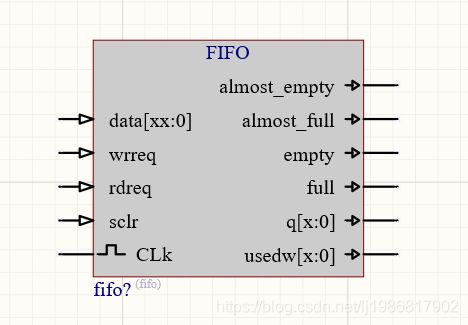

![]()

FPGA 22 嵌入式块Ram 应用之 FIFO

实验现象:通过在Quartus l软件中调用FifolP核,并进行不同形式的配置,通过仿真来验证其接口时序。

知识点:

1、FIFO IP核的使用

一、什么是FIFO.

FIFO的完整英文拼写为First In First Out,即先进先出(也可以理解为程序里面的堆)。FPGA或者ASIC中使用到的FIFO一般指的是对数据的存储具有先进先出特性的一个存储器,常被用于数据的缓存或者高速异步数据的交互。

FIFO从大的情况来分,有两类结构 : 单时钟 FIFO (SCFIFO)和双时钟FIFO(DCFIFO),其中双时钟 FIFO又可以分为普通双时钟(DCFIFO)和混合宽度双时钟FIFO(DCFIFO_MIXED_WIDTHS)。三种 FIFO结构的英文含义如下所示:。

SCFIFO:single-clock FIFO.

DCFIFO: dual-clock FIFO (supports same port widths for input and output data).

DCFIFO MIXED_WIDTHS: dual-clock FIFO (supports different port widths for inputand output data)

注意:在没有特别指明的情况下,混合宽度双时钟FIFO和双时钟 FIFo统称为双时钟FIFO。

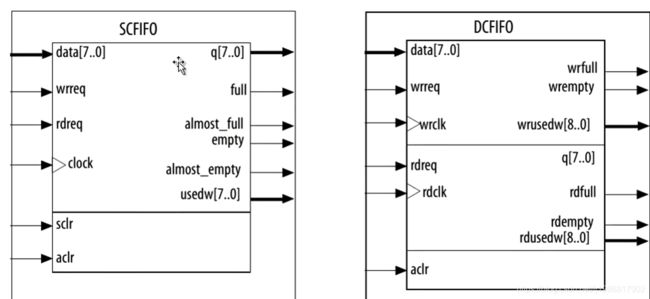

单时种FIFO 和 双 时钟 FIFO 结构图:

输入端口:

data[7:0]: 数据写入端口

wreq : 写请求信号

rdreq : 读请求信号

clock : 时钟

sclr :同步清零

aclr :异步清零

输出端口:

q[7:0] 数据读取端口

full : FIFO内数据写满状态信号

almost_full : 数据即将写满信号

empty : FIFO数据空信号

almost_empty : 即将数据全部读取完成信号

usedw[7…0] : 可用数据个数

单时钟FIFO:

单时钟FIFO常用于片内数据交互,例如,在 FPGA 的控制下从外部传感器读取到的一连串传感器数据,首先被写入FIFo中,然后再以UART串口的数据发送速率将数据依次发送出去。由于传感器的单次读取数据可能很快,但并不是时刻都需要采集数据,例如某传感器使用SPI接口的协议,FPGA 以2M的SPI数据速率从该传感器中读取20个数据,然后以9600 的波特率通过串口发送出去。此过程每秒钟执行一次。因为2M的数据速率远高于串口9600 的波特率,因此需要将从传感器中采集到的数据首先用FIFO缓存起来,然后再以串口的数据速率缓慢发送出去。这里,由于【传感器数据的读取和串口数据的发送都是可以同步于同一个时钟】的,因此可以使用单时钟结构的FIFO来实现此功能。

为什么可以说是同一个时钟的分析: 传感器那边的SPI的时钟是通过fpga 的clk 经过分频得到的,串口的发送端也是通过fpga 的clk得到的时钟,也就是说,他们都是再CLk 的时钟域下面得到,但是在发送数据的时候,仍然和Clk是相关联的(即: 两个模块之间的内部电路都是基于 always@(posedge Clk or negedge Rst_n)这么个always条件下来发送或者接收数据的),所以说,即使双方之间的时钟是不一样的,但是都是通过fpga的同一个clk控制进行发送和接收的。

双时钟FIFO:

双时钟FIFO的一个典型应用就是异步数据的收发。所谓异步数据是指数据的发送端和接收端分别同步与不同的【时钟域】;使用双时钟FIFO的独立的读写时钟结构,能够将不同时钟域中的数据同步到所需的时钟域系统中。例如,在一个高速数据采集系统中,实现将高速ADC采集的数据通过千兆以太网发送到pc机。

分析:(一定要看!!!)

【ADC的采样时钟(CLK1)由外部专用锁相环芯片产生,则高速ADC采样得到的数据就是同步于该时钟信号的,在 FPGA内部,如果 FPGA工作时钟(CLK2)是由独立的时钟芯片加片上锁相环产生的,则CLK1和 CLK2就是两个不同频率的时钟,他们的【频率和相位没有必然的联系,即使频率呈现倍数关系,但是他们两个并不是来自与同一个晶振或者说是来自同一个pll,那么相位就会有所不同,所以两边仍然没有一个确定的关系】,假如CLK1为65M,CLK2为125M,那么就不能使用125M的数据来直接采集65M速率的数据,因为两者数据速率不匹配?–>【解释:假设使用左边的CLK1作为同一个时钟,OK没问题,那么FIFO在读数据的时候,注定也是使用CLK1 来进行(读取/发送)数据的,而使用CLK1来读取的时候,右边模块(UDP_ETH)的采集数据的CLK2=125M,对于该模块来说,FIFO 发送的其实是一个65Mhz异步数据信号了,所以】,在采集过程中会出现包括亚稳态问题在内的一系列问题,所以这里就需要使用一个具备双时钟结构的FIFO来进行异步数据的收发,进而避免出现亚稳态情况。】下图为使用FIFO进行异步数据收发的简易系统框图:

双时钟混合宽度的使用:

在此系统中,由于ADC的数据位宽为8位,基于UDP协议的以太网发送模块所需的数据也是8位,因此使用的是非混合宽度的双时钟FIFО结构。假如 CLK1的频率为20M,ADC的数据位宽为16位,则可以使用混合宽度的双时钟 FIFO,在实现异步时钟域数据收发的同时,实现数据位宽的转换。通过设置双时钟FIFO的写入位宽为16位,读取位宽为8位,则可以实现将16位的ADC数据转换为以太网支持的8位发送数据,然后通过以太网发送到pc机。

使用IP核来设计FIFO 的应用及测试

单时钟FIFO的使用及配置:

1、调用FIFO流程

FIFO模块选项

1、模块输入输出定义:

具体可以参考最上方FIFO定义对端口的解释

2、功能配置

①FIFO数据的位宽

② FIFO的深度,和定义的位宽相联系,及开辟的内存空间 = 位宽*深度

③输入输出是否使用同一个时钟

1、哪些引脚是你所需要添加的信号

①full 信号

②empty信号

③usedw 信号,统计FIFO内部的数据个数

④almost_full : 添加一个almost_full信号,当我们的FIFO接收的数据大于等于某一个数时(eg: >= 254),使其变为高电平

⑤almost_empty :添加一个almost_full信号,当我们的FIFO接收的数据小于某一个数时(eg: <= 254),使其变为高电平

⑥同步清零信号

⑦异步清零信号

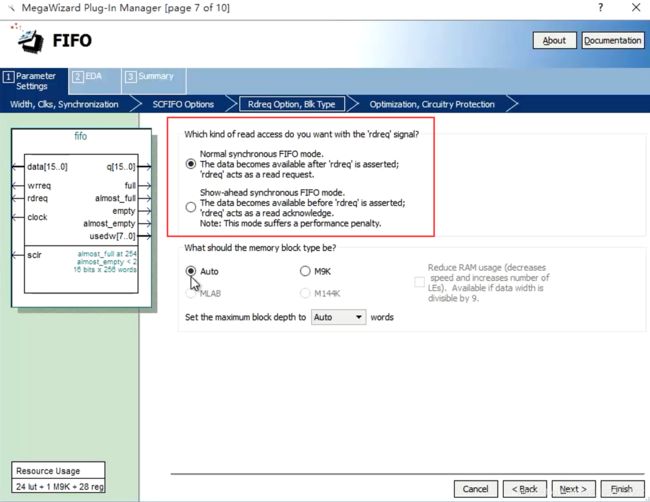

两种设计方式

① 普通模式

只有 rdreq 使能以后,q[xx:0]的数据才会被读取

② show ahead 模式

先取q[xx:00],然后发送rdreq信号,可以让FIFO准备下一个信号发送到 q[xx:0]端口

③内存块的分配,选择auto模式即可。

数据输出结果方式:

①性能有限(不考虑逻辑单元的使用,只要保证速度是最快的)

②逻辑单元优先(最小的逻辑设计单元)

点击 finish 即可。

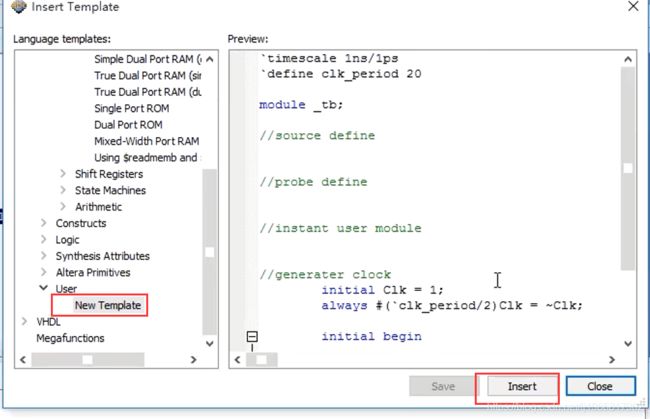

模板的创建及其使用:

点击进入

开始创建模板,并导入数据

双时钟FIFO 的配置及应用

数据的读取,是先读取低八位,再读取高八位。

FIFO 类似与队列,生活中的例子如:食堂窗口打饭,下课时间到,大家一下课就在窗口拍了一个队伍,但是呢,每一个窗口打饭的阿姨只有一个,所以这就会变成了一个队伍,但是呢,先排队过来的人(除去插队的人),阿姨总是会想给他打饭,这样的话就是一个队列,也就是一个可以理解的FIFO结构。