PCI——第2章——PCI 总线的桥与配置

摘要:记录一下PCIE第二章内容

目录

第 2 章 PCI 总线的桥与配置

2.1 存储器域与PCI总线域

2. 1. 1 CPU 域、 DRAM 域与存储器域

2. 1. 2 PCI 总线域

2. 1. 3 处理器域

2. 2 HOST 主桥

2. 2. 1 PCI 设备配置空间的访问机制

2. 2. 2 存储器域地址空间到 PCI 总线域地址空间的转换

2. 2. 3 PCI 总线域地址空间到存储器域地址空间的转换

2. 2. 4 x86 处理器的 HOST 主桥

2. 3 PCI 桥与 PCI 设备的配置空间

2. 3. 1 PCI 桥

2. 3. 2 PCI Agent 设备的配置空间

2. 3. 3 PCI 桥的配置空间

2. 4 PCI 总线的配置

2. 4. 1 Type 01h 和 Type 00h 配置请求

2. 4. 2 PCI 总线配置请求的转换原则

2. 4. 2 PCI 总线树Bus号的初始化

2. 4. 4 PCI 总线 Device 号的分配

2.5 非透明PCI桥

2. 5. 1 Intel 21555 中的配置寄存器

2. 5. 2 通过非透明桥片进行数据传递

总结

参考文章:

第 2 章 PCI 总线的桥与配置

在 PCI 体系结构中, 含有两类桥, 一类是 HOST 主桥, 另一类是 PCI 桥。 在每一个 PCI 设备中 (包括 PCI 桥) 都含有一个配置空间。 这个配置空间由 HOST 主桥管理, 而 PCI 桥可以转发来自 HOST 主桥的配置访问。 在 PCI 总线中, PCI Agent 设备使用的配置 空间与 PCI 桥使用的配置空间有些差别, 但这些配置空间都是由处理器通过 HOST 主桥 管理的。

2.1 存储器域与PCI总线域

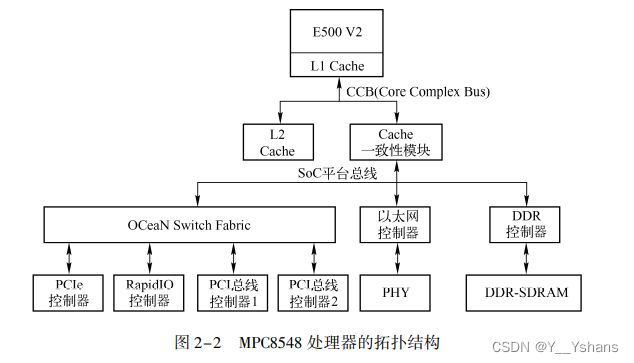

图中的处理器系统由一个 CPU、 一个 DRAM 控制器和两个 HOST 主桥组成。 在这个处 理器系统中, 包含 CPU 域、 DRAM 域、 存储器域和 PCI 总线域地址空间。

2. 1. 1 CPU 域、 DRAM 域与存储器域

严格地讲, CPU 域仅在 CPU 内核中有效。在多数处理器系统中, DRAM 域空间是 CPU 域空间的一部分, 但是也有例外。 比如显 卡控制器可能会借用一部分主存储器空间, 这些被借用的空间不能被 CPU 访问, 而只能被 DRAM 控制器, 更为准确地说是显卡通过 DRAM 控制器访问, 因此这段空间不属于 CPU 域, 严格地讲, 这段空间属于外部设备域。 本书使用存储器域统称 CPU 域与 DRAM 域。

2. 1. 2 PCI 总线域

在 x86 处理器系统中, PCI 总线域是外部设备域的重要组成部分。 实际上在 Intel 的 x86 处理器系统中, 所有的外部设备都使用 PCI 总线管理。PCI 总线域 (PCI Segment) 由 PCI 设备所能直接访问的地址空间组成。

2. 1. 3 处理器域

注意区别处理器域和存储器域。处理器域是指一个处理器系统能够访问的地址空间集合。 处理器系统能够访问的地址空间由存储器域和外部设备域组成。

2. 2 HOST 主桥

2. 2. 1 PCI 设备配置空间的访问机制

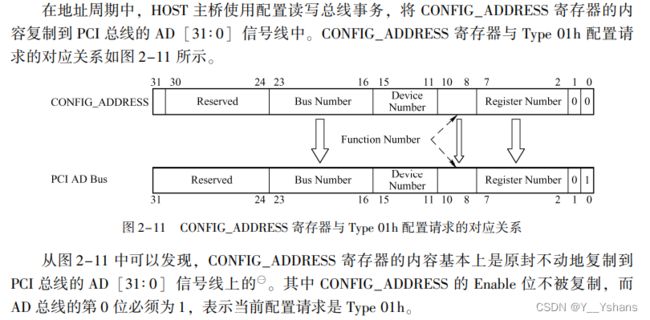

PCI 总线规定访问配置空间的总线事务, 即配置读写总线事务, 使用 ID 号进行寻址。 PCI 设备的 ID 号由总线号 ( Bus Number) 、 设备号 ( Device Number) 和功能号 ( Function Number) 组成。

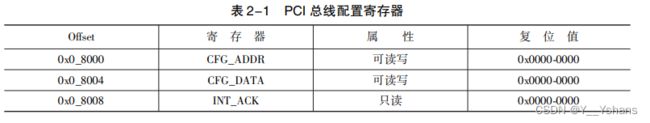

MPC8548 处理器使用 CFG_ADDR 寄存器和 CFG_DATA 寄存器访问 PCI 设备的配置空 间, 其中用 CFG_ADDR 寄存器保存 PCI 设备的 ID 号和寄存器号, 该寄存器的各个字段的详 细说明如下所示。

● Enable 位。 当该位为 1 时, HOST 主桥使能对 PCI 设备配置空间的访问, 当 HOST 处 理器对 CFG_DATA 寄存器进行访问时, HOST 主桥将对这个寄存器的访问转换为 PCI 配置读写总线事务并发送到 PCI 总线上。

● Bus Number 字段记录 PCI 设备所在的总线号。

● Device Number 字段记录 PCI 设备的设备号。 ● Function Number 字段记录 PCI 设备的功能号。

● Register Number 字段记录 PCI 设备的配置寄存器号。

2. 2. 2 存储器域地址空间到 PCI 总线域地址空间的转换

MPC8548 处理器使用 ATMU (Address Translation and Mapping Unit) 寄存器组进行存储器 域到 PCI 总线域, 以及 PCI 总线域到存储器域的地址映射。ATMU 寄存器组由两大组寄存器组 成, 分别为 Outbound 和 Inbound 寄存器组。 其中 Outbound 寄存器组将存储器域的地址转换为 PCI 总线域的地址, 而 Inbound 寄存器组将 PCI 总线域的地址转换为存储器域的地址。

CPU 对存储器域的地址访问, 首先使用 CCB 总线事务, 如果所访问的 地址在 Cache 中命中, 则从 Cache 中直接获得数据, 否则将从存储器域中获取数据。而在绝 大多数情况下, 外部设备使用的地址空间是不可 Cache的, 所以发向 PCI 设备的 CCB 总线事务通常不会与 Cache 进行数据交换。 如果 CCB 总线事务使用的地址在 HOST 主桥的 Outbound 寄存器窗口中命中, HOST 主 桥将接收这个 CCB 总线事务, 并将其转换为 PCI 总线事务之后, 再发送到 PCI 总线上。 MPC8548 处理器的每一个 HOST 主桥都提供了 5 个 Outbound 寄存器窗口来实现存储器域地 址到 PCI 总线域地址的映射, 其映射过程如图 2-4 所示。(书P47)

2. 2. 3 PCI 总线域地址空间到存储器域地址空间的转换

绝大多数操作系统将同一个空间的 PCI 总线域地址和存储器地址设为 相同的值, 但是这两个相同的值所代表的含义不同。

2. 2. 4 x86 处理器的 HOST 主桥

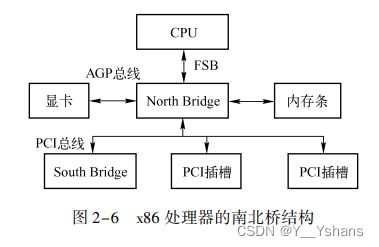

x86 处理器使用南北桥结构连接 CPU 和 PCI 设备。 其中北桥 (North Bridge) 连接快速 设备, 如显卡和内存条, 并推出 PCI 总线, HOST 主桥包含在北桥中。 而南桥 ( South Bridge) 连接慢速设备。

2. 3 PCI 桥与 PCI 设备的配置空间

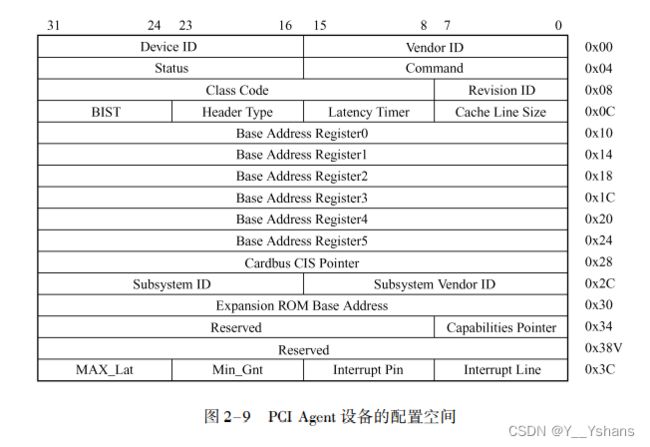

PCI 设备都有独立的配置空间, HOST 主桥通过配置读写总线事务访问这段空间。 PCI 总线规定了三种类型的 PCI 配置空间, 分别是 PCI Agent 设备使用的配置空间, PCI 桥使用 的配置空间和 Cardbus 桥片使用的配置空间。

2. 3. 1 PCI 桥

PCI 桥的引入使 PCI 总线极具扩展性, 也极大地增加了 PCI 总线的复杂度。

2. 3. 2 PCI Agent 设备的配置空间

E.P56

2. 3. 3 PCI 桥的配置空间

2. 4 PCI 总线的配置

PCI 总线定义了两类配置请求, 一类是 Type 00h 配置请求, 另一类是 Type 01h 配置请 求。根据图2-8,HOST 主桥可以使用 Type 00h 配置请求访问 PCI 设备 01, 而使用 Type 01h 配置请求通 过 PCI 桥1、 2 或者3 转换为 Type 00h 配置请求之后, 访问 PCI 总线树上的 PCI 设备11、 21、 22、 31 和 32。

2. 4. 1 Type 01h 和 Type 00h 配置请求

2. 4. 2 PCI 总线配置请求的转换原则

这里面涉及Type01h和Type00h是如何进行配置请求的。

Type00h比较容易理解,他对PCI设备的请求比较直接,只需要有配置地址寄存器enable,然后总线号设置好,再加上Device、Function和Register Number就能够找到PCI设备。

但是Type01h需要多一些步骤,主要是需要找到Bus Number 即对应的PCI总线,然后才能找到PCI设备。

2. 4. 2 PCI 总线树Bus号的初始化

在一个处理器系统中, 每一个 HOST 主桥都推出一棵 PCI 总线树。 在一棵 PCI 总线树中 有多少个 PCI 桥 (包括 HOST 主桥) , 就含有多少条 PCI 总线。

一般采用DFS算法对PCI总线进行编号,其空间复杂度比较低。

2. 4. 4 PCI 总线 Device 号的分配

PCI 设备的 IDSEL 信号与 PCI 总线的 AD [31∶ 0] 信号的连接关系决定了该设备在这条 PCI 总线的设备号。认真的读者一定可以发现在 CONFIG_ADDRESS 寄存器中 Device Number 字段一共有 5 位可以表示 32 个设备, 而 AD [31∶ 11] 只有 21 位, 显然在这两者之间无法建立一一对应 的映射关系。 因此在一条 PCI 总线上如果有 21 个以上的 PCI 设备, 那么总是有几个设备无 法与 AD [31∶ 11] 信号线连接, 从而 PCI 总线无法访问这些设备。 因为 PCI 总线在配置请 求的地址周期中, 只能使用第 31 ~ 11 这些 AD 信号, 所以在一条总线上最多也只能挂接 21 个 PCI 设备。 这 21 个设备可能是从 0 到 20, 也可能是从 11 到 31 排列。 从而系统软件在遍 历 PCI 总线时, 还是需要从 0 到 31 遍历整条 PCI 总线。 在实际的应用中, 一条 PCI 总线能够挂接 21 个设备已经足够了, 实际上由于 PCI 总线 的负载能力有限, 即便在总线频率为 33 MHz 的情况下, 在一条 PCI 总线中最多也只能挂接 10 个负载。

在一个处理器系统的设计中, 如果在一条 PCI 总线上使用的 PCI 插槽少于 4 个时, 笔者 建议优先使用 AD [17∶ 20] 信号与 PCI 设备的 IDSEL 信号连接。 因为 PCI⁃X 总线规范建议 使用 AD17 连接 PCI 设备 1、 AD18 连接 PCI 设备 2、 AD19 连接 PCI 设备 3、 AD20 连接 PCI 设备 4, 采用这种方法便于实现 PCI 总线与 PCI⁃X 总线的兼容。

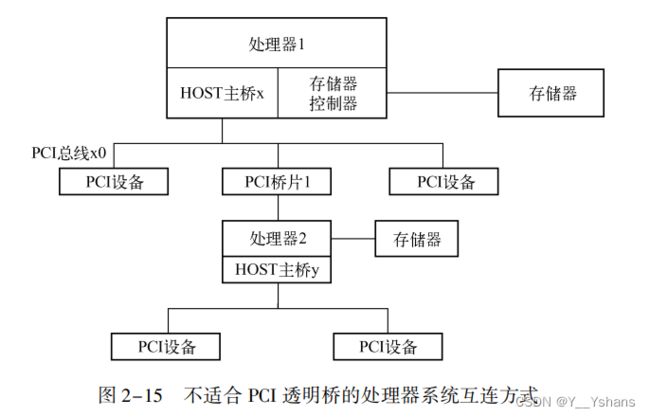

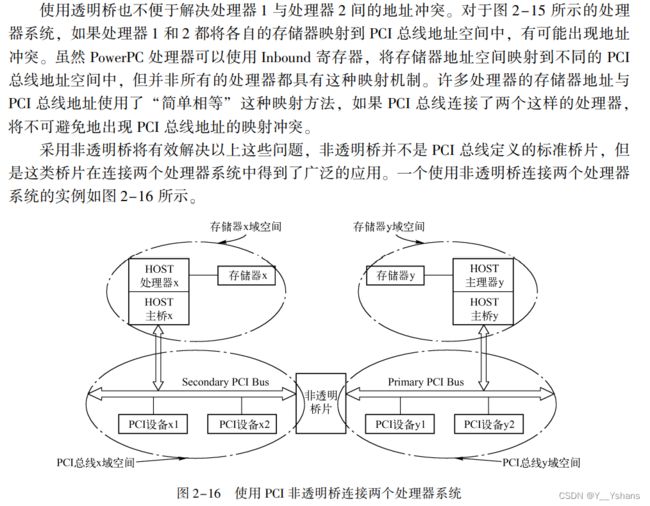

2.5 非透明PCI桥

通过透明 桥, 处理器系统可以以 HOST 主桥为根节点, 建立一颗 PCI 总线树, 在这个树上的 PCI 设备 共享同一个 PCI 总线域上的地址空间。 但是在某些场合下 PCI 透明桥并不适用。主要是他们位于同一个HOST主桥,会有地址空间不够的情况。

值得注意的是, 非透明 PCI 桥的作用是对 不同 PCI 总线域地址空间进行隔离, 而不是隔离存储器域地址空间。 而 HOST 主桥的作用才 是将存储器域与 PCI 总线域进行隔离。

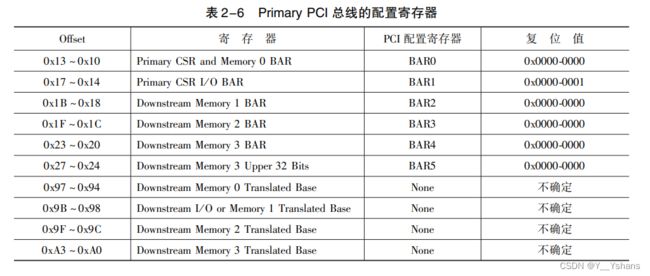

2. 5. 1 Intel 21555 中的配置寄存器

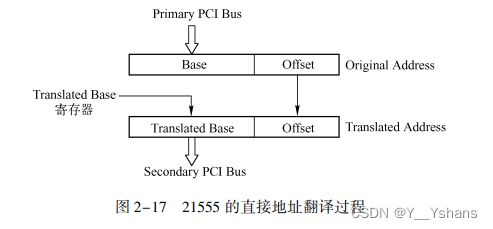

简单的来说就是,Primary PCI的数据经过变化可以给到Secondary PCI,那么两个PCI可以实现通信。

2. 5. 2 通过非透明桥片进行数据传递

知道有这个转换的东西存在就行,这样两个PCI可以通过非透明桥片进行通信。

总结

1.Host主桥与PCI桥

2.如何使用HOST桥和PCI桥访问PCI设备空间,这里面有Outbound和Inbound寄存器组

3.PowerPc处理器使用的HOST主桥

4.存储器域与PCI总线域

5.PCI桥的实现机制,深入理解PCI桥的运行机制,是理解PCI体系结构的重要基础

参考文章:

PCI_Express_体系结构导读——王齐