ARMday1

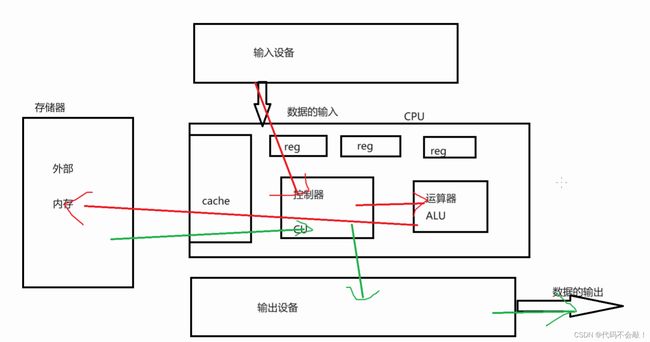

1、计算机的组成

输入设备-输出设备-运算器-控制器-存储器

输入设备:键盘、鼠标、手柄、扫描仪

输出设备:显示屏、打印机、音响

存储器:存放数据以及指令、是实现“程序存储控制”的基础、外存、内存、cache、寄存器

控制器(CU):对机器指令进行译码操作、按照译码结果进行相应的控制

运算器:根据控制器译码之后的指令和数据,进行算数逻辑运算,并且把运算的结果进行输出

2、程序编译原理(面试重点)

2、程序编译原理(面试重点)

- 预处理:gcc -E 1.c -o 1.i

- 编译:gcc -S 1.i -o 1.s

- 汇编:gcc -c 1.s -o 1.o

- 链接:gcc 1.o -o a.out

3 、指令和集合

- 机器指令(指令的机器码):由二进制的0和1组成的一条机器码。计算机解析这条机器码可以做相应的运算处理

- 汇编指令:一条汇编指令就是一条机器指令的标志。执行汇编指令也可以让机器进行相关的运算处理

- 指令集:指令的集合

4、 RISC和CISC

RISC(精简指令集)的架构主要应用于嵌入式的设备上

选取比较简单、使用频率比较高的指令集

1、指令的长度和指令执行的周期固定

2、成本、功耗、体积低、实现功能相对简单

CISC(复杂指令集)基于复杂指令集设计的CPU核心更加注重功能的完善性,复杂指令集内核会集合各自各样的指令

1、指令的长度和执行周期不固定

2、功能更为复杂、但是功耗、成本更高

5、目前几种主流的RISC内核

ARM内核、RISC-V、MIPS

6、ARM的发展历史(了解即可)ARM发展史 (huawei.com)

1>ARM:ARM公司、ARM处理器架构、ARM技术

2>ARM 公司是全球领先的半导体知识产权 (IP) 提供商,并因此在数字电子产品的开发中处于核心地位

3>ARM 的商业模式主要涉及 IP 的设计和许可,而非生产和销售实际的半导体芯片。

ARM成立 ARM前身为艾康电脑(Acorn)-----里程碑1

于1978年,英国剑桥成立,大学的孵化物。

1980年代晚期,苹果开始与艾康合作,开发新版ARM核心。

1985年,艾康开发出全球第一款商用RISC处理器,即ARM1,针对于PC市场,还没有嵌入式呢!!!

1990年,艾康财务危机,受苹果和VLSI(最早做超大规模集成电路的公司)的投资,成立独立子公司:Advanced RISC Machines(ARM),ARM公司正式成立面世 里 程碑2——嵌入式RSIC处理器

1991年,ARM推出第一款嵌入式RISC处理器,即ARM6。

1993年,发布ARM7。

1997年,发布ARM9TDMI,三星2440基于此内核。

1999年,发布ARM9E,增强型ARM9。

2001年,ARMv6架构。

2002年,发布ARM11微架构。 里程碑3——微控制器

2004年,发布ARMv7架构的Cortex系列处理器,同时推出Cortex-M3。

2005年,发布Cortex-A8处理器。

2007年,发布Cortex-M1和Cortex-A9

2009年,实现Cortex-A9、发布Cortex-M0

2010年,推出Cortex-M4(F)、成立Linaro(ARM公司牵头成立的公共组织,专门做ARM处理器在Linux平台上的一些软件的开发和移植),推出Cortex-A15 MPcore高性能处理器(性能比较高了,但是发热量很大)。

里程碑4——64位处理器时代 2011年,推出32位 Cortex-A7 处理器,ARMv8发布

2012年,开始推出64位处理器。推出 Cortex-M0+、ARM 首款64位处理器架构 Cortex-A53、Cortex-A57 架构。全球第一款64位ARM手机iPhone5s。

2013年,推出32位 Cortex-A12 处理器架构

2014年,推出 Cortex-M7(F) 微控制器架构;32位 Cortex-A17处理器架构。

2015年,推出64位 Cortex-A35、Cortex-A72 处理器架构。

2016年,推出 Cortex-M23 、Cortex-M33(F) 微控制器架构;32位 Cortex-A32 处理器架构;64位 Cortex-A73 处理器架构。

2017年,推出64位 Cortex-A55 、Cortex-A75 处理器架构。

2018年,推出微控制器 Cortex-M35P;64位 Cortex-A76 处理器架构。

2016---ARM被软银收购

2020---英伟达收购ARM未果

7、ARM架构

不同版本的指令集就是不同的架构

ARMV1-ARMV6:已经被淘汰 ARMV7架构:32位架构,支持32位指令集

ARMV8架构:64位架构,支持64位指令集,并且向下兼容32位指令

ARMV9架构:64位架构,支持64位指令集

8、ARM内核

基于不同的ARM架构设计出来的不同的处理器核心叫做不同的ARM内核

arm7/arm9/arm11

cortex-A7 ARMV7

cortex-A53 ARMV8

cortex-A55 ARMV8

cortex-A77 ARMV8

cortex-A78 ARMV8

cortex-x1 ARMV8

cortex-A710 ARMV9

cortex-A510 ARMV9

9、SOC(system on chip)

ARM公司只进行技术授权。将自己的IP授权给各个半导体公司。半导体公司根据ARM的授权,在CPU核心外围设计了一些外围电路和设备,集成在一个芯片上,这个芯片就被成为SOC。

SOC由CPU+外设备+总线组成

MCU(微控制器)

MPU(微处理器)

公司 SOC名称 内核 架构

ST STM32MP157A cortex-A7 ARMV7

三星 S5P6818 cortex-A53 ARMV8

海思 麒麟9000 cortex-A77 ARMV8

高通 骁龙888 cortex-x1 ARMV8

10、ARM产品分布

Cortex-A系列:性能最强的、最完善的处理器。属于高端处理器、在基于Cortex-A处理器为核心的开发板上可以搭载linux/鸿蒙灯标准化操作系统

Cortex-R系列:统的实时性能。对数阶的实时性要求高的场景下使用Cortex-R系列 处理器 汽车、军工

Cortex-M系列:属于ARM处理器中比较低端的芯片处理器,工作主频一般在24M-256MHz之间

Cortex-M系列 处理器一般不跑操作系统,主要执行一些裸机程序

Cortex-M系列 处理器可以搭载一些轻量级的实时系统 FreeRtos

SecurCore系列:用于对安全性能要求比较高的场景

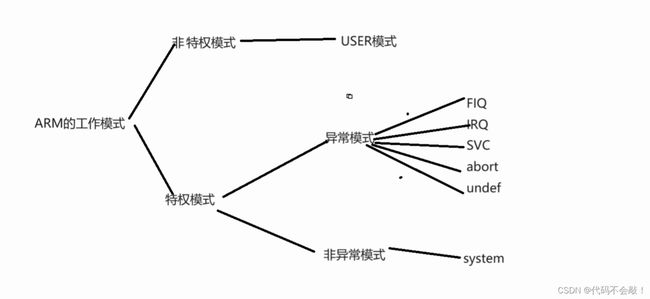

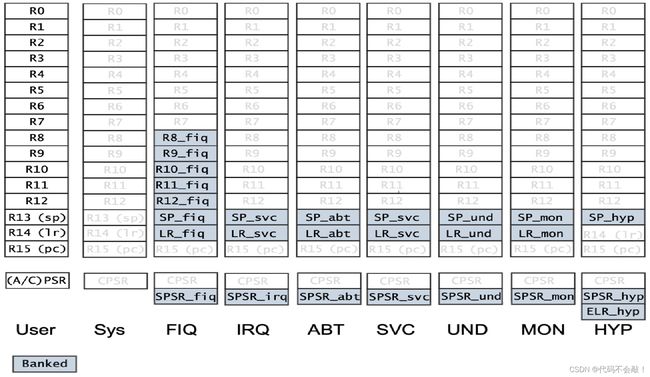

11、ARM的工作模式(面试重点)

ARM处理器在面对不同的情境下需要进入不同的工作模式进行对应模式下的处理

ARM 有7种基本工作模式:

User : 非特权模式,大部分任务执行在这种模式

FIQ : 当一个高优先级(fast) 中断产生时将会进入这种模式

IRQ : 当一个低优先级(normal) 中断产生时将会进入这种模式

Supervisor :当复位或软中断指令执行时将会进入这种模式

Abort : 当存取异常时将会进入这种模式

Undef : 当执行未定义指令时会进入这种模式

System : 使用和User模式相同寄存器集的特权模式 Cortex-A特有模式:

Monitor : 是为了安全而扩展出的用于执行安全监控代码的模式; 也是一种特权模式

HYP:虚拟化模式,当一个硬件上运行两种OS内核时进入这种模式

12、寄存器概念

寄存器是集成在CPU内部的存储组织,CPU访问寄存器数据的时候只需要根据寄存器的编号就可以访问到寄存器的数值。访问寄存器的速度块。但是寄存器存在数量限制,保存的数据量也很少

13、ARM v7架构下的寄存器组织

ARM 有37个32-Bits长的寄存器: 1 个用作PC( program counter)

ARM 有37个32-Bits长的寄存器: 1 个用作PC( program counter)

1个用作CPSR(current program status register)

5个用作SPSR(saved program status registers)

30 个通用寄存器 Cortex体系结构下有40个32-Bits长的寄存器: Cortex-A多出3个寄存器, Monitor 模式 r13_mon , r14_mon, spsr_mon

当前处理器的模式决定着哪组寄存器可操作. 任何模式都可以存取: 相应的r0-r12子集 相应的 r13 (the stack pointer, sp) and r14 (the link register, lr) 相应的 r15 ( the program counter, pc) 相应的CPSR(current program status register, cpsr) 特权模式 (除system模式) 还可以存取: 相应的 spsr (saved program status register) 每一个寄存器大小都是32位

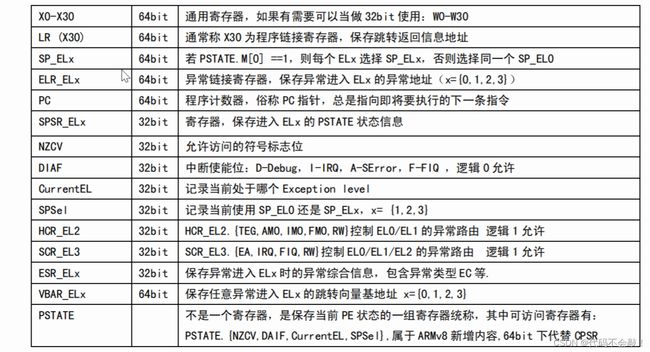

14、ARMV8架构寄存器组织

15、ARMV7架构下一些具有特定功能的寄存器

15、ARMV7架构下一些具有特定功能的寄存器

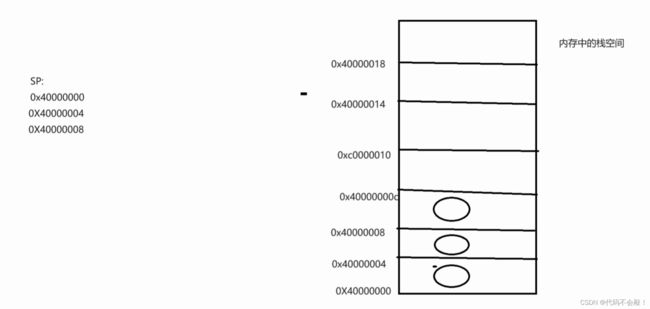

R13寄存器(the stack pointer, sp)

R13寄存器又叫SP(栈指针寄存器),这个寄存器内部保存栈顶的地址 一般在内存中分出一部分内存当作栈来使用,SP寄存器时钟保存栈顶空间的地址 栈一般存放一些临时数据,也可以用于保护现场

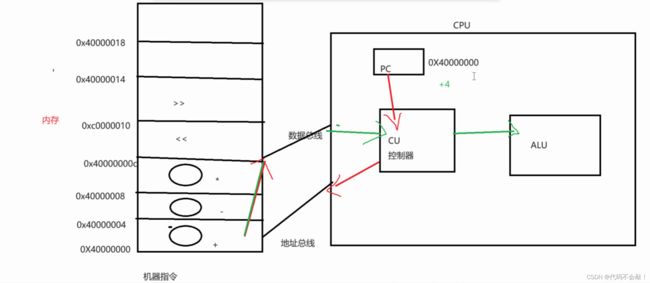

r15寄存器(the program counter, pc)

R15寄存器又被称为PC寄存器(程序计数器) 这个寄存器始终保存马上要进行取址的指令的地址,当一条指令执行结束之后PC寄存器的数值会自动向下+4 另外,在特定情况下可以手动修改PC的值进行程序的跳转

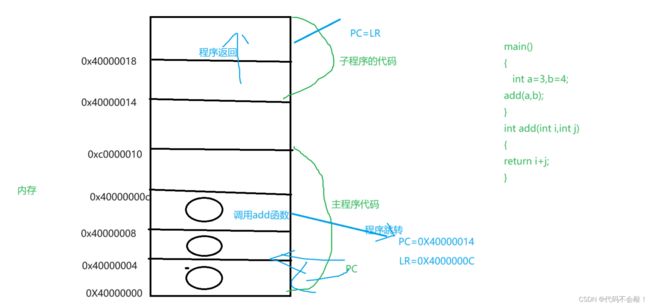

R14寄存器(the link register, lr)

R14寄存器又被称为链接寄存器,当程序在实现跳转的时候,LR寄存器中保存当前跳转指令下一条指令的地址。方便 实现程序的返回 程序的跳转实现: PC-》跳转之后指令的地址 程序的返回: PC=LR

16、CPSR寄存器(current program status register, cpsr)

CPSR:程序状态寄存器 这个寄存器中保存当前程序的运行状态,比如工作模式等信息 SPSR:saved program status register SPSR寄存器可以用于保存程序某一时刻的状态 比如当发生异常之后,处理器的工作模式要切换到对应的异常模式去处理异常,这样CPSR的数值会发生对应的改变 在处理完异常结束后,我们需要将CPSR的值修改为没有发送异常之前的状态,这个时候就可以将SPSR保存的异常发送之前的状态赋值给CPSR

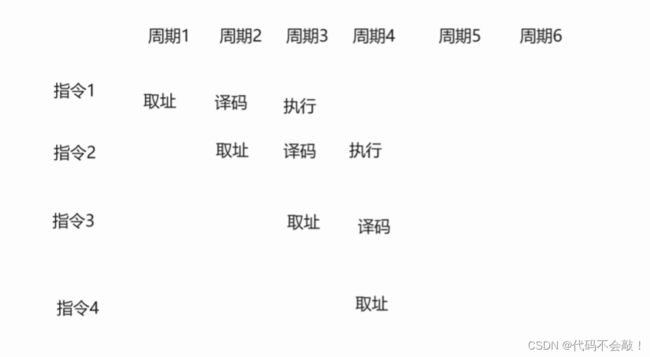

17、ARM的流水线工作

1、 一条指令的执行过程

取址:CPU将PC寄存器中保持的指令地址通过地址总线传输给存储器,存储器将PC对应的指令通过数据总线传输给CPU。CPU将指令保存在IR(指令暂存寄存器)寄存器中

译码:IR寄存器的指令交给译码器,对指令进行译码

执行:译码器对指令译码之后由运算器对译码之后的指令进行运算

2、 ARM三级流水线

当一条指令在被取址是,译码模块和执行模块处于空闲状态,这样这两个模块相当于没有得到充分利用。为了充分,利用资源,ARM引入了流水线工作,增加了指令的处理速度