8086与8088

一、8086与8088概述

- 8088/8086都是16位微处理器,内部运算器和寄存器都是16位的,同样具有20位地址线

- 8088/8086都是由执行单元(EU)和总线接口部件(BIU)两大部分构成

- 指令系统和寻址能力都相同,两种CPU是兼容的

- 8088被称作准十六位的、是紧继8086之后推出的,为了去兼容当时已有的一整套Intel外围设备接口芯片

- 外部数据总线位数的差别:8088与存储器和I/O接口进行数据传输的外部数据总线宽度为8位,而8086数据总线为16位

- 指令队列容量的差别:8086CPU的指令队列可容纳6个字节,且在每个总线周期中从存储器中取出2个字节的指令代码填入指令队列;而8088CPU的指令队列只能容纳4个字节,且在每个总线周期中只能取一个字节的指令代码

- 某些引脚还有一些差别,比如8086低电平访问存储器,高电平访问IO,而8088相反

二、8086与8088的三个共同特点

三、编程结构中的Bus interface unit与Execution unit

1.BIU

功能:与存储器、IO端口进行数据通信

组成:4个段地址寄存器、指令指针寄存器IP、20位地址加法器、6字节指令队列缓冲器

2.EU

功能:执行指令

组成:4个通用寄存器、4个专用寄存器、标志寄存器FR、ARU(arithmetic logic unit)

四、8086引脚信号与工作模式

1.基本概念

- 8086CPU可在两种模式下工作

最小模式:系统中只有8086,所有总线控制信号都直接由8086产生

最大模式:有两个或两个以上的CPU,一个为主CPU8086,其他为:数值运算协CPU8087、IO协CPU8089

2.8086引脚信号和功能

①完成一次访问内存或接口所需信号

②与外部同步控制信号

③中断请求和响应信号

④总线保持和响应信号

3.8086存储器的组织

8086的数据总线为16位,但它访问存储器时,即要能传送一个字,又要能传送一个字节,因此必须将16位宽度的存储器分成两个独立的8位宽度的存储体(奇偶存储体)来处理

4.8086的操作和时序

CPU工作时序:CPU引脚信号在时间上的关系

- 指令周期:执行一条指令所需要的时间

- 总线周期:CPU通过总线与存储器或I/O接口进行一次数据传输所需的时间

- 时钟周期:CPU处理动作的最小单位

①总线操作

一个最基本的总线周期由4个时钟周期组成,习惯上将4个时钟周期分别称为4个状态,即T1状态、T2状态、T3状态、T4状态

下面,以总线读操作的时序为例

- T1状态:CPU发地址信息

M//IO信号:从存储器读还是从I/O设备中读数据

AD15-AD0、A19/S7-A16/S3:确定20位地址

/BHE:选择奇地址存储体

ALE:地址锁存信号,以使地址/数据线分开

DT//R:为低电平,指示收发器8286接收数据,读操作

- T2状态:CPU从总线上撤销地址,使总线的低16位浮置成高阻状态,为传输数据作准备。总线的高4位(A16-A19)用来输出本总线周期状态信息(表示中断允许状态,当前使用的段寄存器名等)

A19/S6-A16/S3:出现S6-S3状态信号。决定段寄存器、IF状态、8086CPU是否连在总线上。

AD15-AD0:高阻状态。

/RD:由高电平变为低电平,开始进行读操作。

/DEN:变低电平,启动收发器8286,做好接收数据的准备。

- T3状态:总线的高4位继续提供状态信息,而总线低16位上出现CPU写出的数据或读入的数据

若存储器或I/O端口已做好发送数据准备,则在T3状态期间将数据放到数据总线上,在T3结束时,CPU从AD15-AD0上读取数据。若在T3状态,存储器或外设没有准备好数据,不能在T3状态将数据放到总线上,使READY=0,则CPU在T3和T4之间插入一个或几个TW状态,直到数据准备好READY=1为止。

- T4状态:总线周期结束。

CPU对数据总线进行采样,读出数据

注意:

由于外设或存储器速度较慢,常常不能及时配置CPU传送数据。这时,外设或存储器会通过READY信号线在T3状态启动之前向CPU发送“数据未准备好”信号,于是CPU会在T3之后插入1个或多个附加的时钟周期Tw(等待状态)。在Tw状态,总线上的信息情况和T3状态的信息情况一样。当存储器或外设完成数据传送时,便在READY线上发送“准备好”信号,CPU一接受到这信号,就会自动脱离Tw状态进入T4状态。

只有在CPU和内存或IO接口之间传输数据,以及填充指令队列时,CPU才执行总线周期。如果在1个总线周期之后,不立即执行下一个总线周期,那么,系统总线就处在空闲状态,此时,执行空闲周期。S6~S3同前一总线周期;若前一周期是读周期,则AD15 ~AD0为高阻态;总前一周期是写周期,则AD15 ~AD0保持数据有效。

②8086的复位与启动操作

8086的复位与启动信号通过RESET信号引发

RESET信号一进入高电平,CPU就会结束现行操作,如果维持4个时钟周期的高电平则复位,并且,只要RESET信号停留在高电平状态,CPU就维持在复位状态。如果是初次加电引起的复位,则要求维持不小于50μs的高电平。

复位状态:CPU将CS设置为初值0FFFFH,其他内部寄存器都被设置为0

RESET信号从高电平跳变到低电平并经过7个是时钟周期后,CPU就被启动恢复正常工作,即从FFFF0H处开始执行程序

③最小模式下的总线保持

当系统中CPU之外的另一个控制器要求使用总线时,向CPU发请求信号HOLD。在每个时钟脉冲的上升沿,CPU检测HOLD,如为高电平,并且允许让出总线时,在总线周期的T4或空闲状态Ti之后的下一个时钟周期,CPU发出总线响应信号HLDA,并且让出总线,直到HOLD信号无效,CPU才收回总线控制权。

④最大模式下的总线请求/授权

与最小模式下不同的是,在最大模式下,总线控制信号不再是HOLD和HLDA,而是功能更加完善的两个双向信号引脚/RQ//GT0和/RQ//GT1,他们都称为总线请求/授权信号端,但是前者的优先级更高。每次总线控制权的切换都是通过三个环节来实现的,即发请求脉冲、CPU发授权脉冲,用完总线后发给CPU释放脉冲,这三个脉冲都是负脉冲。另外,每次总线控制权改变后,总线上必须有一个空闲周期。即在一个时钟周期中,没有任何一个主模块使用总线。

⑤中断操作

中断:硬件中断、软件中断

硬件中断(外部中断):INTR可屏蔽中断、NMI不可屏蔽中断

软件中断(内部中断):INT n软中断、INTO溢出中断、除数为0中断、单步中断

中断向量:中断处理子程序的入口地址,每个中断类型对应一个中断向量

中断向量表位于内存的0-3FFH区域

下图是低地址在下,高地址在上(有点反常)

前5个是专用中断,除非屏蔽中断外,其他都是软件中断

类型5到类型31共27个中断为保留的中断,是提供给系统使用的

其余类型中断原则上可以用户自定义,但有些中断类型已有固定用途,比如21H中断是操作系统MS-DOS的系统调用,在Windows操作系统中仍有效

中断响应流程图

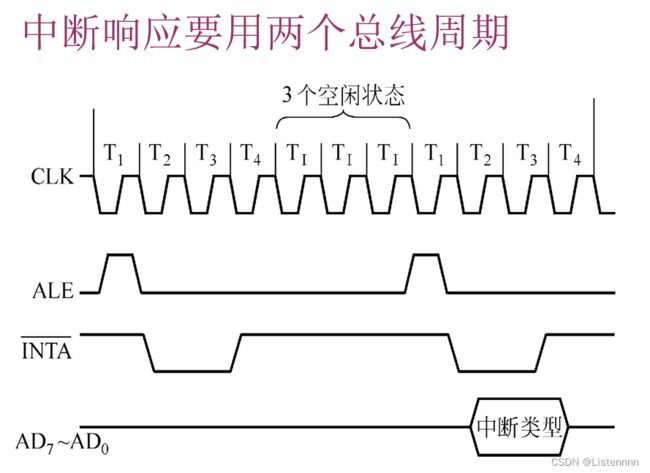

中断响应的总线周期

当响应一个可屏蔽中断时,CPU实际执行的总线时序如下:

第一步:执行2个中断响应周期,得到中断类型码

第二步:执行1个总线写周期,把标志寄存器入栈

第三步:标志寄存器中IF和TF置0

第四步:执行1个总线写周期,CS入栈

第五步:执行1个总线写周期,IP入栈

第六步:执行1个总线读周期,偏移量送IP寄存器

第七步:执行1个总线读周期,段地址送CS寄存器

如果是NMI或软件中断,则跳过第一步,从第二步开始按次序执行到第七步

五、8086的系统配置

1.8086在最小模式下的典型配置

除了CPU外,还需要哪些芯片来构成一个最小模式系统?这些芯片和CPU之间的连接关系是什么样的?

8284A时钟发生器、地址锁存器8282(或74LS373)、8286数据收发器(或74LS245)

2.8086在最大模式下的典型配置

最大模式配置和最小模式配置有一个主要的差别,就是在最大模式下,需要用外加电路来对CPU发出的控制信号进行变换和组合,以得到对存储器和IO端口的读写信号和对锁存器8282和对总线收发器8286的控制信号。8288总线控制器就是完成上面这些功能的专用芯片。8259A是中断优先级管理部件。使用8288后,就可以依据/S0,/S1,/S2的组合来提供相应的控制信号