数字 08 vivado的时序约束UI界面操作

实例 利用vivado的UI时序约束向导进行约束

打开工程,在implementation之后,点击如下选项

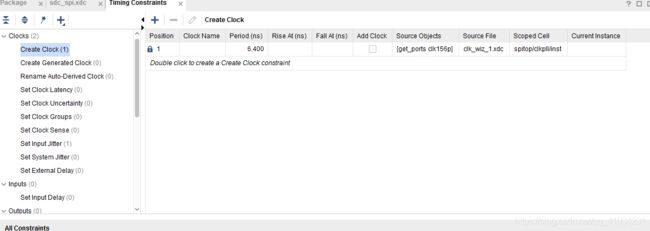

在什么都没有做的时候,时序约束UI界面里面是这样的

里面有一个主时钟clk156p,一个input jitter ,都是关于PLL的输入主时钟的,既然他已经做好了,而且我也明确的知道,这是一个port进来的主时钟,并且这个时钟是锁定住的,时钟约束的开头有个锁,所以我不能再对他进行操作。

所以我要在这基础上,进行我的时钟约束。

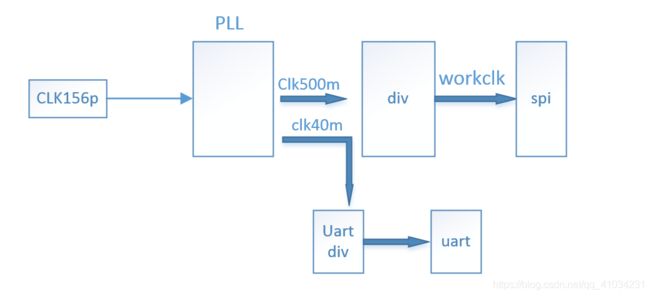

首先梳理我的时钟树

其实很简单,我需要约束的时钟是4个

1、主时钟clk156p

2、衍生时钟clk500m(我这里改成了300M)

3、衍生时钟clk40m

4、workclk是clk500m的分频(这里是300M的分频)

其中,1已经做好了,现在开始做第二个

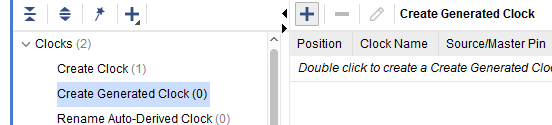

点击+号

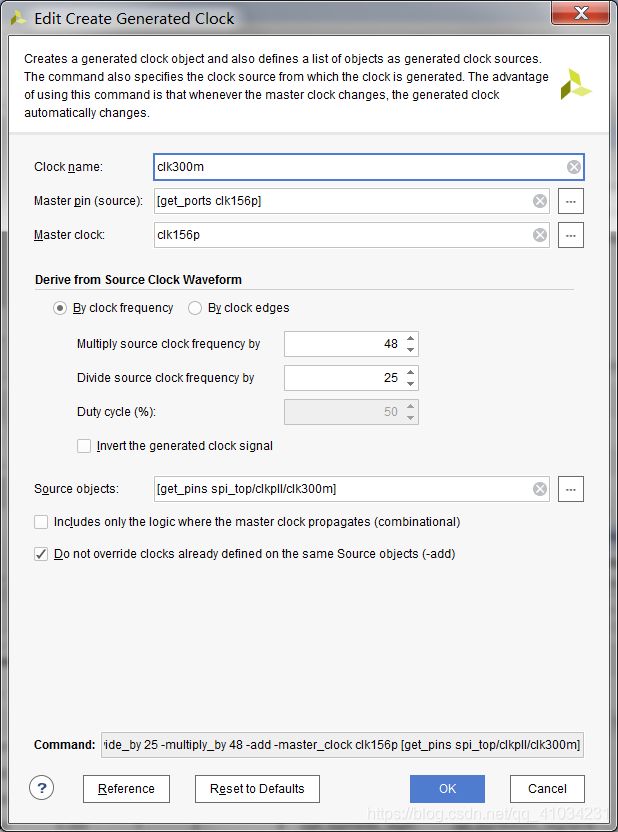

一项一项说明:

1、clock name是自己取的名字

2、Master pin是上级时钟的pin

3、Master clock是上级时钟

4、倍频和分频,我这里是300M,上级时钟是156.25M,所以,300/156.25=1.92=48/25,所以倍频48,分频25

5、source object 我这里选择了cell pins 搜索clk300m,找到对应得端口

6、把-add 打勾,表示是在原来的基础上添加衍生时钟

7、如果要invert反转自己的时钟,点击对应选项前面的打勾框

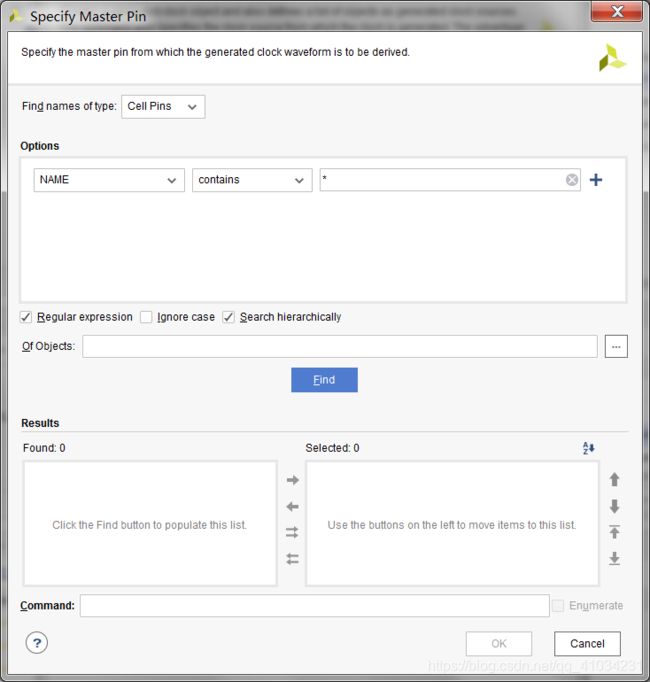

下面说明一下找cell pin之类的端口怎么搜

首先 Find names of type要选对,主时钟一般是port ,衍生时钟一般是net或者cell pins

然后在搜索框里输入名称,点击Find即可,在最下面两个框框里面将左边框正确的对象点击![]() 到右边框

到右边框

操作时界面如下

其他衍生时钟也是类似这样设置。

可以在tcl命令框里面输入report_clocks

查看时钟状态

约束xdc文件全文

set_property PACKAGE_PIN K28 [get_ports clk156p]

set_property PACKAGE_PIN M19 [get_ports rd]

set_property PACKAGE_PIN Y29 [get_ports rst_n]

set_property PACKAGE_PIN AA25 [get_ports spi_cs]

set_property PACKAGE_PIN AA27 [get_ports spi_miso]

set_property PACKAGE_PIN AB28 [get_ports spi_mosi]

set_property PACKAGE_PIN AB25 [get_ports spi_sck]

set_property IOSTANDARD LVDS_25 [get_ports clk156p]

set_property IOSTANDARD LVCMOS33 [get_ports rd]

set_property IOSTANDARD LVCMOS33 [get_ports rst_n]

set_property IOSTANDARD LVCMOS33 [get_ports spi_cs]

set_property IOSTANDARD LVCMOS33 [get_ports spi_miso]

set_property IOSTANDARD LVCMOS33 [get_ports spi_mosi]

set_property IOSTANDARD LVCMOS33 [get_ports spi_sck]

create_clock -period 6.400 -name clk156p -waveform {0.000 3.200} -add [get_ports clk156p]

create_generated_clock -name clk300m -source [get_ports clk156p] -divide_by 25 -multiply_by 48 -add -master_clock clk156p [get_pins spi_top/clkpll/clk300m]

create_generated_clock -name clk40m -source [get_ports clk156p] -divide_by 125 -multiply_by 32 -add -master_clock clk156p [get_pins spi_top/clkpll/clk40m]

create_generated_clock -name clk_divuart_out -source [get_pins spi_top/clkpll/clk40m] -divide_by 260 -add -master_clock clk40m [get_pins uart_top/clk_divuart/CLK]

create_generated_clock -name clk_divspi_out -source [get_pins spi_top/clkpll/clk300m] -multiply_by 1 -add -master_clock clk300m [get_pins spi_top/clk_divspi_out]

set_clock_groups -name asyn_uarttospi -asynchronous -group [get_clocks clk_divuart_out] -group [get_clocks clk300m]

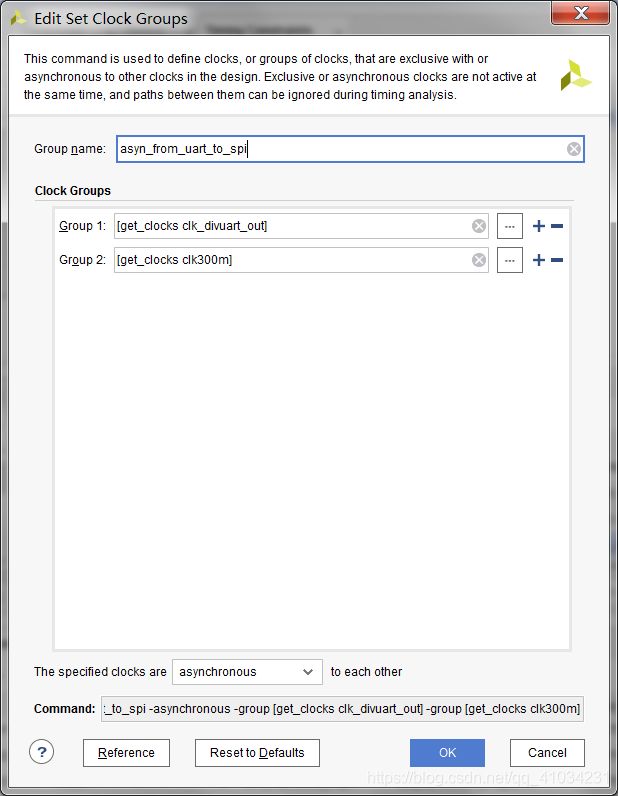

我这里有存在不同时钟域之间的数据交互,所以我做了一个set clock groups

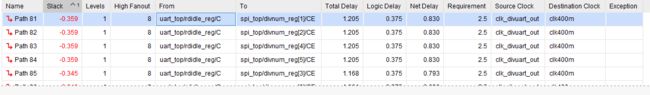

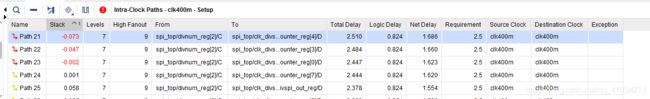

加异步时钟之前

可以看到最差的时序是由clk_divuart_out这个时钟到clk400m这里

set_clock_groups -name asyn_uarttospi -asynchronous -group [get_clocks clk_divuart_out] -group [get_clocks clk400m]

加上set_group_clocks

![]()

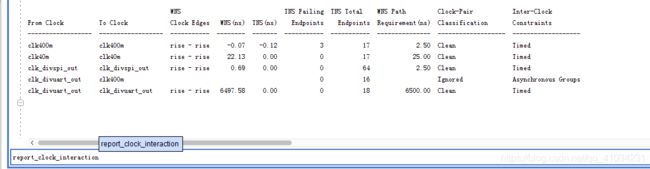

出现了一个严重warning,但是实际上这句语句确实起作用了,我的最差的时序现在已经不是在跨时钟域这里了

而是在400m单一时钟域里面了

并且最差的时序不是跨时钟域的数据交互了

使用report_clock_interaction命令查看,可以看到约束已经生效了

注意这里设置异步时钟组之后,对待这两个时钟域之间的状态是ignored

我在查找这个错误的时候发现有人这么说

BUT, I will issue my standard warning - the set_clock_groups command is dangerous. Due to constraint priority, it will override all other timing constraints on paths between the clocks, which can often under-constrain clock domain crossing (CDC) circuits, which leads to unreliable designs. Take a look at this post on constraining clock domain crossing circuits.

他说set_clock_groups这个命令是比较危险的、不可靠的,因为它会override(覆盖?)其他时序路径。(这个问题先存着,后续再继续研究)

有人在xilinx官网Q&A问了跟我类似的问题:

大意就是网友遇到了一样的问题,并且用TCL 命令确认了set_group_clocks后面跟着的时钟,是确实存在的,并且在TCL命令下,用set_group_clocks命令不会产生任何警告,所以很疑惑为什么implement之后会出现这个错误。

[Vivado 12-4739] set_clock_groups:No valid object(s) found for '-group [get_clocks

I am getting the following critical warning, however, I am not sure if it is safe to ignore it or not.... Because I believe the tool understands it.

My assumption is that probably it is an ordering issue, and the tool is trying to execute the tcl commands in a out of order fashion, and maybe that is why it results in this critical warning.

First off, in my RTL code, I made sure that the nets "clk_A" and "clk_B" are not going to be removed, by adding "KEEP" attribute, and I know that the tool didn't trim it, and everything is still there.

So, then in my XDC file, I have something like this:

set_clock_groups -asynchronous -group [get_clocks -of_objects [get_nets clk_A]] -group [get_clocks -of_objects [get_nets clk_B]]And, after the synthesis, I get the following critical warning:

[Vivado 12-4739] set_clock_groups:No valid object(s) found for '-group [get_clocks -of_objects [get_nets clk_B]]'. ["Z:/project/vivado/my_xdc.xdc":20]But here is what is interesting that happens:

after I open my synthesis design, I typed the followings, in the TCL console, here is what I get:

get_clocks -of_objects [get_nets clk_A]on the console it gets printed:

clkout1So, I know that the clocks for net "clk_A" exists....

Similarly, I typed the followings, in the TCL console, here is what I get:

get_clocks -of_objects [get_nets clk_B]on the console it gets printed:

clkout2So, the proper clocks for net "clk_B" also exists.

Additionally, when I type:

get_clocksI get this:

SYS_CLK_DDR4_P clkout0 clkout1 adc_dac_clk clkfbout clkout0_1 clkout2 clkout0_1_INTERNAL_DIVCLK FMC_C[GBTCLK0_M2C_P] qpll0outclk_out[0] qpll0outrefclk_out[0] rxoutclk_out[0] txoutclk_out[0]So, I know that clkout1 and clkout2 exist.....

And finally, when I type the entire tcl command:

set_clock_groups -asynchronous -group [get_clocks -of_objects [get_nets clk_A]] -group [get_clocks -of_objects [get_nets dc_B]]There is no warning or nothing strange printed on the TCL console. So, to me, these are all indicative of the fact that the tool properly interpreted the above TCL command, and everything is good to go....

However, after the synthesis is done, I get the critical warning message that I mentioned above, which is:

[Vivado 12-4739] set_clock_groups:No valid object(s) found for '-group [get_clocks -of_objects [get_nets clk_B]]'. ["Z:/project/vivado/my_xdc.xdc":20]That is why, I am not sure what is happening...!!!!

It this a bug in the tool, or there is something wrong with my tcl command?

Also, after the implementation, I get the exact same critical warning, which says:

[Vivado 12-4739] set_clock_groups:No valid object(s) found for '-group [get_clocks -of_objects [get_nets clk_B]]'. ["Z:/project/vivado/my_xdc.xdc":20]Any idea what is going on, and how to fix this issue?

算了既然生效了就不管了。

可以看到我在上面还有-0.073ns的时序违例,所以我决定去优化我的rtl代码,我去掉了一个减法器,时序又优化了一些。