【Vivado那些事儿】Vivado环境一览

前言

在我看来,用好一个工具的前提,就需要对工具有比较清晰的认识,不然对工具都不熟悉,遇到一些关乎工具上的问题时,会根本无从下手,也会在一定程度上影响项目的开发,所以很多时候,在进行一些项目的时候,团队里使用的开发工具的版本都会进行一定的统一,而不能一味的追求新版本,就是为了减少工具引起问题,从而提高项目进展速度。(PS:个人使用就看你自己的心情了)

工程直接使用的Example Project里的BFT那个,本篇主要对Vivado工程界面进行学习,其他的就不多说了,直接开始本篇的内容吧~

整体界面

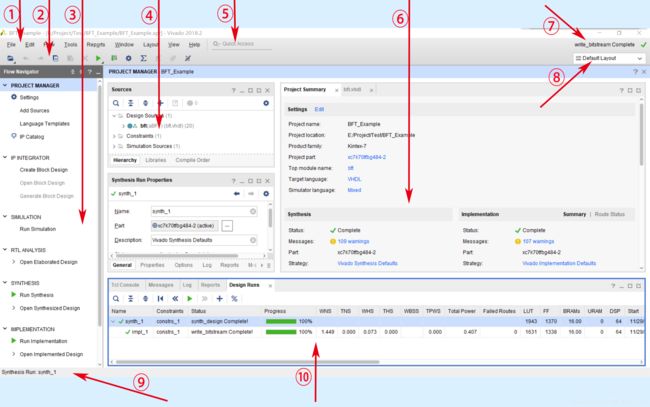

一个建好的工程,运行成功后的整体界面如下所示,就按以下的顺序进行学习,序号与图中界面一一对应。

1.菜单栏

2.工具栏

3.设计流程导航

4.源+属性+网表

5.快速访问搜索

6.工作空间

7.工程状态信息

8.布局选择器

9.提示

10.结果窗口

1.菜单栏

菜单栏中的选项就是对Vivado的一种直接操作的指令,常用的命令会始终显示(比如, File >Project > New Project ),而其他命令就需要活动状态下才会显示(比如,Reports > Report DRC),然后在一些选项后面还能看到快捷键,关于自定义快捷键的操作就后面的篇章再讲。

2.工具栏

该部分就是为了使用一些功能的时候方便些,把鼠标光标移到对应的工具图标上,会显示该图标的功能,如下。

3.设计流程导航

顾名思义,就是一个完整设计的流程导航,或者说是设计流程的向导,反正就是完成一整个设计会涉及到的东西,屏幕太小,需要看更多的内容,可以按那个右上角的”—“,也可以快捷键”Ctrl+Q“,接下来直接说下以下七个目录下都代表哪些功能或者是设计流程中的哪一项。

.Project Manager

该目录下具有几个功能,也是比较常用的,可改变工程的设置【Settings】,添加或新建源文件【Add Sources】,可以看官方提供的模板【Language Templates】,还能进入IP核的菜单【IP Catalog】,IP Catalog的相关,可以看官方文件:【UG896】Vivado Design Suite User Guide: Designing with IP

***Note:***搜寻文件可以在DOC Nav那个软件上找,或者在官网进行搜索,我就不放文件了,以下涉及到的亦如此。

.IP Integrator

IP集成器,具有创建,打开和生成模块的功能,即作用就是将你自己设计的具有某个功能的HDL文件配置成一个IP核,在设计中直接以IP核的形式进行使用,该目录主要就是针对这些自定义IP,如果还不会用这个的(System Generate系列有操作过…),可以参考官方文件:【UG994】Vivado Design Suite User Guide: Designing IP Subsystems Using IP Integrator

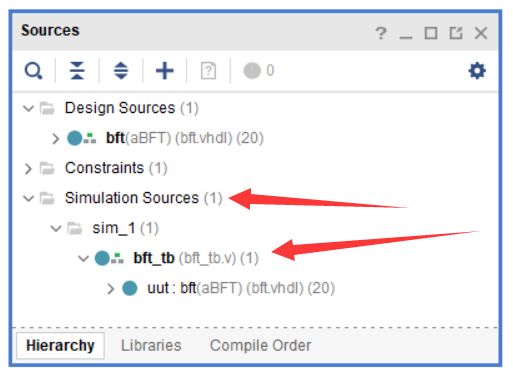

.Simulation

对该目录右键可以对仿真进行设置,该目录下的主要功能就是对设计文件进行仿真,仿真文件调用的是Source下Simulation Sources文件夹下的文件,激励文件需要设置为顶成即Top,才能正确仿真,如下,相关信息可参考:【UG900】Vivado Design Suite User Guide: Logic Simulation

.RTL Analysis

打开一个设计进行RTL分析,也就是将你的的设计文件以电路图的形式打开,也就是常说的RTL电路之类了,此外还可以运行设计规则的检查。

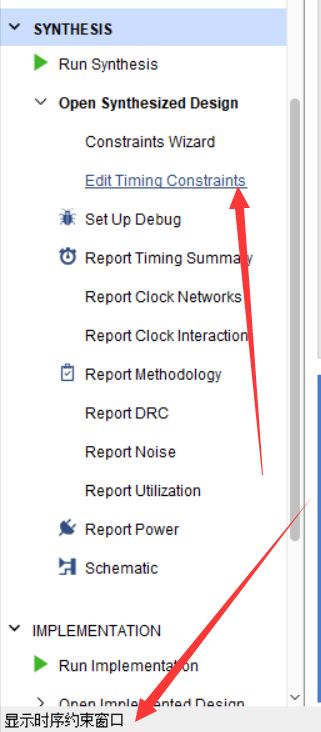

.Synthesis

具有几个功能:改变综合的设置,运行以及打开综合设计。Debug的选项也在此功能下,手动添加网络进行Debug就需要进行该综合的步骤,目录下还有一些向导和报告等等的选项,等下介绍了第9项,就可以自行领悟了~

Synthesis相关文件:【UG901】Vivado Design Suite User Guide: Synthesis

.Implementation

该部分的作用就是将综合后的网表实现,右键进行设置什么的和Synthesis的操作都一样,就不说了,需要了解更多的,参考:【UG904】Vivado Design Suite User Guide: Implementation

.Program and Debug

这个就很明显了,将实现的电路生成BIT文件,可下载进板卡中,如果有设置Debug的相关功能,就可以进入Debug的界面进行观察信号等等,该项的详细说明可参考:【UG908】Vivado Design Suite User Guide: Programming and Debugging

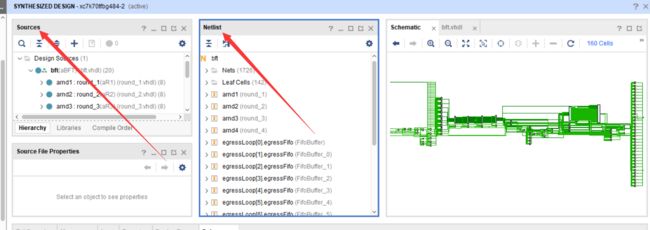

4.源+属性+网表

这个标题可能取得比较奇怪,我也不知道取个怎样的好,因为这个是由三个窗口组成,默认情况下只有两个:源【Sources】和属性【Properties】,网表【Netlist】则需要打开原理图后,才会显示。

【Sources】:包含四个子选项,Hierarchy(代码+约束), IP Sources(使用的IP核), Libraries(使用到的库)和 Compile Order(编译的顺序),其中,IP Sources只有在你使用了IP核的时候才会有。

【Properties】:将选定的逻辑目标(比如:某个.v文件)的信息或者器件资源进行显示

【Netlist】:打开原理图后,网络将有层次的在该窗口进行显示,如下所示,图的左边部分就是网表,右边就是实现的电路。

5.快速访问搜索

这个部分蛮好用的,就是将命令输入到这个框里面,会直接定位该命令,然后你就可以用了,当然,你只记得命令中的个别字母了也一样可以用,直接输入其中一个字母,然后它也会将搜到的命令进行展示(只要命令有这个字母),这样,总能找的你需要的那个命令了吧~

此外还能直接定位最近使用过的一些工程或者文件并打开。

有什么好处就自行体会了~

6.工作空间

叫工作空间,我也不知道合不合适,反正就是这么个意思,使用Vivado进行工作的主区间就是该部分窗口,IP核菜单、程序的编辑、工程概要、原理图等等,除了弹处的小窗口外,基本上都是在该空间中进行,截的图中只取了工程概要进行显示,但是别误会成该序号只是代表概要了。

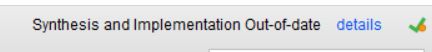

7.工程状态信息

该部分,可以看当前工程的状态,比如运行了综合或者之后的流程,就会出现Running XXX 的字样

完成就会有complete的字样

如果编译完后,修改了文件并保存了,就会出现xxx Out-of-data,点那个details会报出修改过的文件。

除了显示修改后的文件,还会有一个功能,就是右上角那个,强制更新,比如你只是不小心加了点空格啥的,就可以用这个功能,其他情况下用这个的话,就自己看着办了~

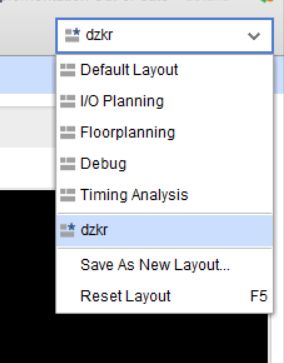

8.布局选择器

这个就是窗口的布局,使用的一般就是系统的预定义的布局了,如果想配一个适合自己使用习惯的窗口布局,就可以拖动小窗口到其他位置,简单举个例子,我把Sources和Netlist两个分开进行查看,,拆分前长这样:

拆分后:

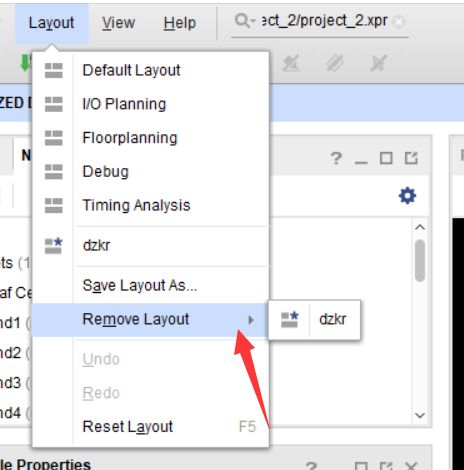

布局设置完成后,就需要保存设置,保持的话可以在Layout这个窗口下进行

也可在菜单栏中的Layout下进行

点击后,会让你给布局命名

保存后的Layout界面如下,之后在其他的工程时也依然可以用。

之后要是不小心变动了(关闭或者移动到其他位置取了)就可以使用Reset Layout,复位回指定的Layout。

如果又不想要这些布局了,可以直接在菜单下使用Remove

关于Layout下的那几个Layout都对应什么的,我就简单再补充下:

Default Layout:选定最少窗口的那个

I/O Planning:进行IO约束的界面

Floorplanning:可以查看物理约束+器件约束,还能管理分区以及分层布局等等

Debug:调试相关界面

Timing Analysis:查看时序分析报告,在界面底部。

除了以上的之外,还有一些布局,由于时间关系,就不多述了。

9.提示

这个也挺有用的,如果使用界面的某些功能时,不懂该选项的作用,鼠标光标移到选项位置,然后这个地方会有功能提示,告诉你,你选择的那个是什么功能,简单举个例子,直接看图:

10.结果窗口

运行命令,生成消息以及创建日志文件和报告文件时,相关信息将显示在该区域中,默认情况下是以下五个。

Tcl Console:输入Tcl控制命令的位置,可以看到已经运行的命令和输出

Messages:按类显示当前设计的信息

Log:运行日志

Reports:提供有效运行的报告

Designs Runs:管理当前工程的运行

结语

本篇的内容蛮细节化的,有很多东西也一下讲不完,由于时间关系(还是比较懒了点,hhhhh),我也就简单的略过了一些,更多的还是给了一个引导,不过我觉得看完前后的这两篇内容,对Vivado基本上也算是有足够的了解了,接下来的篇章就差不多可以直接开始上一些操作了,敬请期待吧~