MIPS CPU设计(基于华中科技大学计组实验)

来都来了给我点个赞收藏一下再走呗~~~

本次实验要求我们掌握的是MIPS CPU设计,而此实验中关注的重点是在计算机中的cpu的运行模式,这个模式可以参考冯诺伊曼的计算机架构去理解,还需要知道的是指令格式和指令在计算机中是如何解析的。

本实验要求我们掌握MIPS指令的格式,MIPS指令的解析,微程序的概念,控制器是如何控制指令的,还需要知道PC程序计数器有哪两种计数模式,状态转化,单周期和多周期的指令在cpu中是怎么执行指令的。

做本实验之前要求掌握的前提知识:

1. 单周期和多周期CPU的区别以及执行流程

2. MIPS指令格式

3. 微程序地址转移逻辑

4. 硬布线控制器状态转化控制

5. 多周期MIPS硬布线控制器CPU

实验需知:在做此实验之前我们需要知道的是如何通过使用实验包中给出的execl表格来进行电路的自动生成,我们需要知道的前提是在logisim的自动生成电路中不可以使用到复杂的逻辑门和复用器。

这个地方我举一个简单的例子,里面的execl表中的数据我就步在讲解只是告诉要如何使用到execl中生成的表达式在logisim中自动生成电路。

首先我们需要直接填写的部分如下所示:

如何我们就可以切换到自动生成表达式的表格中点击下面的自动生成:

![]()

我们点击logisim中的项目à分析电路à表达式à填写表达式à填写完构建电路:

第1关:单周期MIPS CPU设计

首先mips指令是分为了三种,如图4.1所示:

- R型指令格式为:op rd, rs, rt,shamt,funct其中op为操作码,rd为目标寄存器,rs和rt为源寄存器。R型指令主要用于寄存器的操作,如加减乘除、逻辑运算等。

- I型指令格式为:op rt, rs, imm,其中op为操作码,rt为目标寄存器,rs为源寄存器,imm为立即数。I型指令主要用于立即数的操作,如加载。

- J型指令格式为:op rs, imm,其中op为操作码,rs为源寄存器,imm为跳转地址。J型指令用于跳转操作。

图4.1:指令格式

我们可以根据指令的操作码op传送到控制器中就可以知道,当前控制的需要进行的操作是那一个,然后就是需要把Rs,Rt,Rd送到寄存器中,让寄存器在输出两个值,当不是J指令的时候我们就让PC计数器的值加上4,如果是J指令的时候就直接让PC计数器的值等于我们要跳转的地址,这个地方的值需要用到一个数据选择器实现。

具体的实现我们就可以直接找着实验中给出的数据通路进行电路图的设计了,实验给出的数据通路图如图4.2所示:

图4.2 数据通路示范

具体单周期mips的数据通路图,如图4.3所示:

图4.3:单周期MIPS电路图

在写硬布线控制器的时候我们需要知道实验要求我们使用的八种mips指令所对应的op码对应是多少我们就可以更具op传入的值和对应的操作码进行比较来决定是什么指令,指令对应op操作码值的表格如下所示:

| Mips指令 |

Op码 |

| Add(两个寄存器的值相加,并将结果存储在目标寄存器中。) |

000000 |

| Slt(比较两个寄存器的值,并将结果(0 或 1)存储在目标寄存器中)第一个小于第二个置1 |

000000 |

| ADDI(用于将一个立即数添加到目标寄存器的值中。) |

001000 |

| Lw(用于从内存中加载一个32位的字到目标寄存器中。) |

100011 |

| Sw(用于将一个32位的字从源寄存器存储到内存中。) |

101011 |

| Beq(比较两个寄存器的值,值相等,那么程序将跳转到指定的地址。) |

000100 |

| Bne(不相等跳转) |

000101 |

| Syscall(系统调用停机) |

000000 |

单周期的硬布线控制器如图4.4-4.5所示:

图4.4单周期的硬布线控制器

图4.5单周期的硬布线控制器

第2关:微程序地址转移逻辑设计

根据视频中给出的状态值对应的微指令地址,我们需要去填写execl表格,指令状态转化图如图4.6所示:

图4.6指令状态转化图

实现微程序地址转移逻辑的execl表如图4.7所示,我们只需要把地址逻辑自动生成的表达式放入logisim的自动生成中就可以得到微程序地址转移的电路图(部分)如图4.8所示:

图4.7 微程序地址转移逻辑的execl表

图4.8微程序地址转移逻辑电路图(部分)

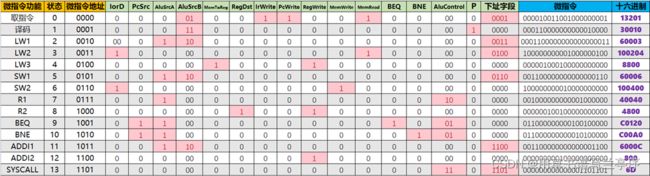

设计微程序控制器,把对应的八条控制指令的控制信号对应的有要这条控制信号的就把对应的信号设置为1,否则为0,控制信号的如图4.9所示:

图4.9:控制信号图

Execl表如图4.10所示:

图4.10 微指令功能微指令

现在就只需把上面的十六进制数复制到控制存储器中即可,结果如图4.11所示:

图4.11:控制寄存器数据

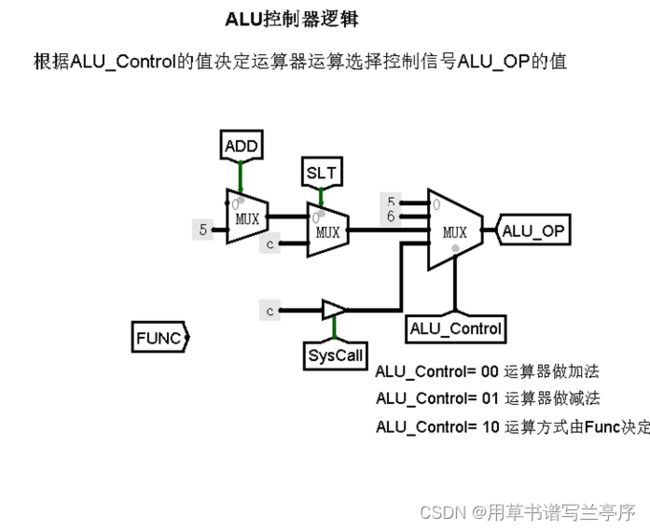

指令译码逻辑和运算器控制逻辑的电路图如图4.12所示:

图4.12 指令译码和运算器控制逻辑电路

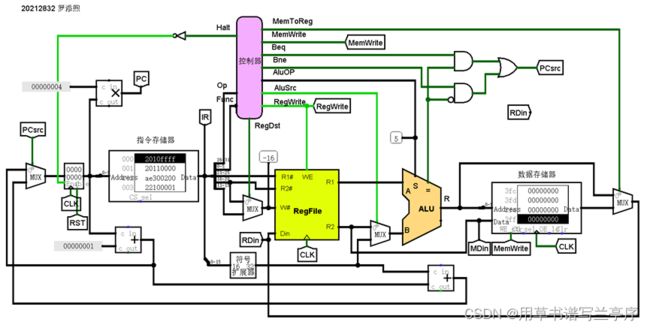

第3关:MIPS微程序CPU设计

也是可以根据视频中给出的多周期MIPS的数据通路的参考图就可以很容易的设计出,多周期MIPS的数据通路电路图如图4.13所示:

图4.13多周期MIPS的数据通路

第4关:硬布线控制器状态机设计

根据上面实验给出的状态转化图,可以填写出execl表,实现现态和次态的转化,execl的具体表格如图4.14所示:

图4.14 状态机状态转化execl表

逻辑表达式自动生成表格如图4.15所示:

图4.15 表达式自动生成

当前我们只需要把逻辑表达式放入logisim的自动生成电路中就会自动的帮我们生成如图4.16所示的电路(部分):

图4.16 状态机FSM电路(部分)

指令译码逻辑和运算器控制逻辑和微指令多周期的MIPS控制器中的是一样的如图4.17所示:

图4.17 指令和运算器逻辑电路图

第5关:多周期MIPS硬布线控制器 CPU设计(排序程序)

多周期的MIPSCPU就是在每一个的输出的时候都加一个寄存器用于寄存指令输出之类的,然后通过寄存器中的数据我们可以把单时钟信号变为多时钟信号,多时钟信号可以减小一个时钟周期的时间过长。

也是可以根据视频中给出的多周期MIPS(硬布线)的数据通路的参考图就可以很容易的设计出,多周期MIPS的数据通路电路图如图4.18所示:

图4.18 多周期MIPS硬布线控制器CPU设计电路图

多周期MIPS硬布线控制器CPU设计电路图清晰图: