[ECE] Fixed-Function Logic Gates

Programming Logic

Most types of programmable logic devices (PLDs) use some form of AND array.

An AND array consists of AND gates and a matrix of interconnections

For each input to an AND gate, only one programmable link is left intact in order to connect the desired variable to the gate input.

Fixed-Function Logic Gates

Fixed-function logic integrated circuits have been a staple in the realm of electronics for quite some time, offering a range of predefined logic functions. Unlike Programmable Logic Devices (PLDs), these integrated circuits come with functions that are hardcoded and cannot be altered or reprogrammed. Notably, the scale of logic in fixed-function ICs is smaller compared to what can be programmed into a PLD.

Despite the prevailing trend towards programmable logic, fixed-function logic finds its niche in specialized applications where PLDs may not be the most optimal choice. These devices are sometimes referred to as "glue logic" due to their role in connecting larger units of logic, such as PLDs, within a system.

固定功能逻辑集成电路在电子领域已经存在了很长时间,提供各种逻辑功能。与可编程逻辑器件(PLD)不同,固定功能集成电路具有无法编程或更改的逻辑功能。固定功能逻辑的规模远远小于可编程逻辑器件可以编程的逻辑规模。尽管技术趋势明显是朝着可编程逻辑的方向发展,但固定功能逻辑在专业应用中仍然发挥着作用,特别是在PLD不是最佳选择的情况下。固定功能逻辑器件有时被称为“胶水逻辑”,因为它们在连接系统中的较大逻辑单元(如PLD)时非常有用。

Key Takeaways:

-

List of Common 74 Series Gate Logic Functions:

- 74 series gate logic functions are prevalent in fixed-function logic devices.

-

Major Integrated Circuit Technologies:

- Two major categories of circuit technology for fixed-function logic devices are CMOS (Complementary Metal-Oxide Semiconductor) and bipolar (also known as TTL - Transistor-Transistor Logic).

-

Integrated Circuit Families:

- Various families of integrated circuits exist within these technologies.

-

Data Sheet Information:

- Understanding and obtaining information from data sheets is crucial for working with fixed-function logic devices.

-

Propagation Delay Time:

- This term refers to the time taken for a signal to travel through a circuit.

-

Power Dissipation:

- The amount of power consumed by the integrated circuit.

-

Unit Load and Fan-Out:

- Parameters that define the electrical load an output can drive and the number of inputs it can feed.

-

Speed-Power Product:

- A metric combining the speed and power characteristics of the device.

目前所有固定功能逻辑设备都分为两大类电路技术:互补金属氧化物半导体(CMOS)和双极(也称为TTL,晶体管-晶体管逻辑)。另一种极少数设备中可用的双极技术是发射结耦合逻辑(ECL)。双极CMOS(BiCMOS)是一种将双极和CMOS结合在一起的集成电路技术。CMOS是最主要的电路技术。

CMOS (Complementary Metal-Oxide Semiconductor)

Bipolar (TTL, Transistor-Transistor Logic)

74 Series Logic Gate Functions

Performance Characteristics and Parameters

Propagation Delay Time

The terms low speed and high speed, applied to logic circuits, refer to the propagation delay time. The shorter the propagation delay, the higher the switching speed of the circuit and thus the higher the frequency at which it can operate.

Propagation delay time, tP, of a logic gate is the time interval between the transition of an input pulse and the occurrence of the resulting transition of the output pulse. There are two different measurements of propagation delay time associated with a logic gate that apply to all the types of basic gates.

• tPHL: The time between a specified reference point on the input pulse and a corresponding reference point on the resulting output pulse, with the output changing from the HIGH level to the LOW level (HL).

• tPLH: The time between a specified reference point on the input pulse and a corresponding reference point on the resulting output pulse, with the output changing from the LOW level to the HIGH level (LH).

For the HCT family CMOS, the propagation delay is 7 ns, for the AC family it is 5 ns, and for the ALVC family it is 3 ns. For standard-family bipolar (TTL) gates, the typical propagation delay is 11 ns and for F family gates it is 3.3 ns. All specified values are dependent on certain operating conditions as stated on a data sheet

| Term | Definition |

|---|---|

| Low Speed | Refers to a longer propagation delay time in logic circuits, resulting in a lower switching speed and a lower operating frequency. |

| High Speed | Indicates a shorter propagation delay time in logic circuits, leading to a higher switching speed and a higher operating frequency. |

| Propagation Delay | Time interval between the transition of an input pulse and the occurrence of the resulting transition of the output pulse. |

| tPHL | Propagation delay time from a specified reference point on the input pulse to a corresponding reference point on the resulting output pulse, with the output changing from HIGH to LOW. |

| tPLH | Propagation delay time from a specified reference point on the input pulse to a corresponding reference point on the resulting output pulse, with the output changing from LOW to HIGH. |

| HCT Family (CMOS) | Propagation delay: 7 ns. |

| AC Family (CMOS) | Propagation delay: 5 ns. |

| ALVC Family (CMOS) | Propagation delay: 3 ns. |

| Standard Bipolar | Typical propagation delay for TTL gates: 11 ns. |

| F Family (Bipolar) | Propagation delay for F family gates: 3.3 ns. |

| Operating Conditions | Specified values are dependent on certain operating conditions as stated on a data sheet. |

DC Supply Voltage (VCC) &Input and Output Logic Levels

| Parameter | 5 V CMOS | 3.3 V CMOS | Bipolar Logic |

|---|---|---|---|

| DC Supply Voltage (VCC) | 5 V, 3.3 V, 2.5 V, 1.8 V | 2 V to 3.6 V | 5.0 V (Min: 4.5 V, Max: 5.5 V) |

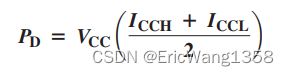

| Power Dissipation (PD) | Varies with ICCH and ICCL | Varies with ICCH and ICCL | Independent of Frequency |

| Input LOW Level Voltage (VIL) | 1.5 V (max) | Not specified | 0.8 V (max) |

| Input HIGH Level Voltage (VIH) | 3.5 V (min) | Not specified | 2 V (min) |

| Output LOW Level Voltage (VOL) | 0.33 V (max) | Not specified | 0.4 V (max) |

| Output HIGH Level Voltage (VOH) | 4.4 V (min) | Not specified | 2.4 V (min) |

| Speed-Power Product (SPP) | tpPD (joules) | tpPD (joules) | tpPD (joules) |

Power Dissipation

Speed-Power Product (SPP)

This parameter (speed-power product) can be used as a measure of the performance of a logic circuit taking into account the propagation delay time and the power dissipation. It is especially useful for comparing the various logic gate series within the CMOS and bipolar technology families or for comparing a CMOS gate to a TTL gate. The SPP of a logic circuit is the product of the propagation delay time and the power dissipation and is expressed in joules (J), which is the unit of energy. The formula is

Fan-Out and Loading

Fan-out : the maximum number of gate inputs driven by the output of another single gate.

Fan-out is specified in terms of unit loads

![[ECE] Fixed-Function Logic Gates_第1张图片](http://img.e-com-net.com/image/info8/95e5396a9a2f4fffbd9bb7f6a0b79e77.jpg)

![[ECE] Fixed-Function Logic Gates_第2张图片](http://img.e-com-net.com/image/info8/8358d048556a4d958b3c6711184d699d.jpg)

![[ECE] Fixed-Function Logic Gates_第3张图片](http://img.e-com-net.com/image/info8/95f0897532c94664a7535479244ed61c.jpg)

![[ECE] Fixed-Function Logic Gates_第4张图片](http://img.e-com-net.com/image/info8/e96f877958cc43a2bae8736c154dd49f.jpg)