2011大学生电子设计竞赛E题——数字锁相环实现

作者:林子木

有人跟我说,今年的电子设计竞赛E题,可以用锁相环来做。我看了下晚上的10篇文章,最后我都打包在了csdn,网址如下http://download.csdn.net/detail/wolinxuebin/3615889

首先提一点,有人想,不做其他处理,直接就可以用锁相环锁住,不大可能实现,因为范围太广了,想从10k到100k直接锁住,完全不可能,且看下面的分析。

撇开很多计算,大致讲下思路,首先DPLL的组成是鉴相器、环路滤波器、压控振荡器

一、鉴相器

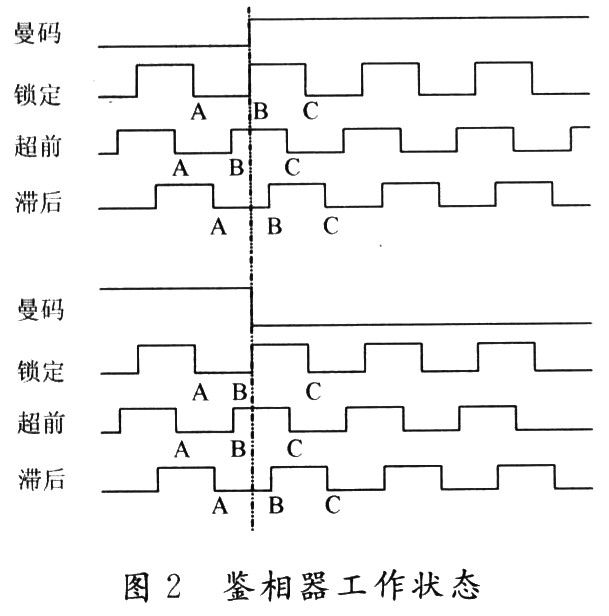

如图2 ,A、B、C点怎么看呢?是的,直接看如上面图中的超前的那个波形,A点时,曼码为0;B点时,曼码为0;C点时,曼码为1。

这样看,会看了之后,我们发现下图的公式就好理解了。

Sign_ready的作用是,检测时候在跳变点,指的是曼码的跳变点哦。

两者同时成立才能。

二、环路滤波器

在模拟锁相环里面,环路滤波器就是低通滤波器,滤除鉴相器出来的高频分量。DPLL中,就更简单了,如下图

就是一个模为M的一个计数器,因为相位有超前、也有滞后,所以计数器应该是可加可减的,sign=1 上面已经知道了,那是超前了,那么计数器就加1,否则减去1。

对了,提下,这个是用来滤波的,其实简单的来说,就是为了避免噪声引起抖动,噪声是不确定的,引起的抖动是可上可下的。一般将初始的数值设为M/2。

当Sign为1时,表示本地时钟超前于输入信号,Mod做加法计数,逐次加法直到15,进位变为8,Inset输出一个1μs的高电平;同样,当Sign为0时,表示本地时钟超前于输入信号,Mod做减法计数,逐次加法直到1,借位变为8,Deduct输出一个1μs的高电平。

这个M设置也是有讲究的,模值M 对DPLL 的性能指标有着显著的影响,可自行设定.加大模值M,有利于提高DPLL的抗噪能力,但是会导致较大的捕捉时间和较窄的捕捉带宽;减小模值M 可以缩短捕捉时间,扩展捕捉带宽,但是降低了DPLL的抗噪能力。

三、压控振荡器

相位怎么调?给下款图,贴下代码

给一个代码:

if(elkin'event and clkin= l )then

if deduct= '1' then

count:= count+2;%滞后了,使其超前,为什么加2?下面告诉你

elsif insert='1' then

count:=count;%超前了,使其滞后,为嘛相等,而不是减1,因为如果去掉这两个信号,那么这个就是简单的一个分频器呀,所以它本身就是一直在加的,所以不加就等于减掉了嘛(这个太白了,自己回到的都觉得)

else

count:=count+1;

end if;

if(count< 8)then %这里不一定是8哦,如果是8那么50M/16=3125kHz呀

clkout< = '1';

else

clkout< ='0';

end if;

end if;

到这里,数字滤波器就这么讲完了。

写到这里,我想说的是,很违心,因为还没有解决E题的要求,所以必须还要解决一个问题,那就是大致知道输入信号的频率,这个比较近简单,做过频率计的同学应该知道。这里还需要小小的鉴别下,那就是找到里面最宽的那个,就是信号的时钟,由于信号速率是已知的,那就可以实现了。加上这样一个东西,改变最后的那个压控振荡器中的count的值(例程中是8)。

那么就这样的解决了。