PCI 学习笔记

一、PCI配置空间

PCI总线体系结构图

![]PKSCS9H[CBB[Z7Z9}$R@)J.jpg wKioL1MdazXyMtoRAAENr6z98gk010.jpg](http://s3.51cto.com/wyfs02/M01/22/5B/wKioL1MdazXyMtoRAAENr6z98gk010.jpg)

PCI有三个相互独立的物理地址空间:设备存储器地址空间、I/O地址空间和配置空间。配置空间是PCI所特有的一个物理空间。由于PCI支持设备即插即用,所以PCI设备不占用固定的内存地址空间或I/O地址空间,而是由操作系统决定其映射的基址。

系统加电时,BIOS检测PCI总线,确定所有连接在PCI总线上的设备以及它们的配置要求,并进行系统配置。所以,所有的PCI设备必须实现配置空间,从而能够实现参数的自动配置,实现真正的即插即用。

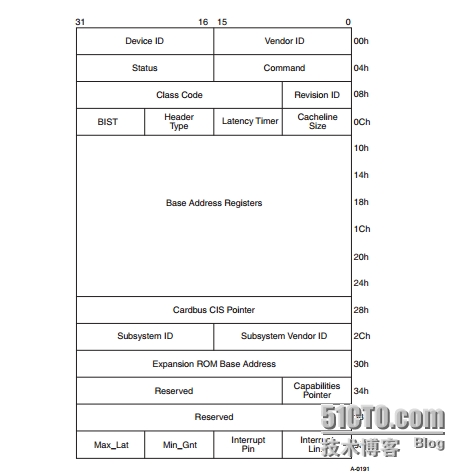

PCI总线规范定义的配置空间总长度为256个字节,配置信息按一定的顺序和大小依次存放。前64个字节的配置空间称为配置头,对于所有的设备都一样,配置头的主要功能是用来识别设备、定义主机访问PCI卡的方式(I/O访问或者存储器访问,还有中断信息)。其余的192个字节称为本地配置空间,主要定义卡上局部总线的特性、本地空间基地址及范围等。

一般PCI配置空间格式:

配置空间中最重要的有:

Vendor ID:厂商ID。知名的设备厂商的ID。FFFFh是一个非法厂商ID,可它来判断PCI设备是否存在。

Device ID:设备ID。某厂商生产的设备的ID。操作系统就是凭着 Vendor ID和Device ID 找到对应驱动程序的。

Revison ID:设备具体修改标识符

Header Type:这个字节识别预定义的第二部分的布局。BIT7确定一个多功能设备,1:多功能;0:单一。

Class Code:类代码。共三字节,分别是 类代码、子类代码、编程接口。类代码不仅用于区分设备类型,还是编程接口的规范,这就是为什么会有通用驱动程序。

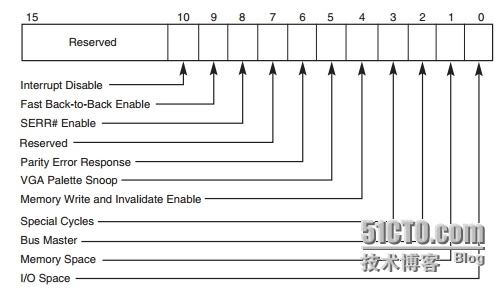

Command:2字节寄存器,寄存器结构如图:

Bit15-Bit11 and Bit7保留,Bit10 中断使能,1禁止,0允许,初始时为0。

Bit9:可读写位,控制a master是否可以对不同的设备进行快速连续的处理。1允许,0禁止,一 般初始化时为0。

Bit8:这是使能SERR# driver 0值禁止,1值允许。只要有SERR# driver的设备必须对这个寄存器 进行配置。初始化后置为0,此Bit和Bit6都为1时可以报告地址的奇偶检验错误。

Bit6:控制设备是否回应奇偶校验错误。设置成1时,当设备检测当错误时必须执行正常的动 作;设置成0时,当设备检测到错误时,设备将置奇偶检验状态位,但不assert PERR#并继续正常 操作。(太多了详情参考《PCI Local Bus Specification》第六章)

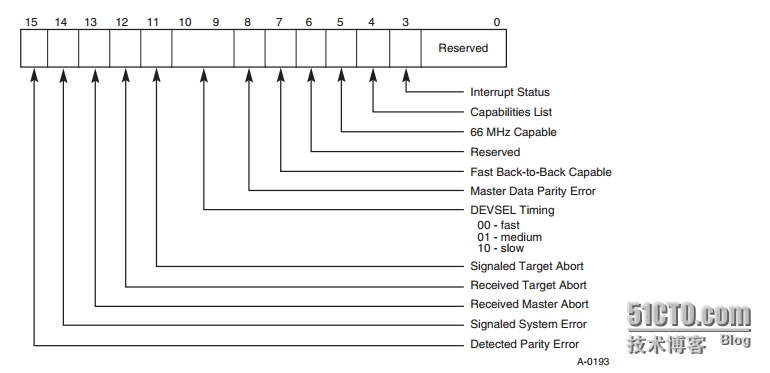

Status:2字节寄存器,寄存器结构如图:

Bit0-Bit2 保留

Bit3:中断状态标志位

IRQ Line:IRQ编号。PC机以前是靠两片8259芯片来管理16个硬件中断。现在为了支持对称多处理器,有了APIC(高级可编程中断控制器),它支持管理24个中断。

IRQ Pin:中断引脚。PCI有4个中断引脚,该寄存器表明该设备连接的是哪个引脚。

(太多了详情参考《PCI Local Bus Specification》第六章)

二、访问配置空间

1、Commands

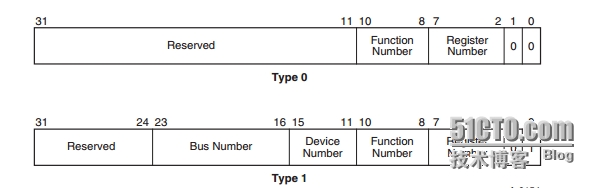

由于一个总线上可以分割的段是一定的,为了让系统拥有更多的设备,PCI-to-PCI bridge被提出来。PCI-to-PCI bridge需要一种机制来访问bridge后边的设备,为了支持这种机制Command就存在两种形式。如下图所示;

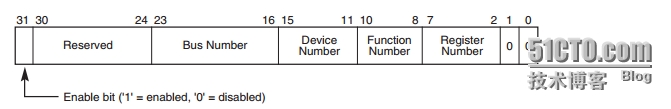

Type1与Type0的区别在于Bit0和Bit1,Bit0与Bit1的值为00时,选择当前总线上的一个设备,置为01时,选择另外一条总线上的设备。

Register Number:用来选择已选定目标的配置空间中一个DWORD

Function Numbei:用来选择一个多功能设备中的一个功能(值0-7)

Device Number:用来选择选定的bus中一个设备(值0-31)

Bus Number:用来选定一个bus

2、访问配置空间的方法

IO端口访问:地址端口0xcf8和数据端口0xcfc

忘地址端口写的地址格式,后两位必须为00,Bit31为使能位,要想读配置空间的数据,此位必须置1

定义一个unsigned long address 则

address = 0X80000000 | (Bus Number<<16) | (Device Nmuber<<11) | (Function Number<<8)

unsigned long Date (32位)

往端口写地址:

mov eax,address

mov dx,0xcf8

out da,eax

读出端口数据:

mov dx,0xcfc

in eax,da

mov Date,eax