ISE中IPcore调用之DCM

Xilinx ISE中的IP核生成器叫Core Generator ,而锁相环 PLL 所对应的 IPcore 在 ISE 中叫 DCM (digital clock management) ,它的主要功能是精准的生成由输入时钟经过相移、分频等操作得到的时钟 。下面是ISE 中调用DCM 的步骤。

1.右键自己的工程,单击 new source 后选择 IP core ,并添加名字

2.选择FPGA Features and Design->Clocking->Spartan-3E,Spartan-3A->Single DCM_SP

3. 根据自己的需求选择引脚(在相应的引脚后面打钩即可),下面各个引脚对应的功能:

CLKIN:输入时钟

CLKFB:反馈时钟,主要是用于补偿延时‘输出;分内部反馈和外部反馈

RST:复位信号

PSEN:phase shift enabled,移相使能

PSINCDEC:移相增减

PSCLK:移相时钟

CLK0~CLK270:分别为对输入移相0~270°输出

CLKDV:分频输出,分配系数下面可以设置

CLK2X/180:2倍频/反相输出

CLKFX/180:频率合成/反相输出,即分数M/N倍输入的时钟输出,M,N设置在NEXT步骤里会有提到

STATUS:8位输出总线,[2:0]有效,[7:3]悬空。STATUS[0] indicates the overflow of the phase shift numerator and that the absolute delay range of the phase shift delay line is exceeded. STATUS[1] indicates the loss of the input clock, CLKIN, to the DCM. STATUS[2] indicates that CLKFX has stopped.

PSDONE:移相结束标识

另外:在下面Advanced选项里有个Devide input clock by 2,意思是将输入时钟2分频后再作为输入时钟,即prescaler

注意:DLL_FREQUENCY_MODE and DFS_FREQUENCY_MODE属性默认为LOW,并且在Spartan-3E和3A器件中无法更改其属性。在其它器件中,设置该属性为高,DCM只有CLK0,CLK180,CLKDV和LOCKED有效

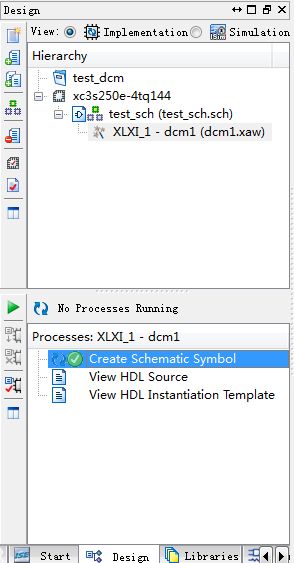

4.如果是采用原理图的输入方法,单击生成的DCM后双击下面的 creat schematic symbol ,即可在原理图调用该器件 ,如果是用vlog的输入方法,直接做例化即可。