OpenRisc-58-ORPSoC调试环境的构建

引言

之前我们在PC上构建了ORPSoC的仿真环境,通过仿真环境,我们可以观察任何模块的工作波形,极大的方便了问题定位和错误分析。但是,“是骡子是马,拉出来溜溜”,只能看看仿真波形显然还不过瘾,我们还需要用FPGA板子跑一边才行。但要想在板子上运行和调试软件,最方便最直接的方式就是用gdb将程序load到内存,进行调试运行。本小节就以ML501板子为例来说明OpenRISC调试系统的构建过程。

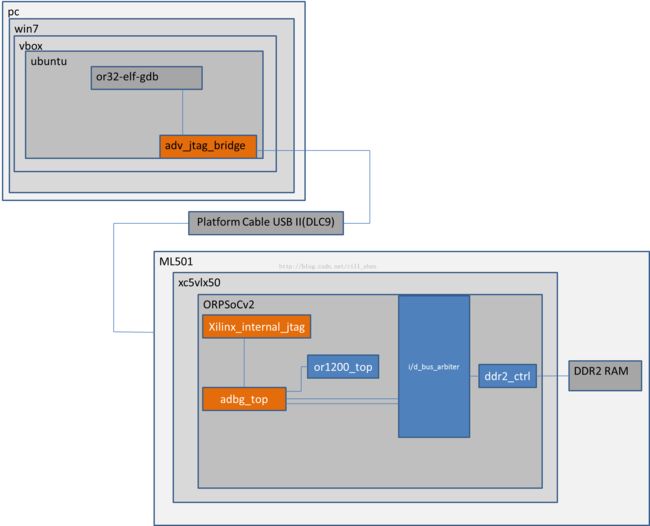

1, 调试系统结构

其中棕色模块来自advanced debug system,PC端用的是orpsoc的vox的ubuntu镜像,蓝色模块来自ORPSoCv2 for ML501。

2, 资源准备

a,Ubuntu镜像

http://opencores.org/or1k/Ubuntu_VirtualBox-image_updates_and_information

b,adv_debug_sys

http://opencores.org/project,adv_debug_sys

c,ML501板子及下载器。

http://www.xilinx.com/products/boards-and-kits/HW-V5-ML501-UNI-G.htm

3, 调试环境的构建

1> 安装adv_jtag_bridge

解压:

tar xvf adv_debug_sys_latest.tar.gz

安装:

cd adv_debug_sys/trunk/Software/adv_jtag_bridge ./autogen.sh ./configure ./make ./sudo make install

2> 在windows下构建ORPSOC针对ML501的ISE工程

ORPSOCv2的工程有两种方式,一种是在linux下,另外一种是在windows下。

linux下的工程,前面已经介绍过了:http://blog.csdn.net/rill_zhen/article/details/16880801

安装完ISE之后,就可以综合了。

下面介绍windows下的综合,

首先根据linux下的ise的prj文件,将对应的所有文件copy到windows下。

prj文件内容如下:

orpsoc.prj:

verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/arbiter/arbiter_bytebus.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/arbiter/arbiter_dbus.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/arbiter/arbiter_ibus.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/clkgen/clkgen.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/gpio/gpio.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/lfsr/lfsr.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/orpsoc_top/orpsoc_top.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_chipscope.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_ctrl.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_idelay_ctrl.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_infrastructure.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_mem_if_top.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_mig.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_phy_calib.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_phy_ctl_io.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_phy_dm_iob.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_phy_dq_iob.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_phy_dqs_iob.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_phy_init.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_phy_io.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_phy_top.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_phy_write.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_top.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_usr_addr_fifo.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_usr_rd.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_usr_top.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/ddr2_usr_wr.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/xilinx_ddr2_if_cache.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/xilinx_ddr2_if.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ddr2/xilinx_ddr2.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../rtl/verilog/xilinx_ssram/xilinx_ssram.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/cfi_ctrl/cfi_ctrl_engine.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/cfi_ctrl/cfi_ctrl.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/dbg_if/dbg_cpu_registers.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/dbg_if/dbg_cpu.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/dbg_if/dbg_crc32_d1.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/dbg_if/dbg_if.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/dbg_if/dbg_register.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/dbg_if/dbg_wb.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_clockgen.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_crc.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_fifo.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_maccontrol.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_macstatus.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/ethmac.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_miim.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_outputcontrol.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_random.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_receivecontrol.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_registers.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_register.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_rxaddrcheck.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_rxcounters.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_rxethmac.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_rxstatem.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_shiftreg.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_spram_256x32.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_transmitcontrol.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_txcounters.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_txethmac.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_txstatem.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/eth_wishbone.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ethmac/xilinx_dist_ram_16x32.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/i2c_master_slave/i2c_master_bit_ctrl.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/i2c_master_slave/i2c_master_byte_ctrl.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/i2c_master_slave/i2c_master_slave.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/intgen/intgen.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/jtag_tap/jtag_tap.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_alu.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_amultp2_32x32.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_cfgr.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_cpu.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_ctrl.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_dc_fsm.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_dc_ram.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_dc_tag.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_dc_top.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_dmmu_tlb.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_dmmu_top.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_dpram_256x32.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_dpram_32x32.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_dpram.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_du.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_except.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_fpu_addsub.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_fpu_arith.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_fpu_div.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_fpu_fcmp.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_fpu_intfloat_conv.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_fpu_mul.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_fpu_post_norm_addsub.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_fpu_post_norm_div.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_fpu_post_norm_intfloat_conv.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_fpu_post_norm_mul.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_fpu_pre_norm_addsub.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_fpu_pre_norm_div.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_fpu_pre_norm_mul.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_fpu.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_freeze.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_genpc.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_gmultp2_32x32.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_ic_fsm.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_ic_ram.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_ic_tag.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_ic_top.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_if.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_immu_tlb.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_immu_top.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_iwb_biu.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_lsu.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_mem2reg.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_mult_mac.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_operandmuxes.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_pic.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_pm.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_qmem_top.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_reg2mem.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_rfram_generic.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_rf.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_sb_fifo.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_sb.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_spram_1024x32_bw.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_spram_1024x32.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_spram_1024x8.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_spram_128x32.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_spram_2048x32_bw.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_spram_2048x32.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_spram_2048x8.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_spram_256x21.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_spram_32_bw.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_spram_32x24.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_spram_512x20.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_spram_64x14.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_spram_64x22.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_spram_64x24.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_spram.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_sprs.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_top.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_tpram_32x32.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_tt.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_wb_biu.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_wbmux.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/or1200/or1200_xcv_ram32x8d.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ram_wb/ram_wb_b3.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/ram_wb/ram_wb.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/rom/rom.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/simple_spi/fifo4.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/simple_spi/simple_spi.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/smii/smii_if.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/smii/smii_sync.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/smii/smii.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/uart16550/raminfr.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/uart16550/uart16550.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/uart16550/uart_debug_if.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/uart16550/uart_receiver.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/uart16550/uart_regs.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/uart16550/uart_rfifo.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/uart16550/uart_sync_flops.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/uart16550/uart_tfifo.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/uart16550/uart_transmitter.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/uart16550/uart_wb.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/directControl.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/dpMem_dc.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/endpMux.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/fifoMux.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/fifoRTL.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/getPacket.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/HCTxPortArbiter.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/hostcontroller.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/hostSlaveMuxBI.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/hostSlaveMux.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/lineControlUpdate.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/processRxBit.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/processRxByte.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/processTxByte.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/readUSBWireData.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/RxfifoBI.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/RxFifo.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/rxStatusMonitor.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/SCTxPortArbiter.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/sendPacketArbiter.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/sendPacketCheckPreamble.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/sendPacket.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/SIEReceiver.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/SIETransmitter.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/slavecontroller.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/slaveDirectControl.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/slaveGetPacket.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/slaveRxStatusMonitor.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/slaveSendPacket.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/SOFController.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/SOFTransmit.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/speedCtrlMux.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/TxfifoBI.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/TxFifo.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/updateCRC16.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/updateCRC5.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/USBHostControlBI.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/usbHostControl.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/usbhostslave.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/usbhost.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/usbSerialInterfaceEngine.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/USBSlaveControlBI.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/usbSlaveControl.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/usbslave.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/USBTxWireArbiter.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/wishBoneBI.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/usbhostslave/writeUSBWireData.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/wb_ram_b3/wb_ram_b3.v verilog work /home/openrisc/soc-design/orpsocv2/boards/xilinx/ml501/syn/xst/run/../../../../../../rtl/verilog/wb_switch_b3/wb_switch_b3.v

此外还要将以下文件copy到windows下:

bootrom.v,ml501.ucf,xilinx_ddr2_if_cache.ngc,synthesis-defines.v,timescale.v。

这些文件都可以在~/soc-design/orpsocv2/boards/xilinx目录下找到。

orpsoc.prj文件,在安装ISE之后,综合时会自动生成。

所有文件准备好之后,在windows下,打开ISE,创建一个工程(需要设置芯片型号等信息),将上面所有的文件加入工程即可。

需要注意的是bootrom.v的生成,一定要指令ML501对应的board.h。

3> 例化xilinx_internal_jtag

orpsoc中默认使用的是单独的jtag tap,我们使用xilinx_internal_jtag。

将adv_debug_sys\trunk\Hardware\xilinx_internal_jtag\rtl\verilog中的两个文件加到ISE工程里面,然后修改orpsoc_top.v,例化之。

在例化之前要先修改:

xilinx_internal_jtag.v:由于ml501板子本身就有4个jtag device(0,1,2,3),所以我们的device id要设置成4。

// May be 1, 2, 3, or 4 // Only used for Virtex 4/5 devices parameter virtex_jtag_chain = 4;

xilinx_internal_jtag_options.v:

//`define SPARTAN2 //`define SPARTAN3 // This is also used for SPARTAN 3E devices //`define SPARTAN3A //`define VIRTEX //`define VIRTEX2 // Also used for the VIRTEX 2P //`define VIRTEX4 `define VIRTEX5

例化:orpsoc_top.v:

`ifdef JTAG_DEBUG

////////////////////////////////////////////////////////////////////////

//

// JTAG TAP

//

////////////////////////////////////////////////////////////////////////

//

// Wires

//

wire dbg_if_select;

wire dbg_if_tdo;

wire jtag_tap_tdo;

wire jtag_tap_shift_dr, jtag_tap_pause_dr,

jtag_tap_upate_dr, jtag_tap_capture_dr;

//

// Instantiation

//

wire xilinx_internal_jtag_clk;

wire xilinx_internal_jtag_rst;

xilinx_internal_jtag xilinx_internal_jtag_rill

(

.tck_o (xilinx_internal_jtag_clk),

.debug_tdo_i (dbg_if_tdo),

.tdi_o (jtag_tap_tdo),

.test_logic_reset_o (xilinx_internal_jtag_rst),

.run_test_idle_o (),

.shift_dr_o (jtag_tap_shift_dr),

.capture_dr_o (jtag_tap_capture_dr),

.pause_dr_o (jtag_tap_pause_dr),

.update_dr_o (jtag_tap_update_dr),

.debug_select_o (dbg_if_select)

);

/*

jtag_tap jtag_tap0

(

// Ports to pads

.tdo_pad_o (tdo_pad_o),

.tms_pad_i (tms_pad_i),

.tck_pad_i (dbg_tck),

.trst_pad_i (async_rst),

.tdi_pad_i (tdi_pad_i),

.tdo_padoe_o (tdo_padoe_o),

.tdo_o (jtag_tap_tdo),

.shift_dr_o (jtag_tap_shift_dr),

.pause_dr_o (jtag_tap_pause_dr),

.update_dr_o (jtag_tap_update_dr),

.capture_dr_o (jtag_tap_capture_dr),

.extest_select_o (),

.sample_preload_select_o (),

.mbist_select_o (),

.debug_select_o (dbg_if_select),

.bs_chain_tdi_i (1'b0),

.mbist_tdi_i (1'b0),

.debug_tdi_i (dbg_if_tdo)

);*/

////////////////////////////////////////////////////////////////////////

`endif // `ifdef JTAG_DEBUG

4> 例化adbg_top

同样,orpsocv2中使用的dbg_if也需要替换成adv_debug_sys中的adbg_top。

将adv_debug_sys\trunk\Hardware\adv_dbg_if\rtl\verilog目录下的文件加到ISE工程,修改orpsoc_top.v例化之。

`ifdef JTAG_DEBUG

////////////////////////////////////////////////////////////////////////

//

// OR1200 Debug Interface

//

////////////////////////////////////////////////////////////////////////

adbg_top dbg_if0

(

// OR1200 interface

.cpu0_clk_i (or1200_clk),

.cpu0_rst_o (or1200_dbg_rst),

.cpu0_addr_o (or1200_dbg_adr_i),

.cpu0_data_o (or1200_dbg_dat_i),

.cpu0_stb_o (or1200_dbg_stb_i),

.cpu0_we_o (or1200_dbg_we_i),

.cpu0_data_i (or1200_dbg_dat_o),

.cpu0_ack_i (or1200_dbg_ack_o),

.cpu0_stall_o (or1200_dbg_stall_i),

.cpu0_bp_i (or1200_dbg_bp_o|(|or1200_dbg_wp_o)),

// TAP interface

.tck_i (xilinx_internal_jtag_clk),

.tdi_i (jtag_tap_tdo),

.tdo_o (dbg_if_tdo),

.rst_i (xilinx_internal_jtag_rst),

.shift_dr_i (jtag_tap_shift_dr),

.pause_dr_i (jtag_tap_pause_dr),

.update_dr_i (jtag_tap_update_dr),

.capture_dr_i (jtag_tap_capture_dr),//new add

.debug_select_i (dbg_if_select),

// Wishbone master

.wb_clk_i (wb_clk),

.wb_rst_i (wb_rst),

.wb_dat_i (wbm_d_dbg_dat_i),

.wb_ack_i (wbm_d_dbg_ack_i),

.wb_err_i (wbm_d_dbg_err_i),

.wb_adr_o (wbm_d_dbg_adr_o),

.wb_dat_o (wbm_d_dbg_dat_o),

.wb_cyc_o (wbm_d_dbg_cyc_o),

.wb_stb_o (wbm_d_dbg_stb_o),

.wb_sel_o (wbm_d_dbg_sel_o),

.wb_we_o (wbm_d_dbg_we_o ),

.wb_cti_o (wbm_d_dbg_cti_o),

.wb_cab_o (),

.wb_bte_o (wbm_d_dbg_bte_o)

);

/*

dbg_if dbg_if0

(

// OR1200 interface

.cpu0_clk_i (or1200_clk),

.cpu0_rst_o (or1200_dbg_rst),

.cpu0_addr_o (or1200_dbg_adr_i),

.cpu0_data_o (or1200_dbg_dat_i),

.cpu0_stb_o (or1200_dbg_stb_i),

.cpu0_we_o (or1200_dbg_we_i),

.cpu0_data_i (or1200_dbg_dat_o),

.cpu0_ack_i (or1200_dbg_ack_o),

.cpu0_stall_o (or1200_dbg_stall_i),

.cpu0_bp_i (or1200_dbg_bp_o),

// TAP interface

.tck_i (dbg_tck),

.tdi_i (jtag_tap_tdo),

.tdo_o (dbg_if_tdo),

.rst_i (wb_rst),

.shift_dr_i (jtag_tap_shift_dr),

.pause_dr_i (jtag_tap_pause_dr),

.update_dr_i (jtag_tap_update_dr),

.debug_select_i (dbg_if_select),

// Wishbone debug master

.wb_clk_i (wb_clk),

.wb_dat_i (wbm_d_dbg_dat_i),

.wb_ack_i (wbm_d_dbg_ack_i),

.wb_err_i (wbm_d_dbg_err_i),

.wb_adr_o (wbm_d_dbg_adr_o),

.wb_dat_o (wbm_d_dbg_dat_o),

.wb_cyc_o (wbm_d_dbg_cyc_o),

.wb_stb_o (wbm_d_dbg_stb_o),

.wb_sel_o (wbm_d_dbg_sel_o),

.wb_we_o (wbm_d_dbg_we_o ),

.wb_cti_o (wbm_d_dbg_cti_o),

.wb_cab_o (),

.wb_bte_o (wbm_d_dbg_bte_o)

);*/

////////////////////////////////////////////////////////////////////////

`else // !`ifdef JTAG_DEBUG

5> 修改ucf文件

由于我们采用的是xilinx_internal_jtag,不需要外部单独的jtag引脚,所以需要将ml501.ucf文件中jtag的4个引脚分配注释掉。

注意,最后一行不要注掉。

#NET tdo_pad_o LOC = E26; # HDR2_6 #NET tdi_pad_i LOC = E25; # HDR2_8 #NET tms_pad_i LOC = G22; # HDR2_10 #NET tck_pad_i LOC = G21; # HDR2_12 #NET tdo_pad_o TIG; NET tdo_pad_o PULLUP; NET tdo_pad_o IOSTANDARD = LVCMOS25; #NET tdi_pad_i TIG; NET tdi_pad_i PULLUP; NET tdi_pad_i IOSTANDARD = LVCMOS25; #NET tms_pad_i TIG; NET tms_pad_i PULLUP; NET tms_pad_i IOSTANDARD = LVCMOS25; #NET tck_pad_i TIG; NET tck_pad_i PULLUP; NET tck_pad_i IOSTANDARD = LVCMOS25; # Overide the following mapping error: # ERROR:Place:645 - A clock IOB clock component is not placed at an optimal clock # IOB site. NET "tck_pad_i" CLOCK_DEDICATED_ROUTE = FALSE;

6> FPGA配置文件(orpsoc_top.bit)的下载

进行以上修改之后,在windows下综合生成bit文件。

需要注意的是,我们要用JTAG下载,所以在生成bit文件时的配置(startup clk)需要选择‘JTAG CLK’。

7> 软件的下载与调试

在windows下用iMPACT将orpsoc_top.bit烧到FPGA(xc5vlx50)里面。

在jtag chaininit的时候,从打印信息中,我们可以发现,需要的4个bsd文件:xc5vlx50.bsd,xc95144xl.bsd,xccace.bsd,xcf32p.bsd。

这些文件可以在ISE的安装目录中找到。

8>ML501的调试

万事俱备,只欠东风。做完以上工作之后,我们就可以对ML501上的ORPSoC进行调试运行软件了。

首先,在vbox的分配USB设备中选中下载线对应的名称,我这里是“Xilinx”。可以通过lsusb命令来查看。

然后,将xc5vlx50.bsd,xc95144xl.bsd,xccace.bsd,xcf32p.bsd复制到linux下的某个目录(eg.~/ml501_bsd)。

然后,运行adv_jtag_bridge 检测下载器,建立RSP server(默认RSP端口号是9999)。

adv_jtag_bridge -b ~/ml501_bsd/ xpc_usb

具体使用方法,请参考adv_jtag_bridge的手册。

运行之后,如下图所示:

通过在xpc_usb之前加入‘-b’参数可进行自检:

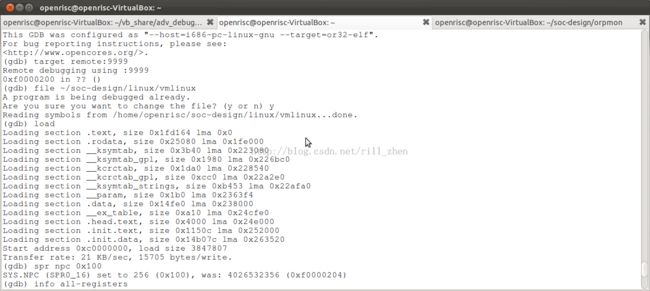

然后,运行or32-elf-gdb,建立和adv_jtag_bridge的RSP的链接。

or32-elf-gdb target remote:9999 file ~/soc-design/linux/vm;inux 或者file ~/soc-design/orpmon/orpmon.32 load

如下图所示:

load linux:

load orpmon:

这里需要注意的是,orpmon在编译之前,需要修改配置文件(~/soc-design/orpmon/include/board.h),使之针对ML501板子:

此外还要修改时钟,使之和板子的时钟一致:板子的时钟在~/soc-design/orpsocv2/boards/xilinx/ml501/sw/board/include/board.h中有定义。

修改完后,make即可生成ELF文件(orpmon.or32)和bin文件(orpmon.or32.bin)。

ELF文件用来直接load到RAM执行,bin文件用bin2sizewordbin工具生成orpmon.or32.szbin和FPGA综合之后的orpsoc_top.bit合成mcs文件,烧到FPGA板子上的SPI FLASH里面。

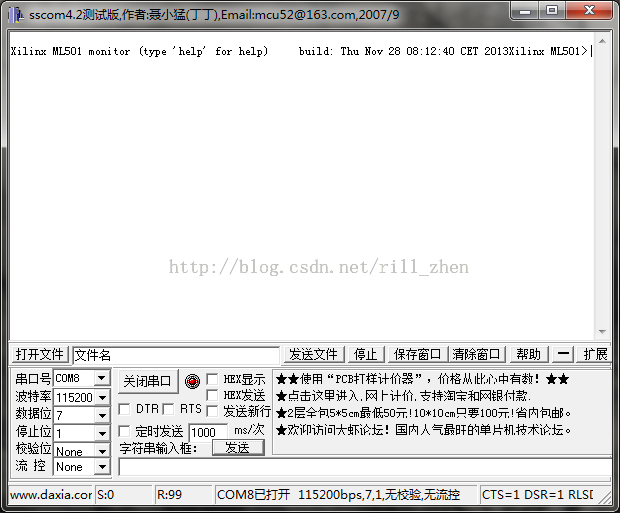

在下载程序之后,将板子的串口通过串口转USB线连接到PC机,打开串口调试工具,或者超级终端。

运行程序,即可看到输出,如下图所示:

4,工程文件

我将windows下的整个ise工程,打包上传,请参考:

http://download.csdn.net/detail/rill_zhen/6628005

5,小结

自此,我们搭建了orpsoc的仿真环境,调试环境。通过仿真环境,我们可以观察仿真波形,通过调试环境,我们可以用FPGA开发板进行实际验证。

Enjoy!