- VHDL实验四:3-8 译码器(含使能端)、四位全加器

White__Sun

fpga开发

一、实验目的1.掌握简单的VHDL程序设计。2.掌握用VHDL对组合逻辑3-8译码器电路的建模。二、实验原理1、3/8译码器的逻辑功能如下表:ABC/ENAY7Y6Y5Y4Y3Y2Y1Y0000111111110001

- 一、VHDL实现UART协议代码

cmc1028

FPGA代码fpga开发

1.uart_tx.vhd--串口发送模块编写--数据帧格式1位起始位+8位数据位+1位停止位--低位先行LSBlibraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all;useieee.std_logic_arith.all;----------------------------------------------

- 二、VHDL实现SPI协议代码

cmc1028

FPGA代码fpga开发

1、spi.vhdLIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALL;USEIEEE.STD_LOGIC_signed.ALL;----------------------------------------------------------------

- Linux下VCS与Verdi联合仿真(Verilog与VHDL混仿)

超能力MAX

fpga开发

1.介绍本篇简单介绍一下如何通过VCS与Verdi实现混合仿真,在学习过程中也遇到了很多头疼的问题,因此通过一些例子简要总结一下,当然,也希望对各位小伙伴有所帮助。很多公司ASIC设计所使用的还是更加专业的EDA软件,即Synopsys下的VCS、Verdi这种(Vivado大多针对于自家FPGA),VCS编译速度极快,仿真效率高,Verdi支持信号追溯、无缝增加信号波形等功能。2.使用环境:Li

- verilog基础知识

寒听雪落

FPGA专栏_verilogfpga开发

一,Verilog和VHDL区别全世界高层次数字系统设计领域中,应用Verilog和VHDL的比率是80%和20%;这两种语言都是用于数字电路系统设计的硬件描述语言,而且都已经是IEEE的标准。VHDL是美国军方组织开发的,VHDL1987年成为标准;Verilog是由一个公司的私有财产转化而来,Verilog是1995年成为标准。Verilog有更强的生命力,后来Verilog成为IEEE标准这

- FPGA设计怎么学?薪资前景好吗?

博览鸿蒙

FPGAfpga开发

FPGA前端设计和各岗位之间有着很多联系,是一个薪资待遇高,前景发展好的岗位。但这个岗位的门槛也比较高,很多人不知道怎么学习,下面就和宸极教育一起来了解一下吧。数字前端设计必备技能1、熟悉数字电路设计2、熟悉Verilog或VHDL3、熟悉异步电路设计4、熟悉FIFO的设计5、熟悉UNIX系统及其工具的使用6、熟悉脚本语言Perl、Shell、Tcl等7、熟悉C/C++语言、SystemVeril

- 均薪23W还缺人,FPGA工程师到底有多重要?

博览鸿蒙

FPGAfpga开发

近两年,随着FPGA行业的快速发展,FPGA工程师的需求量持续增长。FPGA技术在通信、人工智能、自动驾驶、数据中心等领域的广泛应用,使得这一岗位变得尤为重要。尤其是在高性能计算、边缘计算等场景下,FPGA凭借其高并行计算能力和灵活性,成为不可或缺的技术方案。FPGA工程师的核心职责FPGA工程师主要负责FPGA的开发、调试和优化,具体包括:逻辑设计与实现:使用Verilog/VHDL等硬件描述语

- I2C协议与FPGA开发教程_VHDL/Verilog实现

侯昂

本文还有配套的精品资源,点击获取简介:本压缩包文件包含了I2C协议的学习资料,特别是针对FPGA开发的实验教程。内容涵盖了I2C基础知识、通信模式、总线仲裁机制,以及用VHDL和Verilog语言实现I2C控制器的方法。教程还包括在FPGA平台配置I2C接口的详细步骤和实验指导,帮助读者深入理解I2C协议,并在FPGA上实现其控制。1.I2C协议基础介绍I2C(Inter-IntegratedCi

- FPGA开发中的团队协作:构建高效协同的关键路径

whik1194

fpga开发

一、团队成员角色与职责FPGA工程师核心设计:负责FPGA的逻辑设计与代码实现,依据项目需求,运用硬件描述语言(如Verilog或VHDL)完成模块功能编写。例如在设计一个高速数据采集系统时,编写数据采集、缓存及预处理的逻辑代码。功能仿真与验证:使用仿真工具对所编写的代码进行功能验证,确保逻辑设计符合预期。像在完成数字滤波器模块代码后,通过仿真测试不同输入信号下的输出,检查滤波效果。时序分析与优化

- 第11周作业---HLS编程环境入门

pss_runner

目录HLS概念HLS是什么HLS与VHDL/Verilog有什么关系?HLS技术问题HLS开发步骤环境搭建编写test.cpp文件预编译cpp文件HLS概念HLS是什么高层次综合(High-levelSynthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。所谓的高层次语言,包括C、C++、SystemC等,通常有着较高的抽象度,并且往往不具有时

- VCS简介

XtremeDV

VCS快速实战指南

1.2.1关于VCSVCS是VerilogCompiledSimulator的缩写。VCSMX®是一个编译型的代码仿真器。它使你能够分析,编译和仿真Verilog,VHDL,混合HDL,SystemVerilog,OpenVera和SystemC描述的设计。它还为您提供了一系列仿真和调试功能,以验证您的设计。这些功能提供了源码调试和仿真结果查看功能。vcs提供了一系列的feature,如下图:业界

- Xilinx Vivado的RTL分析(RTL analysis)、综合(synthesis)和实现

2401_84185145

程序员fpga开发

理论上,FPGA从编程到下载实现预期功能的过程最少仅需要上述7个步骤中的4、5、6和7,即RTL分析、综合、实现和下载。其中的RTL分析、综合、实现的具体含义和区别又是什么?2、RTL分析(RTLanalysis)一般来讲,通常的设计输入都是Verilog、VHDL或者SystemVerilog等硬件描述语言HDL编写的文件,RTL分析这一步就是将HDL语言转化成逻辑电路图的过程。比如HDL语言描

- 初识 Verilog

栀栀栀

笔记

Verilog综述:类C,并行,自顶向下,硬件描述语言,VHDL,VerilogHDL。VHDL,VerilogHDL,两种不同描述语言。Verilog语言(并行,硬件)类似C语言(串行,软件)。基础知识:1.Verilog的四值逻辑系统0低电平1高电平X不确定Z高阻态2.Verilog的数据类型寄存器数据类型表示一个抽象的数据存储单元,只能在always语句和initial语句等过程语句中被赋值

- Quartus网盘资源下载与安装 附图文安装教程

学习天使Alice

fpga开发学习

如大家所了解的,Quartus是一种FPGA设计软件(相信理工科的小伙伴,很多都接触或学习过FPGA),旨在为数字电路设计师提供一个高效、便捷的开发环境。它可以帮助用户完成数字逻辑电路的设计、仿真、综合和布局,以及与外围设备进行通信和控制。Quartus支持多种编程语言,包括VHDL、Verilog等,并具有丰富的功能和工具库,可满足不同级别、不同规模的数字电路设计需求。收藏的Quartus安装包

- xilinx FPGA 除法器IP核(divider)的使用 vivado 2019.1

小 阿 飞

fpga开发

参考:xilinxFPGA除法器ip核(divider)的使用(VHDL&Vivado)_vivado除法器_坚持每天写程序的博客-CSDN博客一、创建除法IPvivado的除法器ip核有三种类型,跟ISE相比多了一个LuMult类型,总结来说就是LuMult:使用了DSP切片、块RAM和少量的FPGA逻辑原语(寄存器和lut),所以和Radix2相比占用fpga资源更少;可以选择有符号或者无符号

- xilinx FPGA 乘法器 除法器 开方 IP核的使用(VHDL&ISE)

坚持每天写程序

xilinxfpgaip核使用例程(VHDL)FPGAVHDLISEfpga开发

目录一、乘法器ip核1.新建工程之后建一个ip核文件:2.配置ip核:3.编写顶层文件或者激励文件:第一种情况:这个是加了ce的第二种情况:这个是加了ce和sclr的第三种情况:这个是不加使能的乘法器的正确使用:第二天的新进展:最高位是1结果之所以出问题,是因为设置的时候我忘了改了,那个输入的类型默认是signed,即有符号位,大家一定要看清楚哟,按照自己需求,看是否设置最高位为有符号位二、除法器

- vivado HDL编码技术

cckkppll

fpga开发

HDL编码技术介绍硬件描述语言(HDL)编码技术使您能够:•描述数字逻辑电路中最常见的功能。•充分利用AMD设备的体系结构功能。•模板可从AMDVivado™设计套件集成设计环境中获得(侧面)。要访问模板,请在“窗口”菜单中,选择“语言模板”。本章包括编码示例。从“coding”下载编码示例文件示例。VHDL的优点•实施更严格的规则,特别是强类型、不太宽容和容易出错的规则•HDL源代码中RAM组件

- fpga 需要掌握哪些基础知识?

宸极FPGA_IC

fpga开发fpga硬件工程嵌入式硬件javastm32

个人根据自己的一些心得总结一下fpga需要掌握的基础知识,希望对你有帮助。1、数电(必须掌握的基础),然后进阶学模电,2、掌握HDL(verilog或VHDL)一般建议先学verilog,然后可以学SystemVerilog和VHDL。3、掌握FPGA设计流程/原理(推荐教材:FPGA权威指南、AlteraFPGA/CPLD设计、IP核芯志-数字逻辑设计思想、静态时序分析、嵌入式逻辑分析仪等)。4

- 1.1 Verilog 教程

二当家的素材网

Verilog教程fpga开发Verilog

VerilogHDL(简称Verilog)是一种硬件描述语言,用于数字电路的系统设计。可对算法级、门级、开关级等多种抽象设计层次进行建模。Verilog继承了C语言的多种操作符和结构,与另一种硬件描述语言VHDL相比,语法不是很严格,代码更加简洁,更容易上手。Verilog不仅定义了语法,还对语法结构都定义了清晰的仿真语义。因此,Verilog编写的数字模型就能够使用Verilog仿真器进行验证。

- 【INTEL(ALTERA)】为什么在编译 HDMI 英特尔® FPGA IP设计示例 VHDL 变体时看到错误 (13879)?

神仙约架

INTEL(ALTERA)FPGAfpga开发13879HDMI

说明由于英特尔®Quartus®PrimeProEdition软件版本23.2存在一个问题,您在编译HDMI英特尔®FPGAIP设计示例的VHDL变体时可能会看到以下错误:错误(13879):VHDL绑定指示hdmi_rx_ram_1port_intel_mce_2010_tnbtyoy.vhd(59)处出错:设计实体中的泛型“node_name”没有为关联组件中的相同泛型指定的字符串类型。解决方

- 【INTEL(ALTERA)】错误 (22595): 英特尔 Quartus不支持“BDF”类型的实体“entity_path/entity_name”

神仙约架

INTEL(ALTERA)FPGABDFQuartusfpga开发

说明从英特尔®Quartus®Prime专业版软件版本23.3开始,块设计格式(.BDF)已被弃用。任何现有的BDF设计文件都必须转换为VerilogHDL或VHDL。解决方法使用英特尔®Quartus®PrimeStandardEdition命令行和以下命令之一将您的BDF文件转换为VerilogHDL或VHDL:quartus_map--convert_bdf_to_verilog=quart

- ncverilog仿真的基础脚本

罐头说

NCSimNC-SIM为Cadence公司之VHDL与Verilog混合模拟的模拟器(simulator),可以帮助IC设计者验证及模拟其所用VHDL与Verilog混合计设的IC功能.NC-Verilog为Cadence公司之Verilog硬体描述语言模拟器(simulator),可以帮助IC设计者验证及模拟所设计IC的功能.使用NC-Verilog软体,使用者必须使用Verilog硬体描述语言

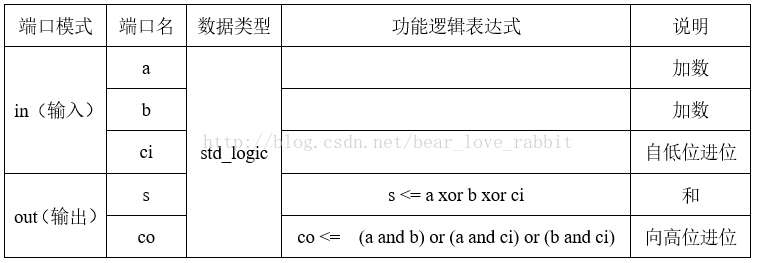

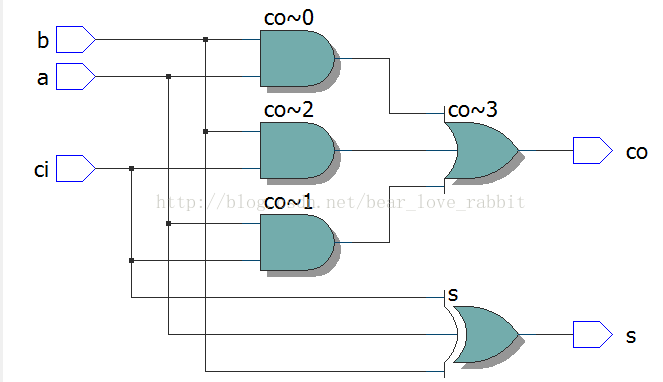

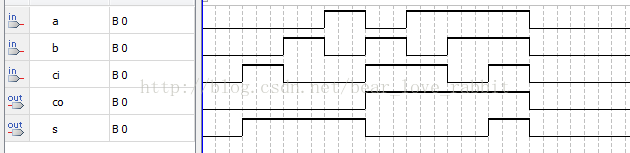

- 1位全加器设计—— 原理图与VHDL设计初步

贪睡的小孩

文章目录一、实验背景二、实验过程总结一、实验背景通过1位全加器的详细设计,掌握原理图输入以及Verilog的两种设计方法二、实验过程实验软件:quartusII13.0modelslimse10.2实验硬件:FPGA开发板IntelDE2-115实验步骤:1.打开quartusll13.0的软件,新建一个工程2.选择合适的开发板类型3.新建原理图文件:打开QuartusII,选菜单“File”一“

- 【xilinx primitives 】02 OBUFDS and OBUFTDS

hcoolabc

FPGA硬件工程

参考源:OBUFDS该设计元件是单输出缓冲器,支持低电压、差分信号。OBUFDS隔离内部电路,并为离开芯片的信号提供驱动电流。它的输出表示为两个不同的端口(O和OB),一个认为是“主端口”,另一个是“从端口”。主端口和从端口是同一逻辑信号(例如,MYNET和MYNETB)的相反相位。真值表例化VHDLLibraryUNISIM;useUNISIM.vcomponents.all;--OBUFDS:

- FPGA解码MIPI视频:Xilinx Artix7-35T低端FPGA,基于MIPI CSI-2 RX Subsystem架构实现,提供工程源码和技术支持

9527华安

FPGA解码MIPI视频专题菜鸟FPGA图像处理专题fpga开发音视频MIPI图像处理CSI

目录1、前言免责声明2、相关方案推荐我这里已有的MIPI编解码方案本方案在XilinxArtix7-100T上解码MIPI视频的应用本方案在XilinxKintex7上解码MIPI视频的应用本方案在XilinxZynq7000上解码MIPI视频的应用本方案在XilinxZynqUltraScale上解码MIPI视频的应用纯VHDL代码解码ov5640-MIPI视频方案3、本MIPICSI2模块性能

- 可逆计数器vhdl

m0_51525427

经验分享

CLR是复位控制输入端;ENA是使能控制输入端;LOAD是预置控制输入端;D[3..0]是4位并行数据输入端;DIR是加减控制输入端,当DIR=0时,计数器作加法操作,DIR=1时,计数器作减法操作;COUT是进/借位输出端。libraryIEEE;useIEEE.STD_LOGIC_1164.ALL;useIEEE.STD_LOGIC_UNSIGNED.ALL;entityRev_Counter

- 应届生把FPGA学到什么程度可以找工作?

宸极FPGA_IC

fpga开发fpga硬件工程

在FPGA(Field-ProgrammableGateArray)领域找到工作通常需要一定的基础知识和专业技能。那应届生把FPGA学到什么程度可以找工作?以下是一些学习里程碑希望可以帮助您达到求职的门槛:一、硬件描述语言(HDL)熟练度:首先,你需要熟悉至少一种硬件描述语言,如VHDL或Verilog,这是FPGA设计的基础。你应该掌握这些语言的核心语法、编写可综合代码以及如何进行仿真测试。二、

- 基于FPGA的4路抢答器verilog,quartus

FPGA代码库

fpga开发

名称:基于FPGA的4路抢答器verilog(代码在文末付费下载)软件:Quartus语言:Verilog要求:1.主持人具有最高优先级,实现4路公平抢答判决。2.具有选手提前抢答和抢答成功指示。3.每个选手的分值采用1位数码管显示,主持人可以给指定1分或和减1分。4.具有限时抢答功能。代码下载:基于FPGA的4路抢答器verilog,quartus_Verilog/VHDL资源下载代码网:hdl

- xilinx FPGA 除法器ip核(divider)的使用(VHDL&Vivado)

坚持每天写程序

FPGAVHDLVIVADOfpga开发1024程序员节

一、创建除法ip核vivado的除法器ip核有三种类型,跟ISE相比多了一个LuMult类型,总结来说就是LuMult:使用了DSP切片、块RAM和少量的FPGA逻辑原语(寄存器和lut),所以和Radix2相比占用fpga资源更少;可以选择有符号或者无符号类型数据;但是位数有限,只能用于运算量小的时候,被除数位宽:2~17,除数位宽:2~11;只能选择余数模式Radix2:使用FPGA逻辑原语(

- 单板计算机(SBC)-片上系统(SOC)嵌入式C++和FPGA(VHDL)

亚图跨际

嵌入式FPGAC/C++单板计算机SBC片上系统SOCRaspberryPiESP8266MQTTC++Qt

要点:片上系统/单板计算机嵌入式C++及VHDL编程单板计算机(RaspberryPi)C++实现MQTT监控房间门锁,灯光,并使用RESTful提示状态单板计算机(ESP8266)C++无线网络MQTT土壤湿度监测仪,实现HTTP服务器,创建网页版监控界面,构建ESP8266监控固件,单板计算机集成到IP网络,添加二氧化碳检测传感器,使用GPIO和PWM控制继电器和直流压控风扇片上系统(SOC)

- 关于旗正规则引擎下载页面需要弹窗保存到本地目录的问题

何必如此

jsp超链接文件下载窗口

生成下载页面是需要选择“录入提交页面”,生成之后默认的下载页面<a>标签超链接为:<a href="<%=root_stimage%>stimage/image.jsp?filename=<%=strfile234%>&attachname=<%=java.net.URLEncoder.encode(file234filesourc

- 【Spark九十八】Standalone Cluster Mode下的资源调度源代码分析

bit1129

cluster

在分析源代码之前,首先对Standalone Cluster Mode的资源调度有一个基本的认识:

首先,运行一个Application需要Driver进程和一组Executor进程。在Standalone Cluster Mode下,Driver和Executor都是在Master的监护下给Worker发消息创建(Driver进程和Executor进程都需要分配内存和CPU,这就需要Maste

- linux上独立安装部署spark

daizj

linux安装spark1.4部署

下面讲一下linux上安装spark,以 Standalone Mode 安装

1)首先安装JDK

下载JDK:jdk-7u79-linux-x64.tar.gz ,版本是1.7以上都行,解压 tar -zxvf jdk-7u79-linux-x64.tar.gz

然后配置 ~/.bashrc&nb

- Java 字节码之解析一

周凡杨

java字节码javap

一: Java 字节代码的组织形式

类文件 {

OxCAFEBABE ,小版本号,大版本号,常量池大小,常量池数组,访问控制标记,当前类信息,父类信息,实现的接口个数,实现的接口信息数组,域个数,域信息数组,方法个数,方法信息数组,属性个数,属性信息数组

}

&nbs

- java各种小工具代码

g21121

java

1.数组转换成List

import java.util.Arrays;

Arrays.asList(Object[] obj); 2.判断一个String型是否有值

import org.springframework.util.StringUtils;

if (StringUtils.hasText(str)) 3.判断一个List是否有值

import org.spring

- 加快FineReport报表设计的几个心得体会

老A不折腾

finereport

一、从远程服务器大批量取数进行表样设计时,最好按“列顺序”取一个“空的SQL语句”,这样可提高设计速度。否则每次设计时模板均要从远程读取数据,速度相当慢!!

二、找一个富文本编辑软件(如NOTEPAD+)编辑SQL语句,这样会很好地检查语法。有时候带参数较多检查语法复杂时,结合FineReport中生成的日志,再找一个第三方数据库访问软件(如PL/SQL)进行数据检索,可以很快定位语法错误。

- mysql linux启动与停止

墙头上一根草

如何启动/停止/重启MySQL一、启动方式1、使用 service 启动:service mysqld start2、使用 mysqld 脚本启动:/etc/inint.d/mysqld start3、使用 safe_mysqld 启动:safe_mysqld&二、停止1、使用 service 启动:service mysqld stop2、使用 mysqld 脚本启动:/etc/inin

- Spring中事务管理浅谈

aijuans

spring事务管理

Spring中事务管理浅谈

By Tony Jiang@2012-1-20 Spring中对事务的声明式管理

拿一个XML举例

[html]

view plain

copy

print

?

<?xml version="1.0" encoding="UTF-8"?>&nb

- php中隐形字符65279(utf-8的BOM头)问题

alxw4616

php中隐形字符65279(utf-8的BOM头)问题

今天遇到一个问题. php输出JSON 前端在解析时发生问题:parsererror.

调试:

1.仔细对比字符串发现字符串拼写正确.怀疑是 非打印字符的问题.

2.逐一将字符串还原为unicode编码. 发现在字符串头的位置出现了一个 65279的非打印字符.

- 调用对象是否需要传递对象(初学者一定要注意这个问题)

百合不是茶

对象的传递与调用技巧

类和对象的简单的复习,在做项目的过程中有时候不知道怎样来调用类创建的对象,简单的几个类可以看清楚,一般在项目中创建十几个类往往就不知道怎么来看

为了以后能够看清楚,现在来回顾一下类和对象的创建,对象的调用和传递(前面写过一篇)

类和对象的基础概念:

JAVA中万事万物都是类 类有字段(属性),方法,嵌套类和嵌套接

- JDK1.5 AtomicLong实例

bijian1013

javathreadjava多线程AtomicLong

JDK1.5 AtomicLong实例

类 AtomicLong

可以用原子方式更新的 long 值。有关原子变量属性的描述,请参阅 java.util.concurrent.atomic 包规范。AtomicLong 可用在应用程序中(如以原子方式增加的序列号),并且不能用于替换 Long。但是,此类确实扩展了 Number,允许那些处理基于数字类的工具和实用工具进行统一访问。

- 自定义的RPC的Java实现

bijian1013

javarpc

网上看到纯java实现的RPC,很不错。

RPC的全名Remote Process Call,即远程过程调用。使用RPC,可以像使用本地的程序一样使用远程服务器上的程序。下面是一个简单的RPC 调用实例,从中可以看到RPC如何

- 【RPC框架Hessian一】Hessian RPC Hello World

bit1129

Hello world

什么是Hessian

The Hessian binary web service protocol makes web services usable without requiring a large framework, and without learning yet another alphabet soup of protocols. Because it is a binary p

- 【Spark九十五】Spark Shell操作Spark SQL

bit1129

shell

在Spark Shell上,通过创建HiveContext可以直接进行Hive操作

1. 操作Hive中已存在的表

[hadoop@hadoop bin]$ ./spark-shell

Spark assembly has been built with Hive, including Datanucleus jars on classpath

Welcom

- F5 往header加入客户端的ip

ronin47

when HTTP_RESPONSE {if {[HTTP::is_redirect]}{ HTTP::header replace Location [string map {:port/ /} [HTTP::header value Location]]HTTP::header replace Lo

- java-61-在数组中,数字减去它右边(注意是右边)的数字得到一个数对之差. 求所有数对之差的最大值。例如在数组{2, 4, 1, 16, 7, 5,

bylijinnan

java

思路来自:

http://zhedahht.blog.163.com/blog/static/2541117420116135376632/

写了个java版的

public class GreatestLeftRightDiff {

/**

* Q61.在数组中,数字减去它右边(注意是右边)的数字得到一个数对之差。

* 求所有数对之差的最大值。例如在数组

- mongoDB 索引

开窍的石头

mongoDB索引

在这一节中我们讲讲在mongo中如何创建索引

得到当前查询的索引信息

db.user.find(_id:12).explain();

cursor: basicCoursor 指的是没有索引

&

- [硬件和系统]迎峰度夏

comsci

系统

从这几天的气温来看,今年夏天的高温天气可能会维持在一个比较长的时间内

所以,从现在开始准备渡过炎热的夏天。。。。

每间房屋要有一个落地电风扇,一个空调(空调的功率和房间的面积有密切的关系)

坐的,躺的地方要有凉垫,床上要有凉席

电脑的机箱

- 基于ThinkPHP开发的公司官网

cuiyadll

行业系统

后端基于ThinkPHP,前端基于jQuery和BootstrapCo.MZ 企业系统

轻量级企业网站管理系统

运行环境:PHP5.3+, MySQL5.0

系统预览

系统下载:http://www.tecmz.com

预览地址:http://co.tecmz.com

各种设备自适应

响应式的网站设计能够对用户产生友好度,并且对于

- Transaction and redelivery in JMS (JMS的事务和失败消息重发机制)

darrenzhu

jms事务承认MQacknowledge

JMS Message Delivery Reliability and Acknowledgement Patterns

http://wso2.com/library/articles/2013/01/jms-message-delivery-reliability-acknowledgement-patterns/

Transaction and redelivery in

- Centos添加硬盘完全教程

dcj3sjt126com

linuxcentoshardware

Linux的硬盘识别:

sda 表示第1块SCSI硬盘

hda 表示第1块IDE硬盘

scd0 表示第1个USB光驱

一般使用“fdisk -l”命

- yii2 restful web服务路由

dcj3sjt126com

PHPyii2

路由

随着资源和控制器类准备,您可以使用URL如 http://localhost/index.php?r=user/create访问资源,类似于你可以用正常的Web应用程序做法。

在实践中,你通常要用美观的URL并采取有优势的HTTP动词。 例如,请求POST /users意味着访问user/create动作。 这可以很容易地通过配置urlManager应用程序组件来完成 如下所示

- MongoDB查询(4)——游标和分页[八]

eksliang

mongodbMongoDB游标MongoDB深分页

转载请出自出处:http://eksliang.iteye.com/blog/2177567 一、游标

数据库使用游标返回find的执行结果。客户端对游标的实现通常能够对最终结果进行有效控制,从shell中定义一个游标非常简单,就是将查询结果分配给一个变量(用var声明的变量就是局部变量),便创建了一个游标,如下所示:

> var

- Activity的四种启动模式和onNewIntent()

gundumw100

android

Android中Activity启动模式详解

在Android中每个界面都是一个Activity,切换界面操作其实是多个不同Activity之间的实例化操作。在Android中Activity的启动模式决定了Activity的启动运行方式。

Android总Activity的启动模式分为四种:

Activity启动模式设置:

<acti

- 攻城狮送女友的CSS3生日蛋糕

ini

htmlWebhtml5csscss3

在线预览:http://keleyi.com/keleyi/phtml/html5/29.htm

代码如下:

<!DOCTYPE html>

<html>

<head>

<meta charset="UTF-8">

<title>攻城狮送女友的CSS3生日蛋糕-柯乐义<

- 读源码学Servlet(1)GenericServlet 源码分析

jzinfo

tomcatWebservlet网络应用网络协议

Servlet API的核心就是javax.servlet.Servlet接口,所有的Servlet 类(抽象的或者自己写的)都必须实现这个接口。在Servlet接口中定义了5个方法,其中有3个方法是由Servlet 容器在Servlet的生命周期的不同阶段来调用的特定方法。

先看javax.servlet.servlet接口源码:

package

- JAVA进阶:VO(DTO)与PO(DAO)之间的转换

snoopy7713

javaVOHibernatepo

PO即 Persistence Object VO即 Value Object

VO和PO的主要区别在于: VO是独立的Java Object。 PO是由Hibernate纳入其实体容器(Entity Map)的对象,它代表了与数据库中某条记录对应的Hibernate实体,PO的变化在事务提交时将反应到实际数据库中。

实际上,这个VO被用作Data Transfer

- mongodb group by date 聚合查询日期 统计每天数据(信息量)

qiaolevip

每天进步一点点学习永无止境mongodb纵观千象

/* 1 */

{

"_id" : ObjectId("557ac1e2153c43c320393d9d"),

"msgType" : "text",

"sendTime" : ISODate("2015-06-12T11:26:26.000Z")

- java之18天 常用的类(一)

Luob.

MathDateSystemRuntimeRundom

System类

import java.util.Properties;

/**

* System:

* out:标准输出,默认是控制台

* in:标准输入,默认是键盘

*

* 描述系统的一些信息

* 获取系统的属性信息:Properties getProperties();

*

*

*

*/

public class Sy

- maven

wuai

maven

1、安装maven:解压缩、添加M2_HOME、添加环境变量path

2、创建maven_home文件夹,创建项目mvn_ch01,在其下面建立src、pom.xml,在src下面简历main、test、main下面建立java文件夹

3、编写类,在java文件夹下面依照类的包逐层创建文件夹,将此类放入最后一级文件夹

4、进入mvn_ch01

4.1、mvn compile ,执行后会在