- FPGA 学习笔记:Vivado 2020.2 MicroBlaze MIG 测试 DDR3 篇二

zhangsz_sh

FPGA开发技术fpga开发学习

前言因为FPGADDR3测试的工程搭建步骤比较的多,所以分成几篇来写,这样利于把复杂的事情拆分,利于理解与实际的操作上一篇搭建了初步的HelloWorld工程,还没写什么代码或者改什么配置,所以FPGA开发,并不是上来就写VerilogHDL,而是要把更多的时间用在:目标是什么?DDR3测试,正常DDR3能否当RAM一样使用清楚要做什么,这里通过搭建嵌入式软核处理器的方式,快速验证实现与验证:搭建

- 基于 Verilog 的经典数字电路设计(1)加法器

新芯设计

1专栏革新中禁止订阅!!!FPGAVerilog加法器数字IC设计IC

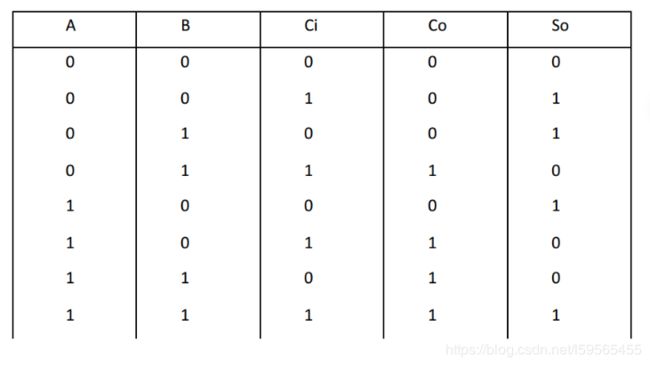

基于Verilog的经典数字电路设计(1)加法器版权所有,新芯设计,转载文章,请注来源引言一、半加器的Verilog代码实现和RTL电路实现一、全加器的Verilog代码实现和RTL电路实现引言 加法器是非常重要的,它不仅是其它复杂算术运算的基础,也是CPU中ALU的核心部件(全加器)。两个二进制数之间的算术逻辑运算例如加减乘除,在数字计算机中都是化为若干步加法操作进行的,因此,学好数字电路,从

- FPGA学习——verilog捕捉信号上升沿下降沿

or_to

FPGAfpga开发学习

在FPGA使用中,常常需要进行信号的边沿检测,如在串口通信中,需要检测接收信号的下降沿来判断串口的的起始位。常用的方法就是:设计两个一位的寄存器,用来接收被检测的信号,系统时钟来一次记一次输入信号,如果用了两个寄存器直接异或就可以了;使用高频的时钟对信号进行采样,因此要实现上升沿检测,时钟频率至少要在信号最高频率的2倍以上,否则就可能出现漏检测。代码如下:moduleedge_detect(sys

- FPGA学习篇——Verilog学习4(常见语句)

ooo-p

Verilog学习fpga开发学习

1.1结构语句结构语句主要是initial语句和always语句,initial语句它在模块中只执行一次,而always语句则不断重复执行,以下是一个比较好解释的图:(图片来源于知乎博主罗成,画的很好很直观!)1.1.1initial语句initial语句它在模块中只执行一次。它常用于测试文件的编写,用来产生仿真测试信号(激励信号),或者用于对存储器变量赋初值。语法格式:initialbegin.

- FPGA学习笔记(二)Verilog语法初步学习(语法篇1)

贾saisai

FPGA学习fpga开发学习1024程序员节

FPGA系列文章目录一、FPGA学习笔记(一)入门背景、软件及时钟约束二、FPGA学习笔记(二)Verilog语法初步学习(语法篇1)三、FPGA学习笔记(三)流水灯入门FPGA设计流程四、FPGA学习笔记(四)通过数码管学习顶层模块和例化的编写五、FPGA学习笔记(五)Testbench(测试平台)文件编写进行Modelsim仿真六、FPGA学习笔记(六)Modelsim单独仿真和Quartus

- Verilog学习方法—基础入门篇(一)

博览鸿蒙

FPGAfpga开发

前言:在FPGA开发中,VerilogHDL(硬件描述语言)是工程师必须掌握的一项基础技能。它不仅用于描述数字电路,还广泛应用于FPGA的逻辑设计与验证。对于初学者来说,掌握Verilog的核心概念和基本语法,是深入FPGA开发的第一步。本篇文章将从Verilog基础入门的角度,帮助你快速建立学习框架,逐步掌握Verilog的使用方法。1.了解Verilog的基本概念1.1什么是Verilog?V

- 使用Modelsim手动仿真

寒听雪落

FPGA专栏_verilogfpga开发

FPGA设计流程在设计输入之后,设计综合前进行RTL级仿真,称为综合前仿真,也称为前仿真或功能仿真。前仿真也就是纯粹的功能仿真,主旨在于验证电路的功能是否符合设计要求,其特点是不考虑电路门延迟与线延迟。在完成一个设计的代码编写工作之后,可以直接对代码进行仿真,检测源代码是否符合功能要求。这时,仿真的对象为HDL代码,可以比较直观的观察波形的变化,在设计的最初阶段发现问题,节省大量的精力。在布局布线

- 【从零开始学习计算机科学】数字逻辑(五) Verilog HDL语言

贫苦游商

学习fpga开发数字逻辑verilogHDL硬件开发逻辑电路

【从零开始学习计算机科学】数字逻辑(五)VerilogHDL语言VerilogHDL语言8位全加器8位计数器2位比较器三态驱动器VerilogHDL模块的结构模块声明。端口定义。信号类型。功能描述verilog描述级别verilog关键字verilog标识符编写VerilogHDL源代码的标准数据类型常量变量nets型变量register型变量reg型变量运算符及表达式算术运算符逻辑运算符位运算符

- 基于FPGA的图像中值滤波Verilog实现及MATLAB辅助验证

CodeWG

fpga开发matlab开发语言

基于FPGA的图像中值滤波Verilog实现及MATLAB辅助验证图像处理是计算机视觉和图像识别领域的重要组成部分。其中,中值滤波是一种常用的图像去噪方法,广泛应用于图像增强、边缘检测和特征提取等任务中。本文将介绍基于FPGA的图像中值滤波Verilog实现,并通过MATLAB进行辅助验证。首先,我们需要了解什么是中值滤波。中值滤波是一种非线性滤波器,它的原理是将图像中每个像素的灰度值替换为该像素

- verilog练习:HRPWM 模块设计

啄缘之间

Verilog项目练习学习资料总结fpga开发学习svuvmverilog测试用例

文章目录前言1.HRPWM代码示例:1.1关键设计说明:2.HRPWM温度补偿和动态校准2.1关键增强功能说明:2.2校准流程验证方法:2.3性能优化建议:前言需要考虑如何用SystemVerilog实现这些功能。首先,模块的输入输出端口应包括时钟、复位、占空比设置、使能信号,以及PWM输出。内部可能需要计数器、比较寄存器、MEP控制逻辑。MEP的实现可能需要一个微边沿计数器,在每个主时钟周期内生

- 用verilog实现3-8译码器和全加器

珠泪美人鱼

fpga开发

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档文章目录前言一、pandas是什么?二、使用步骤1.引入库2.读入数据总结提示:以下是本篇文章正文内容,下面案例可供参考一、用verilog实现3-8译码器首先在一个磁盘上创建一个文档。如下图:在文档中在创建两个文档来储存项目和代码。如图:之后在quartus上建好项目后,填写代码。代码如图:

- 深入解析:FIR滤波器在FPGA上的设计与实现全流程

king-agic

FPGAfpga开发经验分享

在FPGA中实现FIR(FiniteImpulseResponse)滤波器涉及多个步骤,包括滤波器设计、系数量化、硬件架构设计、HDL(HardwareDescriptionLanguage)编码、综合、布局布线以及验证。1.滤波器设计使用软件工具如MATLAB、Octave或者Python中的SciPy库来设计FIR滤波器。定义滤波器的规格,例如采样频率、截止频率、通带和阻带衰减等。生成滤波器的

- 【HDLbits--FSM状态机】

中古传奇

HDLHDL

HDLbits--FSM状态机1.6FSM介绍1.6FSM示例1单输入单输出FSM2双输入单输出FSM3真指标状态4MooreFSMdemo5时序图和状态图写状态机【博客首发于微信公众号《漫谈芯片与编程》,欢迎大家关注,多谢大家】1.6FSM介绍在Verilog中,有限状态机(FiniteStateMachine,FSM)是一种用于描述系统行为的模型,通常用于控制逻辑的设计。FSM由一组状态、状态

- 验证环境中为什么要用virtual interface

m0_71354184

systemverilog

在UVM(UniversalVerificationMethodology)中使用virtualinterface的主要目的是解决SystemVerilog接口(interface)的静态特性与UVM验证环境的动态特性之间的不匹配问题。1.解决静态与动态的绑定问题SystemVerilog接口(interface)是静态的:在编译时确定,无法直接用于动态创建的UVM对象(如driver、monit

- 6. 示例:用mailbox实现生产者-消费者模型

啄缘之间

UVM学习计划表学习verilog测试用例svuvm

文章目录前言示例一:生产者-消费者模型1示例二:生产者-消费者模型2示例三:生产者-消费者模型3示例四:生产者-消费者模型41.完整代码示例2.仿真步骤3.关键代码解析4.波形与日志分析5.常见问题与解决6.扩展练习前言以下是一个完整的SystemVerilog示例,使用mailbox实现生产者-消费者模型,包含详细注释、仿真步骤及预期结果。代码兼容主流仿真工具(如CadenceXcelium的x

- 【Verilog--Procedures】

中古传奇

HDLHDL

Verilog--Procedures1.4Procedures1.4.0CombVSClocked1.4.1always-if1.4.1.1Avoidlatches1.4.2case【博客首发于微信公众号《漫谈芯片与编程》,欢迎大家关注,多谢大家】电路模块是由通过导线连接的逻辑门组成,任何电路都可以表示为模块和赋值语句的某种组合。但有时候这不是描述电路的方便方法。过程(其中always是一个例子

- Linux下VCS与Verdi联合仿真(Verilog与VHDL混仿)

超能力MAX

fpga开发

1.介绍本篇简单介绍一下如何通过VCS与Verdi实现混合仿真,在学习过程中也遇到了很多头疼的问题,因此通过一些例子简要总结一下,当然,也希望对各位小伙伴有所帮助。很多公司ASIC设计所使用的还是更加专业的EDA软件,即Synopsys下的VCS、Verdi这种(Vivado大多针对于自家FPGA),VCS编译速度极快,仿真效率高,Verdi支持信号追溯、无缝增加信号波形等功能。2.使用环境:Li

- FPGA基础知识----第三章 第2节 综合和仿真

原来如此呀

FPGA学习之旅fpgaverilog

第2节综合和仿真2.1综合Verilog是硬件描述语言,顾名思义,就是用代码的形式描述硬件的功能,最终在硬件电路上实现该功能。在Verilog描述出硬件功能后需要使用综合器对Verilog代码进行解释并将代码转化成实际的电路来表示,最终产生实际的电路,也被称为网表。这种**将Verilog代码转成网表的工具就是综合器**。上图左上角是一段Verilog代码,该代码实现了一个加法器的功能。在经过综合

- FPGA基础知识----第二章 FPGA 开发流程

原来如此呀

FPGA学习之旅单片机嵌入式硬件

第二章FPGA开发流程FPGA的设计流程就是利用EDA开发软件和编程工具对FPGA芯片进行开发的过程。原理图和HDL(Hardwaredescriptionlanguage,硬件描述语言)是两种最常用的数字硬件电路描述方法。其中,运用HDL设计方法具有更好的移植性、通用性以及利于模块划分的特点,在工作学习中被广泛使用。典型FPGA的开发流程一般如下图所示,其包括功能定义/器件选型、设计输入、功能仿

- (14)FPGA与GPU区别

宁静致远dream

FPGA入门与提升(培训课程)fpga开发

(14)FPGA与GPU区别1文章目录1)文章目录2)FPGA入门与提升课程介绍3)FPGA简介4)FPGA与GPU区别5)技术交流6)参考资料2FPGA入门与提升课程介绍1)FPGA入门与提升文章目的是为了让想学FPGA的小伙伴快速入门以及能力提升;2)FPGA基础知识;3)VerilogHDL基本语法;4)FPGA入门实例;5)FPGA设计输入,包括代码输入、原语输入;6)FPGA设计技巧;7

- lattice hdl实现spi接口

寒听雪落

FPGA专栏_verilogfpga开发

在lattice工具链中实现SPI接口通常涉及以下步骤:定义硬件SPI接口的管脚。配置SPI时钟和模式。编写SPI主机或从机的控制逻辑。展示了如何在Lattice工具链中使用HDL语言(例如Verilog)来配置SPI接口:lattice工程顶层:spi_slave_top.v`timescale1ns/1psmodulespi_slave_top(inputwireCLK,//Systemclo

- 芯片的Date sheet中常常提到的信号(引脚)的断言(assertion)和去断言(deassertion)是什么意思?

昊虹AI笔记

芯片知识断言去断言

引脚的“断言”(assertion)和“去断言”(deassertion)通常是在硬件设计中使用的术语,尤其是在数字电路和硬件描述语言(HDL)中。它们描述的是信号电平的状态变化。分两种情况来说明这个问题:第1种情况为信号为高电平有效时;第2种情况为信号为低电平有效时。信号为高电平有效时的解释如下断言(Assert):当一个信号被“断言”时,意味着该信号变为活动状态。通常在逻辑电路中,这表示信号被

- verilog基础知识

寒听雪落

FPGA专栏_verilogfpga开发

一,Verilog和VHDL区别全世界高层次数字系统设计领域中,应用Verilog和VHDL的比率是80%和20%;这两种语言都是用于数字电路系统设计的硬件描述语言,而且都已经是IEEE的标准。VHDL是美国军方组织开发的,VHDL1987年成为标准;Verilog是由一个公司的私有财产转化而来,Verilog是1995年成为标准。Verilog有更强的生命力,后来Verilog成为IEEE标准这

- 大学实验课设无忧 ------ 基于FPGA动态数码管数字时钟

FPGA猫

大学实验课设无忧fpga开发

一、前言动态数码管显示是FPGA开发中常见的应用场景之一,尤其在数字时钟、计数器等设计中广泛应用。本文将介绍如何使用FPGA实现一个基于动态数码管的数字时钟,能够显示时、分、秒。该设计基于XilinxFPGA开发板,使用VerilogHDL编写代码,适合初学者学习和参考。二、设计思路本设计分为以下主要模块:时钟分频模块:将系统时钟分频为1Hz信号,用于计时或符合设计需求的频率。动态扫描模块:控制数

- FPGA设计怎么学?薪资前景好吗?

博览鸿蒙

FPGAfpga开发

FPGA前端设计和各岗位之间有着很多联系,是一个薪资待遇高,前景发展好的岗位。但这个岗位的门槛也比较高,很多人不知道怎么学习,下面就和宸极教育一起来了解一下吧。数字前端设计必备技能1、熟悉数字电路设计2、熟悉Verilog或VHDL3、熟悉异步电路设计4、熟悉FIFO的设计5、熟悉UNIX系统及其工具的使用6、熟悉脚本语言Perl、Shell、Tcl等7、熟悉C/C++语言、SystemVeril

- [Verilog]带使能端的级联BCD码计数器 - 以时钟计数器为例

Jason_Tye

fpga开发

问题描述//模块声明moduletop_module(inputclk,inputreset,inputena,outputpm,output[7:0]hh,output[7:0]mm,output[7:0]ss);前置知识:BCD码:将十进制数的每一位(0~9)按序,用4位2进制数表示Decimal=[3:0]Binary(78)10=(0111,1000)BCDDecimal=[3:0]\Bi

- [Verilog]模块实例化驱动的理解

Jason_Tye

fpga开发

笔者在复习刷题HDLBits时,对模块实例化时,接口的驱动有了更深理解.问题描述实现100位的带涟漪进位(ripple-carry)的全加器处理过程这是一个纯组合逻辑电路,除了可能在CombinationalBlocksalways@(*)中进行的赋值外,无需reg,所以默认的wire类型不予显式.首先实现单位全加器full_addermodulefadd(inputa;inputb;inputc

- - `always @(posedge opt_txclk)` 触发后,调用内部有 `@(posedge opt_txclk)`的task

零度随想

fpga开发

问题背景always@(posedgeopt_txclk)触发后,调用task。task内部还有@(posedgeopt_txclk),但在下一个时钟沿到来之前,always块会不会重新触发,从而导致错误。Verilog的事件调度机制always@(posedgeopt_txclk)每当opt_txclk出现上升沿时,always块会被触发,进入执行状态。任务中的@(posedgeopt_txcl

- 均薪23W还缺人,FPGA工程师到底有多重要?

博览鸿蒙

FPGAfpga开发

近两年,随着FPGA行业的快速发展,FPGA工程师的需求量持续增长。FPGA技术在通信、人工智能、自动驾驶、数据中心等领域的广泛应用,使得这一岗位变得尤为重要。尤其是在高性能计算、边缘计算等场景下,FPGA凭借其高并行计算能力和灵活性,成为不可或缺的技术方案。FPGA工程师的核心职责FPGA工程师主要负责FPGA的开发、调试和优化,具体包括:逻辑设计与实现:使用Verilog/VHDL等硬件描述语

- Verilog 实现 FPGA 复杂算法的案例

百态老人

fpga开发

在数字电路设计领域,FPGA(现场可编程门阵列)因其灵活性和高性能而备受青睐。有许多利用Verilog实现FPGA复杂算法的案例。例如,有一个项目是在FPGA中用Verilog实现开方运算。该项目充分利用Verilog的强大功能,通过深入理解FPGA的内部结构优化代码资源利用率,采用经典数学算法确保计算结果的准确性和高效性。具有高效性、可移植性和易用性等优势,适用于对实时性要求较高的应用场景,为开

- web前段跨域nginx代理配置

刘正强

nginxcmsWeb

nginx代理配置可参考server部分

server {

listen 80;

server_name localhost;

- spring学习笔记

caoyong

spring

一、概述

a>、核心技术 : IOC与AOP

b>、开发为什么需要面向接口而不是实现

接口降低一个组件与整个系统的藕合程度,当该组件不满足系统需求时,可以很容易的将该组件从系统中替换掉,而不会对整个系统产生大的影响

c>、面向接口编口编程的难点在于如何对接口进行初始化,(使用工厂设计模式)

- Eclipse打开workspace提示工作空间不可用

0624chenhong

eclipse

做项目的时候,难免会用到整个团队的代码,或者上一任同事创建的workspace,

1.电脑切换账号后,Eclipse打开时,会提示Eclipse对应的目录锁定,无法访问,根据提示,找到对应目录,G:\eclipse\configuration\org.eclipse.osgi\.manager,其中文件.fileTableLock提示被锁定。

解决办法,删掉.fileTableLock文件,重

- Javascript 面向对面写法的必要性?

一炮送你回车库

JavaScript

现在Javascript面向对象的方式来写页面很流行,什么纯javascript的mvc框架都出来了:ember

这是javascript层的mvc框架哦,不是j2ee的mvc框架

我想说的是,javascript本来就不是一门面向对象的语言,用它写出来的面向对象的程序,本身就有些别扭,很多人提到js的面向对象首先提的是:复用性。那么我请问你写的js里有多少是可以复用的,用fu

- js array对象的迭代方法

换个号韩国红果果

array

1.forEach 该方法接受一个函数作为参数, 对数组中的每个元素

使用该函数 return 语句失效

function square(num) {

print(num, num * num);

}

var nums = [1,2,3,4,5,6,7,8,9,10];

nums.forEach(square);

2.every 该方法接受一个返回值为布尔类型

- 对Hibernate缓存机制的理解

归来朝歌

session一级缓存对象持久化

在hibernate中session一级缓存机制中,有这么一种情况:

问题描述:我需要new一个对象,对它的几个字段赋值,但是有一些属性并没有进行赋值,然后调用

session.save()方法,在提交事务后,会出现这样的情况:

1:在数据库中有默认属性的字段的值为空

2:既然是持久化对象,为什么在最后对象拿不到默认属性的值?

通过调试后解决方案如下:

对于问题一,如你在数据库里设置了

- WebService调用错误合集

darkranger

webservice

Java.Lang.NoClassDefFoundError: Org/Apache/Commons/Discovery/Tools/DiscoverSingleton

调用接口出错,

一个简单的WebService

import org.apache.axis.client.Call;import org.apache.axis.client.Service;

首先必不可

- JSP和Servlet的中文乱码处理

aijuans

Java Web

JSP和Servlet的中文乱码处理

前几天学习了JSP和Servlet中有关中文乱码的一些问题,写成了博客,今天进行更新一下。应该是可以解决日常的乱码问题了。现在作以下总结希望对需要的人有所帮助。我也是刚学,所以有不足之处希望谅解。

一、表单提交时出现乱码:

在进行表单提交的时候,经常提交一些中文,自然就避免不了出现中文乱码的情况,对于表单来说有两种提交方式:get和post提交方式。所以

- 面试经典六问

atongyeye

工作面试

题记:因为我不善沟通,所以在面试中经常碰壁,看了网上太多面试宝典,基本上不太靠谱。只好自己总结,并试着根据最近工作情况完成个人答案。以备不时之需。

以下是人事了解应聘者情况的最典型的六个问题:

1 简单自我介绍

关于这个问题,主要为了弄清两件事,一是了解应聘者的背景,二是应聘者将这些背景信息组织成合适语言的能力。

我的回答:(针对技术面试回答,如果是人事面试,可以就掌

- contentResolver.query()参数详解

百合不是茶

androidquery()详解

收藏csdn的博客,介绍的比较详细,新手值得一看 1.获取联系人姓名

一个简单的例子,这个函数获取设备上所有的联系人ID和联系人NAME。

[java]

view plain

copy

public void fetchAllContacts() {

- ora-00054:resource busy and acquire with nowait specified解决方法

bijian1013

oracle数据库killnowait

当某个数据库用户在数据库中插入、更新、删除一个表的数据,或者增加一个表的主键时或者表的索引时,常常会出现ora-00054:resource busy and acquire with nowait specified这样的错误。主要是因为有事务正在执行(或者事务已经被锁),所有导致执行不成功。

1.下面的语句

- web 开发乱码

征客丶

springWeb

以下前端都是 utf-8 字符集编码

一、后台接收

1.1、 get 请求乱码

get 请求中,请求参数在请求头中;

乱码解决方法:

a、通过在web 服务器中配置编码格式:tomcat 中,在 Connector 中添加URIEncoding="UTF-8";

1.2、post 请求乱码

post 请求中,请求参数分两部份,

1.2.1、url?参数,

- 【Spark十六】: Spark SQL第二部分数据源和注册表的几种方式

bit1129

spark

Spark SQL数据源和表的Schema

case class

apply schema

parquet

json

JSON数据源 准备源数据

{"name":"Jack", "age": 12, "addr":{"city":"beijing&

- JVM学习之:调优总结 -Xms -Xmx -Xmn -Xss

BlueSkator

-Xss-Xmn-Xms-Xmx

堆大小设置JVM 中最大堆大小有三方面限制:相关操作系统的数据模型(32-bt还是64-bit)限制;系统的可用虚拟内存限制;系统的可用物理内存限制。32位系统下,一般限制在1.5G~2G;64为操作系统对内存无限制。我在Windows Server 2003 系统,3.5G物理内存,JDK5.0下测试,最大可设置为1478m。典型设置:

java -Xmx355

- jqGrid 各种参数 详解(转帖)

BreakingBad

jqGrid

jqGrid 各种参数 详解 分类:

源代码分享

个人随笔请勿参考

解决开发问题 2012-05-09 20:29 84282人阅读

评论(22)

收藏

举报

jquery

服务器

parameters

function

ajax

string

- 读《研磨设计模式》-代码笔记-代理模式-Proxy

bylijinnan

java设计模式

声明: 本文只为方便我个人查阅和理解,详细的分析以及源代码请移步 原作者的博客http://chjavach.iteye.com/

import java.lang.reflect.InvocationHandler;

import java.lang.reflect.Method;

import java.lang.reflect.Proxy;

/*

* 下面

- 应用升级iOS8中遇到的一些问题

chenhbc

ios8升级iOS8

1、很奇怪的问题,登录界面,有一个判断,如果不存在某个值,则跳转到设置界面,ios8之前的系统都可以正常跳转,iOS8中代码已经执行到下一个界面了,但界面并没有跳转过去,而且这个值如果设置过的话,也是可以正常跳转过去的,这个问题纠结了两天多,之前的判断我是在

-(void)viewWillAppear:(BOOL)animated

中写的,最终的解决办法是把判断写在

-(void

- 工作流与自组织的关系?

comsci

设计模式工作

目前的工作流系统中的节点及其相互之间的连接是事先根据管理的实际需要而绘制好的,这种固定的模式在实际的运用中会受到很多限制,特别是节点之间的依存关系是固定的,节点的处理不考虑到流程整体的运行情况,细节和整体间的关系是脱节的,那么我们提出一个新的观点,一个流程是否可以通过节点的自组织运动来自动生成呢?这种流程有什么实际意义呢?

这里有篇论文,摘要是:“针对网格中的服务

- Oracle11.2新特性之INSERT提示IGNORE_ROW_ON_DUPKEY_INDEX

daizj

oracle

insert提示IGNORE_ROW_ON_DUPKEY_INDEX

转自:http://space.itpub.net/18922393/viewspace-752123

在 insert into tablea ...select * from tableb中,如果存在唯一约束,会导致整个insert操作失败。使用IGNORE_ROW_ON_DUPKEY_INDEX提示,会忽略唯一

- 二叉树:堆

dieslrae

二叉树

这里说的堆其实是一个完全二叉树,每个节点都不小于自己的子节点,不要跟jvm的堆搞混了.由于是完全二叉树,可以用数组来构建.用数组构建树的规则很简单:

一个节点的父节点下标为: (当前下标 - 1)/2

一个节点的左节点下标为: 当前下标 * 2 + 1

&

- C语言学习八结构体

dcj3sjt126com

c

为什么需要结构体,看代码

# include <stdio.h>

struct Student //定义一个学生类型,里面有age, score, sex, 然后可以定义这个类型的变量

{

int age;

float score;

char sex;

}

int main(void)

{

struct Student st = {80, 66.6,

- centos安装golang

dcj3sjt126com

centos

#在国内镜像下载二进制包

wget -c http://www.golangtc.com/static/go/go1.4.1.linux-amd64.tar.gz

tar -C /usr/local -xzf go1.4.1.linux-amd64.tar.gz

#把golang的bin目录加入全局环境变量

cat >>/etc/profile<

- 10.性能优化-监控-MySQL慢查询

frank1234

性能优化MySQL慢查询

1.记录慢查询配置

show variables where variable_name like 'slow%' ; --查看默认日志路径

查询结果:--不用的机器可能不同

slow_query_log_file=/var/lib/mysql/centos-slow.log

修改mysqld配置文件:/usr /my.cnf[一般在/etc/my.cnf,本机在/user/my.cn

- Java父类取得子类类名

happyqing

javathis父类子类类名

在继承关系中,不管父类还是子类,这些类里面的this都代表了最终new出来的那个类的实例对象,所以在父类中你可以用this获取到子类的信息!

package com.urthinker.module.test;

import org.junit.Test;

abstract class BaseDao<T> {

public void

- Spring3.2新注解@ControllerAdvice

jinnianshilongnian

@Controller

@ControllerAdvice,是spring3.2提供的新注解,从名字上可以看出大体意思是控制器增强。让我们先看看@ControllerAdvice的实现:

@Target(ElementType.TYPE)

@Retention(RetentionPolicy.RUNTIME)

@Documented

@Component

public @interface Co

- Java spring mvc多数据源配置

liuxihope

spring

转自:http://www.itpub.net/thread-1906608-1-1.html

1、首先配置两个数据库

<bean id="dataSourceA" class="org.apache.commons.dbcp.BasicDataSource" destroy-method="close&quo

- 第12章 Ajax(下)

onestopweb

Ajax

index.html

<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3.org/TR/xhtml1/DTD/xhtml1-transitional.dtd">

<html xmlns="http://www.w3.org/

- BW / Universe Mappings

blueoxygen

BO

BW Element

OLAP Universe Element

Cube Dimension

Class

Charateristic

A class with dimension and detail objects (Detail objects for key and desription)

Hi

- Java开发熟手该当心的11个错误

tomcat_oracle

java多线程工作单元测试

#1、不在属性文件或XML文件中外化配置属性。比如,没有把批处理使用的线程数设置成可在属性文件中配置。你的批处理程序无论在DEV环境中,还是UAT(用户验收

测试)环境中,都可以顺畅无阻地运行,但是一旦部署在PROD 上,把它作为多线程程序处理更大的数据集时,就会抛出IOException,原因可能是JDBC驱动版本不同,也可能是#2中讨论的问题。如果线程数目 可以在属性文件中配置,那么使它成为

- 推行国产操作系统的优劣

yananay

windowslinux国产操作系统

最近刮起了一股风,就是去“国外货”。从应用程序开始,到基础的系统,数据库,现在已经刮到操作系统了。原因就是“棱镜计划”,使我们终于认识到了国外货的危害,开始重视起了信息安全。操作系统是计算机的灵魂。既然是灵魂,为了信息安全,那我们就自然要使用和推行国货。可是,一味地推行,是否就一定正确呢?

先说说信息安全。其实从很早以来大家就在讨论信息安全。很多年以前,就据传某世界级的网络设备制造商生产的交