- xilinx vivado srio license

QQ_1500930061

学习交流xilinxvivadosriolicense无IP捆绑

xilinxvivadosriolicense如上图所示打开xilinxvivadosriocore时显示BoughtIPlicenseavailable则表示当前使用的license是购买的license,与官网申请的评估license最大的区别是单次上电工作没有时间限制,如果仅用于学习目的,申请使用官网的license即可,当然评估的license限制还是挺多的,不仅有时间限制,而且还要捆绑以

- HI3559AV100和FPGA 7K690T的PCIE接口调试记录

雨之小

pciePCIE3559

1、基本情况HI3559AV100和690t之间使用pcie2.0x2接口连接,3559作为RC端,690T作为EP端,驱动使用XDMA。系统主要功能是FPGA采集srio接口过来的图像数据,再通过pcie把数据传递给3559,3559再实现图像数据的存储、AI处理、编码输出等。2、问题及过程2.1、内核配置RC功能参考海思手册即可,主要是在kernel的menuconfig中打开相应的功能即可。

- 超宽带信号高速采集记录回放系统在现实生活中的应用

qq_38506235

超宽带信号高速采集记录回放系统

超宽带高速记录回放系统超宽带信号高速采集记录存储回放系统主要用于对超宽带信号进行长时间高速连续实时采集记录和回放产生,适用于雷达、无线通信、软件无线电、电子对抗、电子侦察、卫星导航、复杂电磁环境模拟信号的高速采集、分析、记录、存储和回放产生。超宽带信号高速采集记录存储回放系统基于高性能PCIEXPRESS及SRIO协议,实现标准化、模块化、可扩展、可重构的超宽带信号高速连续采集记录回放产生平台。采

- PowerPC T2080部分板卡产品介绍

测试专家

其他网络fpga开发

T2080是NXP公司PowerPCT系列的中高端芯片,它具备4核8线程的E6500高性能CPU核,同时具备8组10Gb和8组8GbSerdesLanes,Serdes可复用成SRIO、PCIE、XFI、SGMII接口,因此T2080具有很强的数据处理能力和广泛的总线互联能力。科技的飞速发展使得国防、军工等领域的数据量呈爆炸式增长,海量的数据流对信息处理系统的运算处理速度、数据带宽、传输速率和通道

- TMS320C6678开发环境搭建4:BIOS-MCSDK软件包安装

Tronlong创龙

TMS320C6678TMS320C6678开发环境搭建BIOS-MCSDK软件包安装创龙

BIOS-MCSDK软件包安装TL6678-EasyEVM是一款基于TIKeyStone架构C6000系列TMS320C6678八核C66x定点/浮点高性能处理器设计的高端多核DSP评估板,由核心板与底板组成。核心板经过专业的PCBLayout和高低温测试验证,稳定可靠,可满足各种工业应用环境。评估板接口资源丰富,引出双路千兆网口、SRIO、PCIe等高速通信接口,方便用户快速进行产品方案评估与技

- FPGA图像处理项目(一)--FIFO与FFT

兔美酱xz

FPGA项目FIFOFFT

最近这个项目是要通过SRIO将图像解析数据送到XILINXFPGA通过FFT处理再用SRIO传回主控,我准备用FIFO来做一个数据的缓冲池,然后按行做FFT运算,中间结果按行存入RAM中,之后按列进行FFT运算,再存入RAM,最后传入FIFO,经过SRIO传回主控。昨天算是对FIFO有了一定了解(因为光一个fifo文档就300多页,我想一个看似简单的IP核其实想用好还真的不容易),对于本项目也够用

- FMC(HPC)接口高性能实时信号处理板(通用信号处理板 Virtex-7 FPGA(XC7VX690T)+ DSP TMS320C6678)

F_white

软件无线电验证平台视频与图像采集处理数据中心

TES605是一款基于Virtex-7的高性能实时信号处理平台,该平台采用1片TI的KeyStone系列多核浮点/定点运算DSPTMS320C6678作为主处理单元,采用1片Xilinx的Virtex-7系列FPGAXC7V690T作为协处理单元,可支持两个标准HPC接口FMC子卡,FPGA与DSP之间通过高速串行SRIO互联,这个板卡主要用在软件无线电、雷达或基带信号处理、智能信号分析、高速图形

- 高速数据采集卡合并超宽带高速记录回放系统

qq_38506120

高速数据采集卡超宽带高速记录回放系统超宽带信号高速采集记录存储回放系统主要用于对超宽带信号进行长时间高速连续实时采集记录和回放产生,适用于雷达、无线通信、软件无线电、电子对抗、电子侦察、卫星导航、复杂电磁环境模拟信号的高速采集、分析、记录、存储和回放产生。超宽带信号高速采集记录存储回放系统基于高性能PCIEXPRESS及SRIO协议,实现标准化、模块化、可扩展、可重构的超宽带信号高速连续采集记录回

- 创龙TL6678F开发板: 实现FPGA与DSP之间 SRIO(3.125Gbps, 4x)通信

falwat

FPGADSPFPGADSPSRIO

创龙TL6678F开发板官方Demo:SRIO_AD9613实现了FPGA和DSP之间的SRIO通信,SRIO的速率为5Gbps.在FPGA端,srio_gen_2模块的参考时钟为125MHz.而Demo:udp_10g_echo实现了10G以太网通信,ten_gig_eth_pcs_pma模块的参考时钟为156.25MHz.两者共用一个cdcm61002,且两个参考时钟不能分别设置.为了在此开发

- 博客摘录「 SRIO学习笔记之SRIO简介与Xilinx SRIO ip核例程详解」2023年9月1日

m0_61265869

笔记

gt_clk=line_rate/20;gt_pcs_clk=line_rate/40;phy_clk=(gt_clk*link_width)/4;log_clk=phy_clk;cfg_clk=phy_clk;

- Aurora 8B/10B、PCIe 2.0、SRIO 2.0三种协议比较

长弓的坚持

总线接口协议存储

在高性能雷达信号处理机研制中,高速串行总线正逐步取代并行总线。业界广泛使用的Xilinx公司Virtex-6系列FPGA支持多种高速串行通信协议,本文针对其中较为常用的Aurora8B/10B和PCIExpress2.0,SerialRapidIO2.0三种协议进行了测试及对比分析。首先搭建了基于Virtex-6FPGA的高速串行协议测试平台;然后设计并分别实现了三种协议的高速数据通信,测算了协议

- 国产化高速信号处理板VPX-6U-DSP-2FPGA

weixin_44862298

信号处理fpga开发

GCH-VPX-6U-DSP-2FPGA板卡是一款6UVPX标准信号处理板,含一片用于信号处理的国产化高端XX-X6678DSP、两片国产化V7690T系列FPGA、一片国产化SRIO交换机和一片国产化PCIE交换机,DSP最高可支持4GB的DDR3SDRAM,FPGA最高可支持4GB容量DDR3SDRAM,板间可以通过GTX、LVDSIO、PCIE和FMCHPC接口进行互联扩展。该板卡主要应用于

- 3U VPX导冷高性能SRIO/以太网数据交换板

F_white

fpga开发

VPX310是一款基于3UVPX导冷架构的高性能SRIO/以太网数据交换板,该板卡符合VITA46规范,用于VPX系统内部高速数据互联和路由,板卡具有1片32端口SRIOSwitch,1片16端口GbESwitch,1片高性能Kintex-7FPGA处理器。该板卡采用标准VPX欧式板卡设计,具有优良的抗振动设计、优良的散热性能和独特的环境防护设计。实物图功能框图功能参数3UVPX规格,符合VITA

- 3U VPX 总线架构+ 2片国防科大银河飞腾 FT-M6678 多核浮点运算 DSP 设计资料--VPX303

北京青翼科技

图像处理产品国产化雷达电抗产品3UVPX架构银河飞腾FT-M6678多核浮点运算DSP雷达与中频信号采集

板卡概述VPX303是一款基于3UVPX总线架构的高性能信号处理板,板载2片国防科大银河飞腾FT-M6678多核浮点运算DSP,可以实现各种实时性要求较高的信号处理算法。板卡每个DSP均支持5片DDR3SDRAM实现数据缓存,两片DSP之间通过X4SRIO进行互联。每个DSP均引出1路X4SRIO到VPX背板,板载一片CPLD进行电源和时钟复位管理。板载一片STM32单片机进行总线监控,健康管理。

- FPGA优质开源模块 - SRIO

cjx_csdn

fpga开发开源SRIO

本文介绍一个FPGA常用模块:SRIO(SerialRapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单介绍一下SRIOIP核的使用和本工程的源代码结构。由于Vivado中RapidIOIP核需要付费才能使用,因此本文提供完整工程源码。文章末尾有该工程源码获取方式,有需要的小伙伴可以收藏、

- Linux内核srio驱动,【Linux典藏大系】Linux驱动开发入门与实战

欧皇·诸葛莺

Linux内核srio驱动

标签:linuxLinux是一套免费使用和自由传播的类Unix操作系统,是一个基于POSIX和UNIX的多用户、多任务、支持多线程和多CPU的操作系统。它能运行主要的UNIX工具软件、应用程序和网络协议。它支持32位和64位硬件。Linux继承了Unix以网络为核心的设计思想,是一个性能稳定的多用户网络操作系统。内容推荐本书由浅入深,全面、系统地介绍了Linux驱动开发技术,提供了大量实例供读者实

- 基于国产器件的KCF跟踪算法实现与验证

小裘HUST

fpga开发

在国产的FT-M6678DSP上实现KCF算法是我研究生期间的主要工作,KCF算法的原理与实现已经在之前的文章以及我的Gitee仓库中有部分介绍。这里主要介绍DSP与上位机通信的方式,以及XDMALinux驱动的使用。具体的设计细节可以看我的毕业设计补充材料。SRIO与PCIe桥接器 如果只考虑实现DSP与上位机通信,设计硬件的时候就完全可以将DSP的PCIe接口与上位机连接。但我所用的硬件

- 串行RapidIO(Serial RapidIO,SRIO):协议介绍

Starry丶

标准总线接口协议fpga开发数字IC

目录一、RapidIO背景介绍二、RapidIO协议概述2.1操作与控制符号2.2包格式三、I/O逻辑操作与包格式3.1引言3.2常用的I/O逻辑操作读操作(NREAD,RESPONSEwithdata)写操作(NWRITE)和流写操作(SWRITE)带响应的写操作(NWRITE_R,RESPONSEwithnodata)原子操作(AtomicOperations,RESPONSEwithdata

- Tsi721芯片驱动代码使用说明

缥缈孤鸿_jason

SRIO嵌入式linux

驱动程序下载路径:https://download.csdn.net/download/luky_zhou123/20087673欢迎共同探讨SRIO相关问题文件说明:rio.c、rio-driver.c、rio-access.c、rio-sysfs.c:srio总线驱动代码文件/devices/tsi721.c、/devices/tsi721_dma.c:PCIE转RAPIDIO控制器驱动代码文

- vivado SRIO 学习

Lzy金壳bing

FPGA学习fpga开发

一、SRIO例化IP模块接口用于后面讲解的参考:srio_gen2_0your_instance_name(.log_clk_in(log_clk_in),//inputwire.buf_rst_in(buf_rst_in),//inputwire.log_rst_in(log_rst_in),//inputwire.gt_pcs_rst_in(gt_pcs_rst_in),//inputwire

- RapidIO 逻辑层IO操作与Message操作的原理和区别

Hello-FPGA

接上一篇SRIORapidIO(SRIO)协议介绍(一)1说明查看协议手册时会发现,逻辑层的操作分成了IO和Message2类动作,那么为什么要分成2类操作?从原理和应用角度来看IO和message的区别是什么呢?1、分成2类是为了应对不同的互联类型,IO操作主要为了应对远端的内存

- SRIO RapidIO (SRIO)协议介绍(-)

Hello-FPGA

1导读1.1与PCIe的差异典型的PCIe结构定义了一个以单个中央处理器为核心的计算机系统,比如我们常见的工控机、PXIe机箱控制器、服务器内的IO设备。从系统架构来看,这个结构的优势在于可有统一的软件驱动,软件模型,设备间具备优异的兼容性。兼容性才是王道,厂商就可以用一个标准包打天下。图

- vivado中SRIO IP核的使用

孙健强

vivado中SRIOIP核的使用姓名:孙健强学号:19021210841本文转载于:https://blog.csdn.net/weixin_44712637/article/details/89735793【嵌牛导读】通常在信号处理板卡上,会用到FPGA和DSP的组合,这就涉及到了FPGA和DSP之间的通信问题。它们之间的通信协议是RapidIO协议,而在FPGA中则需要添加SRIO的IP核来

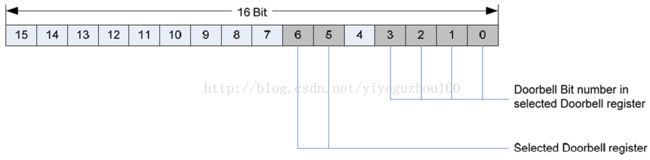

- Xilinx平台SRIO介绍(二)SRIO IP核基础知识

FPGA大叔

FPGA接口篇fpga嵌入式硬件sriorapidio

使用SRIOIP核必须掌握的基础知识!理解了这篇,剩下的只是代码罢了。汇总篇:Xilinx平台SRIO介绍(汇总篇)目录前言:SRIO、RapidIO、GT有什么关系?一、SRIOIP核概述1.1概述1.2SRIO核架构二、接口介绍2.1逻辑层接口(重点)2.1.1I/O端口2.1.2消息端口2.1.3用户自定义端口2.1.4维护端口2.1.5状态(Status)2.2Buffer接口2.3物理层

- Xilinx平台SRIO介绍(一)RapidIO协议介绍

FPGA大叔

FPGA接口篇fpga嵌入式硬件rapidiosrio

菜鸟到老鸟:会用工具;老鸟到大佬:深入理解原理。——FPGA大叔·沃自己硕得目录一、RapidIO背景介绍二、RapidIO协议概述2.1包与控制符号2.2包格式2.3事务格式与类型2.4消息传递2.5全局共享存储器2.6流量控制2.7串行物理层三、I/O逻辑操作与包格式3.1引言3.2请求包格式3.3响应包格式3.4常用的I/O逻辑操作事务四、维护操作与包格式五、消息操作与包格式5.1引言5.2

- Xilinx平台SRIO介绍(汇总篇)

FPGA大叔

FPGA接口篇嵌入式硬件fpgarapidiosrio

用最简单直白的语言记录复杂的FPGA设计。——FPGA大叔·沃自己硕得目录前言一、SRIO扫盲篇——RapidIO协议简介二、Xilinx平台SRIO-IP核基础知识三、SRIO时钟篇四、SRIOIP核配置使用教程五、示例工程ExampleDesign介绍六、SRIO收发测试后记前言本文旨在用通俗易懂的语言,最简单的姿势,将SRIO用起来。为了后续文章方便使用汇总篇的链接,先把汇总篇贴出来,也给自

- 沧小海基于xilinx srio核的学习笔记之第三章 xilinx srio核介绍(一)结构介绍

沧小海的FPGA

#SRIOxilinxrapidiosriofpga

总的目录在这哦~https://blog.csdn.net/z123canghai/article/details/114648658目录3.1SRIO核概述3.2SRIO核的结构剖析3.2.1逻辑层接口(LOG)3.2.2Buffer接口(BUF)3.2.4寄存器空间3.1SRIO核概述RapidIO互连架构,与目前大多数流行的集成通信处理器、主机处理器和网络数字信号处理器兼容,是一种高性能、包

- ISE的网表查看

爷是加菲

ISE

ISE的网表查看是在像出现了这种错误:ERROR:ConstraintSystem:59-Constraint[xiltest_srio_v5_6_top.ucf(94)]:NET"core/clock2_sspcs1_d11"notfound.Pleaseverifythat:1.Thespecifieddesignelementactuallyexistsintheoriginaldesign

- vxworks pci驱动解析

qingfengtsing

PCI/PCI-E

PCI驱动分为两种类别:1.CPU通过io方式访问的PCI设备驱动2.dma方式的PCI设备驱动其实就是两种方式在io方式下访问PCI/SRIO设备通过outbound寄存器将本地存储器映射到remote端pci设备--------------------------------IOMMU过程同时一般需要将CPU物理地址转换成本地存储器地址----------------------MMU过程MM

- VxWorks srio带宽测试 rapidio带宽测试

VxWorks_developer

PPCVxWorks技术分享

硬件环境powerpc和FPGAK7通过srio直连或者过交换都行。srio带宽测试实现:首先,保证srio读写数据正常。(1)写操作流程为:p2020通过srio接口把数据以NWRITE或者SWRITE的消息类型发送到fpga;(2)读操作流程为:p2020以NREAD消息类型将fpga数据读回。计算理论带宽值:(以2.5Gbps*4为例)2.5Gbps*4=10Gbps10Gbps*0.8=8

- Spring4.1新特性——综述

jinnianshilongnian

spring 4.1

目录

Spring4.1新特性——综述

Spring4.1新特性——Spring核心部分及其他

Spring4.1新特性——Spring缓存框架增强

Spring4.1新特性——异步调用和事件机制的异常处理

Spring4.1新特性——数据库集成测试脚本初始化

Spring4.1新特性——Spring MVC增强

Spring4.1新特性——页面自动化测试框架Spring MVC T

- Schema与数据类型优化

annan211

数据结构mysql

目前商城的数据库设计真是一塌糊涂,表堆叠让人不忍直视,无脑的架构师,说了也不听。

在数据库设计之初,就应该仔细揣摩可能会有哪些查询,有没有更复杂的查询,而不是仅仅突出

很表面的业务需求,这样做会让你的数据库性能成倍提高,当然,丑陋的架构师是不会这样去考虑问题的。

选择优化的数据类型

1 更小的通常更好

更小的数据类型通常更快,因为他们占用更少的磁盘、内存和cpu缓存,

- 第一节 HTML概要学习

chenke

htmlWebcss

第一节 HTML概要学习

1. 什么是HTML

HTML是英文Hyper Text Mark-up Language(超文本标记语言)的缩写,它规定了自己的语法规则,用来表示比“文本”更丰富的意义,比如图片,表格,链接等。浏览器(IE,FireFox等)软件知道HTML语言的语法,可以用来查看HTML文档。目前互联网上的绝大部分网页都是使用HTML编写的。

打开记事本 输入一下内

- MyEclipse里部分习惯的更改

Array_06

eclipse

继续补充中----------------------

1.更改自己合适快捷键windows-->prefences-->java-->editor-->Content Assist-->

Activation triggers for java的右侧“.”就可以改变常用的快捷键

选中 Text

- 近一个月的面试总结

cugfy

面试

本文是在学习中的总结,欢迎转载但请注明出处:http://blog.csdn.net/pistolove/article/details/46753275

前言

打算换个工作,近一个月面试了不少的公司,下面将一些面试经验和思考分享给大家。另外校招也快要开始了,为在校的学生提供一些经验供参考,希望都能找到满意的工作。

- HTML5一个小迷宫游戏

357029540

html5

通过《HTML5游戏开发》摘抄了一个小迷宫游戏,感觉还不错,可以画画,写字,把摘抄的代码放上来分享下,喜欢的同学可以拿来玩玩!

<html>

<head>

<title>创建运行迷宫</title>

<script type="text/javascript"

- 10步教你上传githib数据

张亚雄

git

官方的教学还有其他博客里教的都是给懂的人说得,对已我们这样对我大菜鸟只能这么来锻炼,下面先不玩什么深奥的,先暂时用着10步干净利索。等玩顺溜了再用其他的方法。

操作过程(查看本目录下有哪些文件NO.1)ls

(跳转到子目录NO.2)cd+空格+目录

(继续NO.3)ls

(匹配到子目录NO.4)cd+ 目录首写字母+tab键+(首写字母“直到你所用文件根就不再按TAB键了”)

(查看文件

- MongoDB常用操作命令大全

adminjun

mongodb操作命令

成功启动MongoDB后,再打开一个命令行窗口输入mongo,就可以进行数据库的一些操作。输入help可以看到基本操作命令,只是MongoDB没有创建数据库的命令,但有类似的命令 如:如果你想创建一个“myTest”的数据库,先运行use myTest命令,之后就做一些操作(如:db.createCollection('user')),这样就可以创建一个名叫“myTest”的数据库。

一

- bat调用jar包并传入多个参数

aijuans

下面的主程序是通过eclipse写的:

1.在Main函数接收bat文件传递的参数(String[] args)

如: String ip =args[0]; String user=args[1]; &nbs

- Java中对类的主动引用和被动引用

ayaoxinchao

java主动引用对类的引用被动引用类初始化

在Java代码中,有些类看上去初始化了,但其实没有。例如定义一定长度某一类型的数组,看上去数组中所有的元素已经被初始化,实际上一个都没有。对于类的初始化,虚拟机规范严格规定了只有对该类进行主动引用时,才会触发。而除此之外的所有引用方式称之为对类的被动引用,不会触发类的初始化。虚拟机规范严格地规定了有且仅有四种情况是对类的主动引用,即必须立即对类进行初始化。四种情况如下:1.遇到ne

- 导出数据库 提示 outfile disabled

BigBird2012

mysql

在windows控制台下,登陆mysql,备份数据库:

mysql>mysqldump -u root -p test test > D:\test.sql

使用命令 mysqldump 格式如下: mysqldump -u root -p *** DBNAME > E:\\test.sql。

注意:执行该命令的时候不要进入mysql的控制台再使用,这样会报

- Javascript 中的 && 和 ||

bijian1013

JavaScript&&||

准备两个对象用于下面的讨论

var alice = {

name: "alice",

toString: function () {

return this.name;

}

}

var smith = {

name: "smith",

- [Zookeeper学习笔记之四]Zookeeper Client Library会话重建

bit1129

zookeeper

为了说明问题,先来看个简单的示例代码:

package com.tom.zookeeper.book;

import com.tom.Host;

import org.apache.zookeeper.WatchedEvent;

import org.apache.zookeeper.ZooKeeper;

import org.apache.zookeeper.Wat

- 【Scala十一】Scala核心五:case模式匹配

bit1129

scala

package spark.examples.scala.grammars.caseclasses

object CaseClass_Test00 {

def simpleMatch(arg: Any) = arg match {

case v: Int => "This is an Int"

case v: (Int, String)

- 运维的一些面试题

yuxianhua

linux

1、Linux挂载Winodws共享文件夹

mount -t cifs //1.1.1.254/ok /var/tmp/share/ -o username=administrator,password=yourpass

或

mount -t cifs -o username=xxx,password=xxxx //1.1.1.1/a /win

- Java lang包-Boolean

BrokenDreams

boolean

Boolean类是Java中基本类型boolean的包装类。这个类比较简单,直接看源代码吧。

public final class Boolean implements java.io.Serializable,

- 读《研磨设计模式》-代码笔记-命令模式-Command

bylijinnan

java设计模式

声明: 本文只为方便我个人查阅和理解,详细的分析以及源代码请移步 原作者的博客http://chjavach.iteye.com/

import java.util.ArrayList;

import java.util.Collection;

import java.util.List;

/**

* GOF 在《设计模式》一书中阐述命令模式的意图:“将一个请求封装

- matlab下GPU编程笔记

cherishLC

matlab

不多说,直接上代码

gpuDevice % 查看系统中的gpu,,其中的DeviceSupported会给出matlab支持的GPU个数。

g=gpuDevice(1); %会清空 GPU 1中的所有数据,,将GPU1 设为当前GPU

reset(g) %也可以清空GPU中数据。

a=1;

a=gpuArray(a); %将a从CPU移到GPU中

onGP

- SVN安装过程

crabdave

SVN

SVN安装过程

subversion-1.6.12

./configure --prefix=/usr/local/subversion --with-apxs=/usr/local/apache2/bin/apxs --with-apr=/usr/local/apr --with-apr-util=/usr/local/apr --with-openssl=/

- sql 行列转换

daizj

sql行列转换行转列列转行

行转列的思想是通过case when 来实现

列转行的思想是通过union all 来实现

下面具体例子:

假设有张学生成绩表(tb)如下:

Name Subject Result

张三 语文 74

张三 数学 83

张三 物理 93

李四 语文 74

李四 数学 84

李四 物理 94

*/

/*

想变成

姓名 &

- MySQL--主从配置

dcj3sjt126com

mysql

linux下的mysql主从配置: 说明:由于MySQL不同版本之间的(二进制日志)binlog格式可能会不一样,因此最好的搭配组合是Master的MySQL版本和Slave的版本相同或者更低, Master的版本肯定不能高于Slave版本。(版本向下兼容)

mysql1 : 192.168.100.1 //master mysq

- 关于yii 数据库添加新字段之后model类的修改

dcj3sjt126com

Model

rules:

array('新字段','safe','on'=>'search')

1、array('新字段', 'safe')//这个如果是要用户输入的话,要加一下,

2、array('新字段', 'numerical'),//如果是数字的话

3、array('新字段', 'length', 'max'=>100),//如果是文本

1、2、3适当的最少要加一条,新字段才会被

- sublime text3 中文乱码解决

dyy_gusi

Sublime Text

sublime text3中文乱码解决

原因:缺少转换为UTF-8的插件

目的:安装ConvertToUTF8插件包

第一步:安装能自动安装插件的插件,百度“Codecs33”,然后按照步骤可以得到以下一段代码:

import urllib.request,os,hashlib; h = 'eb2297e1a458f27d836c04bb0cbaf282' + 'd0e7a30980927

- 概念了解:CGI,FastCGI,PHP-CGI与PHP-FPM

geeksun

PHP

CGI

CGI全称是“公共网关接口”(Common Gateway Interface),HTTP服务器与你的或其它机器上的程序进行“交谈”的一种工具,其程序须运行在网络服务器上。

CGI可以用任何一种语言编写,只要这种语言具有标准输入、输出和环境变量。如php,perl,tcl等。 FastCGI

FastCGI像是一个常驻(long-live)型的CGI,它可以一直执行着,只要激活后,不

- Git push 报错 "error: failed to push some refs to " 解决

hongtoushizi

git

Git push 报错 "error: failed to push some refs to " .

此问题出现的原因是:由于远程仓库中代码版本与本地不一致冲突导致的。

由于我在第一次git pull --rebase 代码后,准备push的时候,有别人往线上又提交了代码。所以出现此问题。

解决方案:

1: git pull

2:

- 第四章 Lua模块开发

jinnianshilongnian

nginxlua

在实际开发中,不可能把所有代码写到一个大而全的lua文件中,需要进行分模块开发;而且模块化是高性能Lua应用的关键。使用require第一次导入模块后,所有Nginx 进程全局共享模块的数据和代码,每个Worker进程需要时会得到此模块的一个副本(Copy-On-Write),即模块可以认为是每Worker进程共享而不是每Nginx Server共享;另外注意之前我们使用init_by_lua中初

- java.lang.reflect.Proxy

liyonghui160com

1.简介

Proxy 提供用于创建动态代理类和实例的静态方法

(1)动态代理类的属性

代理类是公共的、最终的,而不是抽象的

未指定代理类的非限定名称。但是,以字符串 "$Proxy" 开头的类名空间应该为代理类保留

代理类扩展 java.lang.reflect.Proxy

代理类会按同一顺序准确地实现其创建时指定的接口

- Java中getResourceAsStream的用法

pda158

java

1.Java中的getResourceAsStream有以下几种: 1. Class.getResourceAsStream(String path) : path 不以’/'开头时默认是从此类所在的包下取资源,以’/'开头则是从ClassPath根下获取。其只是通过path构造一个绝对路径,最终还是由ClassLoader获取资源。 2. Class.getClassLoader.get

- spring 包官方下载地址(非maven)

sinnk

spring

SPRING官方网站改版后,建议都是通过 Maven和Gradle下载,对不使用Maven和Gradle开发项目的,下载就非常麻烦,下给出Spring Framework jar官方直接下载路径:

http://repo.springsource.org/libs-release-local/org/springframework/spring/

s

- Oracle学习笔记(7) 开发PLSQL子程序和包

vipbooks

oraclesql编程

哈哈,清明节放假回去了一下,真是太好了,回家的感觉真好啊!现在又开始出差之旅了,又好久没有来了,今天继续Oracle的学习!

这是第七章的学习笔记,学习完第六章的动态SQL之后,开始要学习子程序和包的使用了……,希望大家能多给俺一些支持啊!

编程时使用的工具是PLSQL