MYIR-ZYNQ7000系列-zturn教程(14):在PL中使用ILA进行调试

开发板环境:vivado 2017.1 ,开发板型号xc7z020clg400-1,这个工程主要是用ILA观测FPGA输出管脚的波形

链接:https://pan.baidu.com/s/1sVfxSVcdcRS2wgOwJUl5yg 密码:0agy

Step1 先新建一个vivado 工程

Step2 点击这个Add Sources新建一个fpga工程

在弹出的对话框中选择第二项,然后点击Next

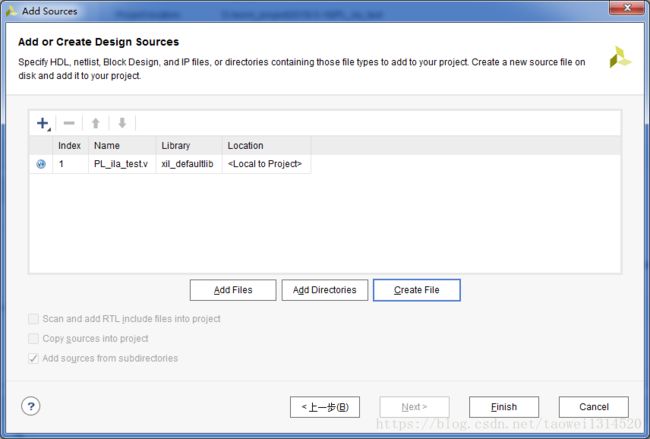

在弹出的对话框中点击Create File新建一个.v文件

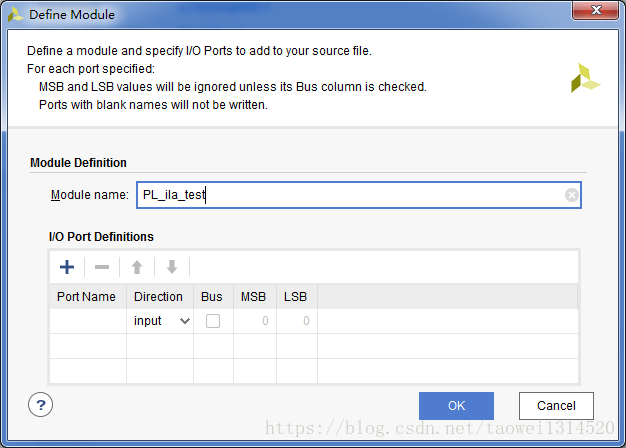

这个.v文件自己可以随便取一个名称,然后点击OK

点击Finish

再在弹出的对话框中点击OK

再在弹出的对话框中点击Yes

这样就完成了创建一个fpga工程

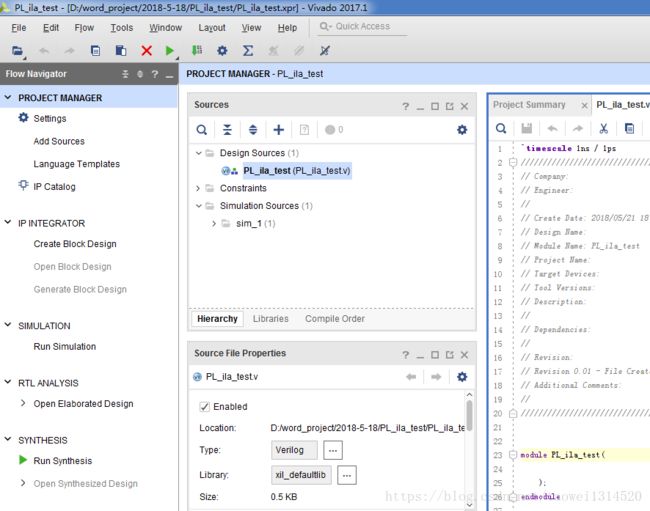

这里是写的一个简单的fpga分频的程序,因这里主要是怎么使用这个ila所以程序写得比较简单

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2018/05/21 18:59:48

// Design Name:

// Module Name: PL_ila_test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module PL_ila_test(

i_clk,

i_rst_n,

sclk_out,

count

);

input wire i_clk;

input wire i_rst_n;

output wire sclk_out;

output wire [9:0] count;

reg [9:0] count_r;

reg sclk_out_r;

always@(posedge i_clk or negedge i_rst_n)begin

if(i_rst_n == 1'b0)

count_r <= 10'd0;

else if(count_r == 10'd999)

count_r <= 10'd0;

else

count_r <= count_r + 1'b1;

end

always@(posedge i_clk or negedge i_rst_n)begin

if(i_rst_n == 1'b0)

sclk_out_r <= 1'b0;

else if(count_r == 10'd999)

sclk_out_r <= ~sclk_out_r;

else

sclk_out_r <= sclk_out_r;

end

assign sclk_out = sclk_out_r;

assign count = count_r;

endmodule已经写好的fpga程序如下图所示

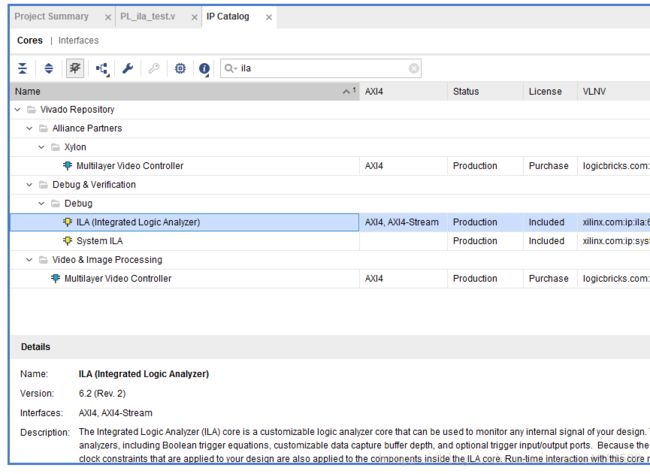

Step3 调用这个ILA核

点击这个IP Catalog

在弹出的查找栏中输入ila,然后选择ILA(Integrated Logic Analyzer)这个双击就会弹出ILA设置对话框

ILA对话框如下图所示

从这里可以看到这类型有Native和AXI这两种,Native通常是用来测量电平或一定的位宽信号,AXI就比较明显了

直接测量AXI总线的信号,我这里主要测试这个fpga程序的输出时钟和计数器输出的值所以只用这个Native。

再往下看这个Number of Probes是设置这个ILA有几个探针,因我这里只需测量这个sclk_out和count这两个信

号所以只用两个探针这里设置为2,这个Sample Data Depth相当于设置测量波形长度,这里的4096也就相当于

一共采集4096个ILA的时钟周期,因这里的测量是会占用开发板的内存如果你的程序占用内存比较大这里又设置

比较大就会出现报错,这里我设置为4096,其它的都保持默认不变。

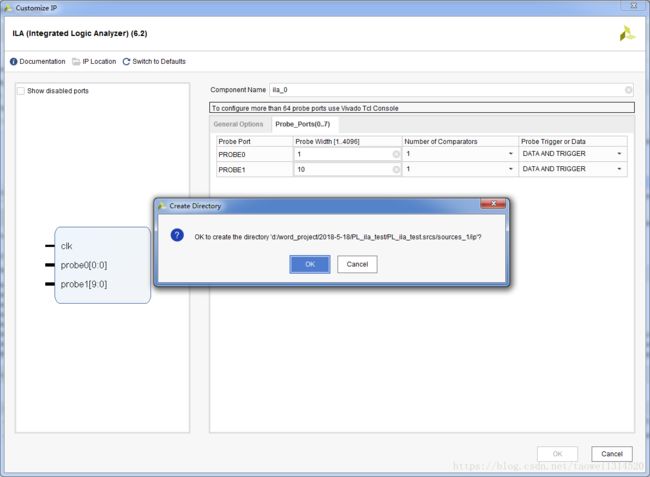

再点击这个Probe_PORTS(0..7)这个选项卡

在弹出的设置对话框中,第一个探针我们是测量这个输出时钟的sclk_out所以位宽不变为1,第二个探针我们测量的是

一个[9:0]count的计数器一共有10位所以设置位宽为10,然后点击OK

继续点击OK

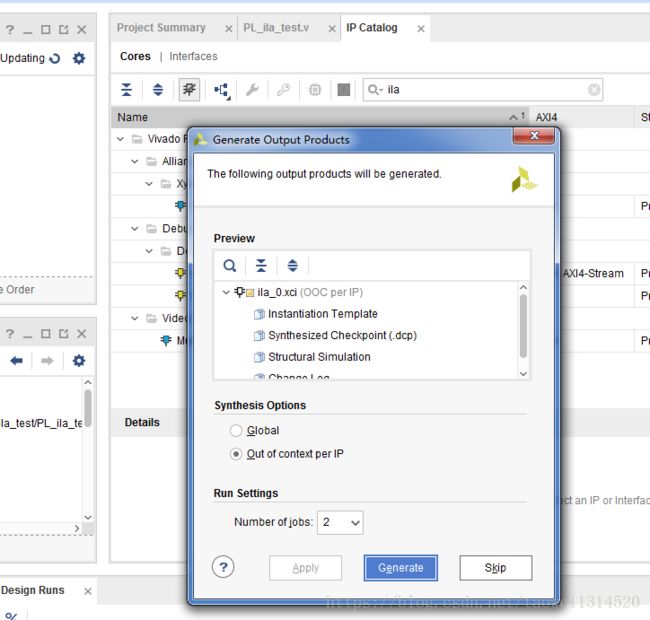

再在弹出的对话框中点击Generate

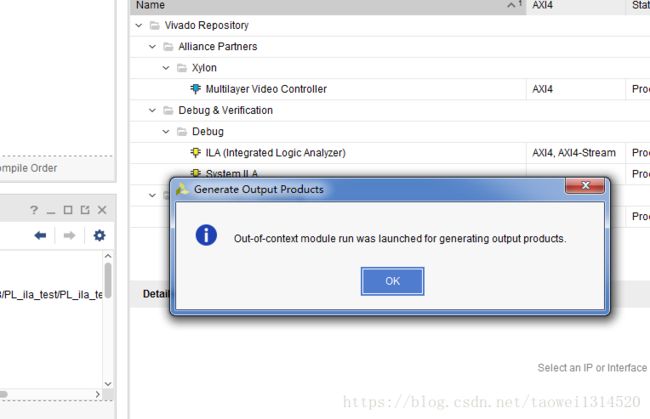

点击OK

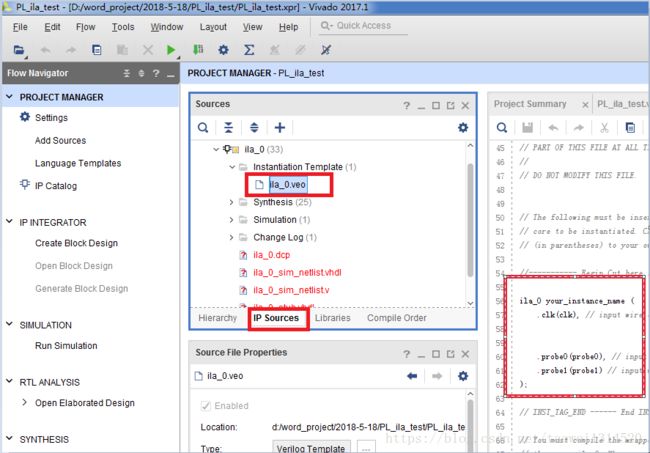

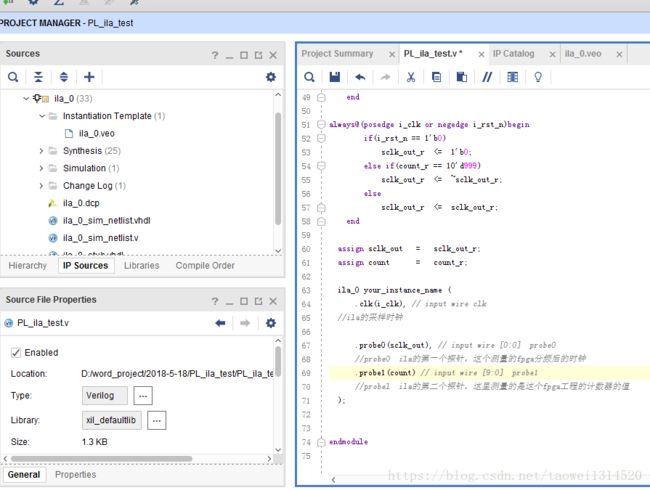

点击这个IP Sources选项卡,然后点击ila_0.veo可以看到右边有已经例化好的ILA模块

Step4 例化这个ILA核到这个fpga工程

将上图中例化的ILA模块复制到这个fpga工程的下面,如下图所示

将这个所以测量的信号连到这个ILA上如下图所示,这里需要注意的是这个ILA的采样时钟一定要大于这个被采样的

时钟的频率,比如这个ILA的采样时钟是输入的i_clk,那么这个i_clk最好是大于或者等于这个被采样时钟sclk_out

的2倍或者以上,这个是根据采样定理得出的结论这里一定要注意。

例化后的fpga程序

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2018/05/21 18:59:48

// Design Name:

// Module Name: PL_ila_test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module PL_ila_test(

i_clk,

i_rst_n,

sclk_out,

count

);

input wire i_clk;

input wire i_rst_n;

output wire sclk_out;

output wire [9:0] count;

reg [9:0] count_r;

reg sclk_out_r;

always@(posedge i_clk or negedge i_rst_n)begin

if(i_rst_n == 1'b0)

count_r <= 10'd0;

else if(count_r == 10'd999)

count_r <= 10'd0;

else

count_r <= count_r + 1'b1;

end

always@(posedge i_clk or negedge i_rst_n)begin

if(i_rst_n == 1'b0)

sclk_out_r <= 1'b0;

else if(count_r == 10'd999)

sclk_out_r <= ~sclk_out_r;

else

sclk_out_r <= sclk_out_r;

end

assign sclk_out = sclk_out_r;

assign count = count_r;

ila_0 your_instance_name (

.clk(i_clk), // input wire clk

//ila的采样时钟

.probe0(sclk_out), // input wire [0:0] probe0

//probe0 ila的第一个探针,这个测量的fpga分频后的时钟

.probe1(count) // input wire [9:0] probe1

//probel ila的第二个探针,这里测量的是这个fpga工程的计数器的值

);

endmodule

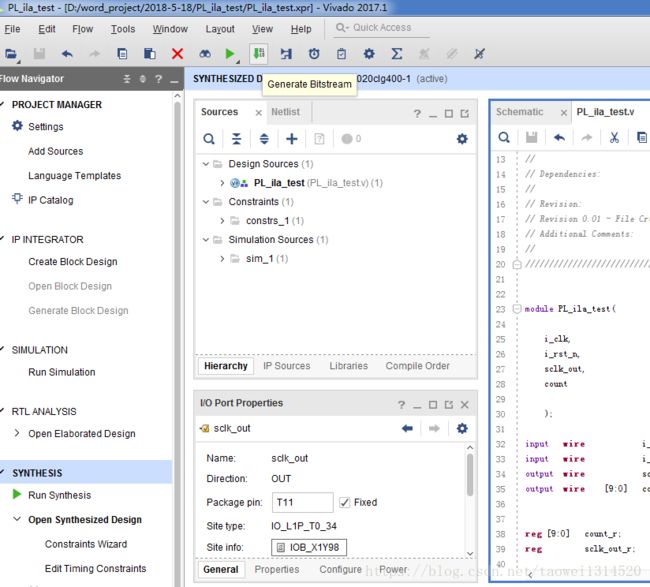

Step5 分配fpga管脚并且生成bit文件

这里设置管脚比较简单,因之前的博客有详细介绍这里不在重复

点击这个图标生成bit文件

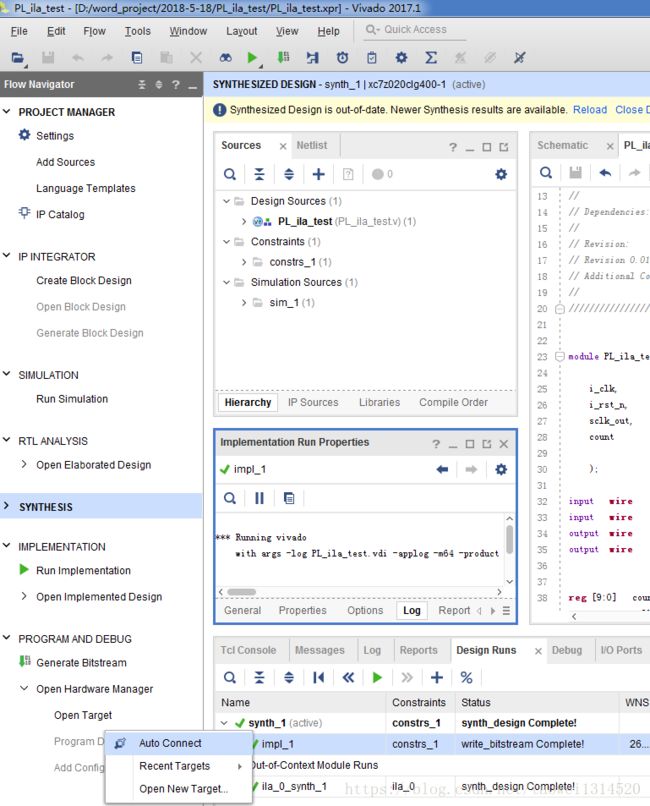

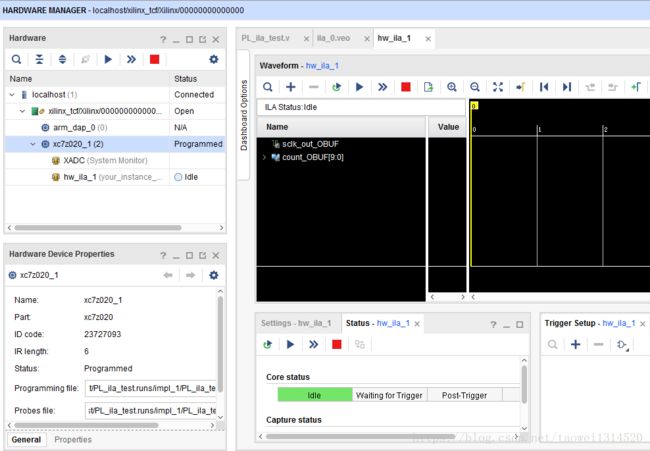

Step6 将bit文件下载到开发板进行ila调试

点击下面的Open Target-->选择Auto Connect

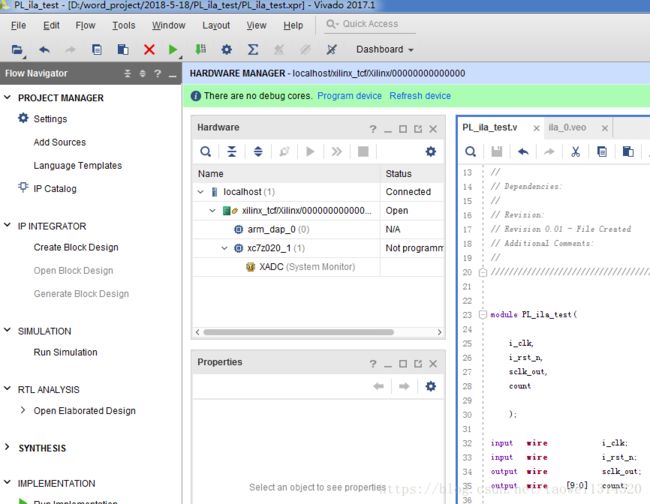

可以看到已经检测我们的开发板,说明这个jtag连接是正常的

点击这个Program device

在弹出的对话框中点击Program进行下载

下载完成后如下图所示

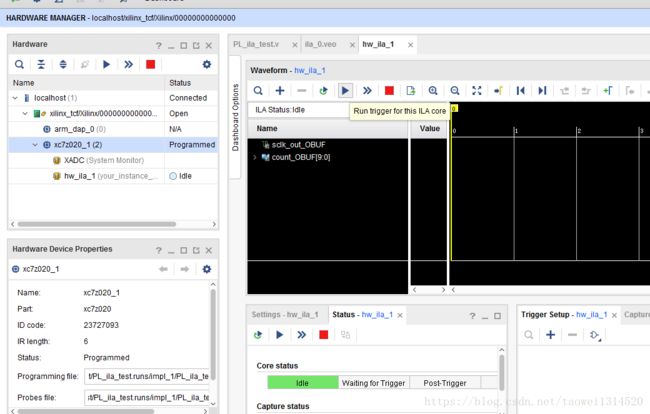

点击这个Run运行按钮

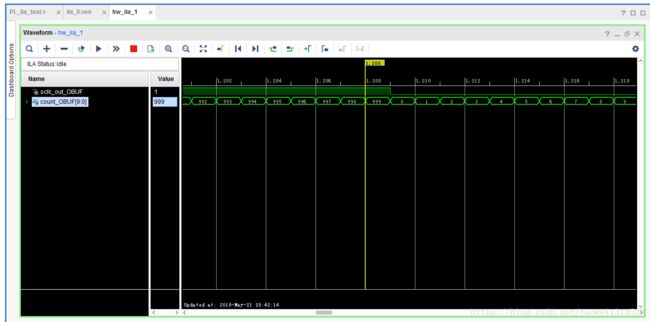

下图便是我们采集到的波形