UART(RS232) 控制器简介

Nios UART(RS232) 控制器简介

■周聪辉 原创+装载+翻译=整理

一、UART简介

UART(Universal Asynchronous Receiver/Transmitter)即通用异步收发传输器,工作于数据链路层。包含了RS-232、RS-422、RS-485串口通信和红外(IrDA) 等等。UART协议作为一种低速通信协议,广泛应用于通信领域等各种场合。UART基本可分为并口通信及串口通信两种。

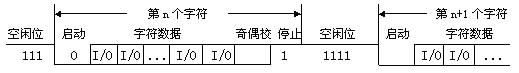

异步串口通信协议作为UART的一种,工作原理是将传输数据的每个字符一位接一位地传输。图一给出了其工作模式:

图 一

其中各位的意义如下:

起始位:先发出一个逻辑”0”的信号,表示传输字符的开始。

资料位:紧接着起始位之后。资料位的个数可以是4、5、6、7、8等,构成一个字符。通常采用ASCII码。从最低位开始传送,靠时钟定位。

奇偶校验位:资料位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验),以此来校验资料传送的正确性。

停止位:它是一个字符数据的结束标志。可以是1位、1.5位、2位的高电平。

空闲位:处于逻辑“1”状态,表示当前线路上没有资料传送。

波特率:是衡量资料传送速率的指针。表示每秒钟传送的二进制位数。例如资料传送速率为120字符/秒,而每一个字符为10位,则其传送的波特率为10×120=1200字符/秒=1200波特。

在嵌入式系统或者计算机中,并非直接对串口直接进行,而是通过SCI (串行通讯接口)模块对其进行控制。(注:“SCI”首先由Motorola微串口微控制器而得名,SCI另一种说法是“UART控制器”)常用的许多芯片中都包含了SCI ,例如ARM的S3C2410X芯片内嵌了3个串行接口控制器,而Nios等软核芯片则可以用选用UART(RS232) 的IP对UART进行控制。PC机则常用 16650 UART,16750 UART等控制串口。

二、Nios UART 控制器简介

当我们用软核做嵌入式系统开发时,我们就可以用内嵌的Nios UART 来控制串口。

在用SOPC Builder创建时,选用了UART(RS232)的IP逻辑,那么就可以使用嵌入Altera器件的Nios UART逻辑来对串口进行控制。

UART寄存器如下图所示:

Notes to Table 6–4:

(1)These bits are reserved. Reading returns an undefined value. Write zero.

(2)These bits may or may not exist, depending on the Data Width hardware option. If they do not exist, they read zero, and writing has no effect.

(3)Writing zero to the status register clears the dcts, e, toe, roe, brk, fe, and pe bits.

(4)This register may or may not exist, depending on hardware configuration options. If it does not exist, reading returns an undefined value and writing has no effect.

(1)接收数据寄存器(rxdata)

The rxdata register holds data received via the RXD input. When a new character is fully received via the RXD input, it is transferred into the rxdata register, and the status register’s rrdy bit is set to 1. The status register’s rrdy bit is set to 0 when the rxdata register is read. If a character is transferred into the rxdata register while the rrdy bit is already set (i.e., the previous character was not retrieved), a receiver-overrun error occurs and the status register’s roe bit is set to 1. New characters are always transferred into the rxdata register, regardless of whether the previous character was read. Writing data to the rxdata register has no effect.

(2)发送数据寄存器(txdata)

Avalon master peripherals write characters to be transmitted into the txdata register. Characters should not be written to txdata until the transmitter is ready for a new character, as indicated by the TRDY bit in the status register. The TRDY bit is set to 0 when a character is written into the txdata register. The TRDY bit is set to 1 when the character is transferred from the txdata register into the transmitter shift register. If a character is written to the txdata register when TRDY is 0, the result is undefined. Reading the txdata register returns an undefined value.

For example, assume the transmitter logic is idle and an Avalon master peripheral writes a first character into the txdata register. The TRDY bit is set to 0, then set to 1 when the character is transferred into the transmitter shift register. The master can then write a second character into the txdata register, and the TRDY bit is set to 0 again. However, this time the shift register is still busy shifting out the first character to the TXD output. The TRDY bit is not set to 1 until the first character is fully shifted out and the second character is automatically transferred into the transmitter shift register.

(3)状态寄存器(status)

状态寄存器由分别指示UART核内的特殊状态的一组独立的位组成。每个状态位都与控制寄存器中的中断允许位相对应。任何时候都可以读取状态寄存器而且不会改变任何值。将0 写进状态寄存器将清除DCTS,E,TOE,ROE,BREK,FE,PE位。

The status register consists of individual bits that indicate particular conditions inside the UART core. Each status bit is associated with a corresponding interrupt-enable bit in the control register. The status register can be read at any time. Reading does not change the value of any of the bits. Writing zero to the status register clears the DCTS, E, TOE, ROE, BRK, FE, and PE bits.

状态寄存器描述如下:

| 位 号 |

位 名 |

说 明 |

位 号 |

位 名 |

说 明 |

| 0 |

PE |

Parity error |

6 |

TRDY |

Transmit ready |

| 1 |

FE |

Framing error |

7 |

RRDY |

Receive character ready |

| 2 |

BRK |

Break detect |

8 |

E |

Exception |

| 3 |

ROE |

Receive overrun error |

10* |

DCTS |

Change in clear to send signal |

| 4 |

TOE |

Transmit overrun error |

11* |

CTS |

Clear-to-send signal |

| 5 |

TMT |

Transmit empty |

12* |

EOP |

End of packet encountered |

注:带星号为可选项,在硬件中不一定存在

| 位 |

位名 |

说 明 |

位 |

位名 |

说 明 |

| 0 |

IPE |

Interrupt for Parity error |

6 |

ITRDY |

Interrupt for a Transmit ready |

| 1 |

IFE |

Interrupt for Framing error |

7 |

IRRDY |

Interrupt for a read ready |

| 2 |

IBRK |

Interrupt for Break detect |

8 |

IE |

Interrupt for an Exception |

| 3 |

IROE |

Interrupt for Receive overrun error |

9 |

TRBK |

Transimit break |

| 4 |

ITOE |

Interrupt for Transmit overrun error |

10 |

IDCTS |

Interrupt for Change in clear to send signal |

| 5 |

ITMT |

Interrupt for Transmit empty |

11* |

RTS |

Interrupt for Clear-to-send signal |

|

|

|

|

12 |

IEOP |

Interrupt for End of packet encountered |

注:带星号为可选项,在硬件中不一定存在

详细的解释请参见《Quartus II Version 6.0 Handbook,Volume 5: Altera Embedded Peripherals》和<%quartuspath%>/sopc_builder/components/altera_avalon_uart/inc/altera_avalon_uart_regs.h

中断行为(Interrupt Behavior)

UART核发送单独的中断请求信号给Avalon接口,这个接口可以连接到系统中如Nios II处理器一样的主要外围设备(a master peripheral)。这个主外围设备(a master peripheral)必须能够读取寄存器状态来处理中断请求。

The UART core outputs a single IRQ signal to the Avalon interface, which can connect to any master peripheral in the system, such as a Nios II processor. The master peripheral must read the status register to determine the cause of the interrupt.

任何一个中断源都在状态寄存器中有一个状态位,在控制寄存器中有一个中断允许位。当一个中断发生时,相对应的位被设置成1,直到执行状态寄存器写操作清除。当任意一个中断允许位被申明为1的时候,与之相关联的中断请求才能够发出。一个主外围设备(a master peripheral)通过清理状态寄存器可以感知中断请求。

Every interrupt condition has an associated bit in the status register and an interrupt-enable bit in the control register. When any of the interrupt conditions occur, the associated status bit is set to 1 and remains set until it is explicitly acknowledged. The IRQ output is asserted when any of the status bits are set while the corresponding interrupt-enable bit is 1. A master peripheral can acknowledge the IRQ by clearing the status register.

重新设置后,所有的中断允许位都将被设置成0。所以只有等到主外围设备(a master peripheral)将一个或多个中断允许位设置成1的时候,UART核才能发出中断请求。

At reset, all interrupt-enable bits are set to 0; therefore, the core cannot assert an IRQ until a master peripheral sets one or more of the interrupt-enable bits to 1.

后记:

第一次自己写这类东西,算是一个综合,希望能给各位初学Nios的朋友有些帮助。因为是边学边写,怕有些地方有误,希望有错的地方帮忙指出。非完全原创,有些是自己翻译,翻译的都附带了原文。

另附一篇文章给大家参考:http://www.freebsd.org/doc/en_US.ISO8859-1/articles/serial-uart/article.html

References:

《Interfacing the Serial /RS232 Port V5.0》

《嵌入式处理其原理及其应用—Nios系统设计和C语言编程》

《Quartus II Version 6.0 Handbook,Volume 5:Altera Embedded Peripherals》