- 单片机、嵌入式Linux开发大学自学路径

Oriental Son

嵌入式MCU单片机单片机学习stm32mculinux

笔者所修读的专业为物联网工程,物联网工程是一门新兴的、热门的专业,其所涉及的学科更是又多又杂,既有计算机方向的编程语言(如C、C++、Java、Python等)、数据结构与算法、操作系统、移动端应用开发、机器学习等;软硬结合的方向有数字电路单片机开发、嵌入式Linux开发等;硬件、电路方向有电路分析、数字电路、模拟电路、传感器原理、RFID、FPGA开发等;涉及信号处理的有信号与系统、通信原理等。

- PLC自动化工程师成长学习过程

crown6465

c语言

PLC自动化工程师成长学习路径:从入门到精通的五个阶段PLC(可编程逻辑控制器)是工业自动化领域的核心设备,PLC工程师需要具备跨学科的知识体系和实践能力。以下是PLC工程师从入门到精通的成长路径,分为五个阶段。第一阶段:基础知识储备(0-6个月)目标:建立自动化领域的基础理论框架。学科基础电工电子基础:学习电路分析、模拟/数字电路、电气元件(继电器、接触器、传感器)原理。自动化原理:理解控制理论

- Verilog 实现 FPGA 复杂算法的案例

百态老人

fpga开发

在数字电路设计领域,FPGA(现场可编程门阵列)因其灵活性和高性能而备受青睐。有许多利用Verilog实现FPGA复杂算法的案例。例如,有一个项目是在FPGA中用Verilog实现开方运算。该项目充分利用Verilog的强大功能,通过深入理解FPGA的内部结构优化代码资源利用率,采用经典数学算法确保计算结果的准确性和高效性。具有高效性、可移植性和易用性等优势,适用于对实时性要求较高的应用场景,为开

- Verilog 语法篇 硬件描述语言

7yewh

【FPGA知识点笔记汇总】fpga开发硬件工程驱动开发arm开发物联网iot

Verilog是一种硬件描述语言,用于设计、模拟和综合数字电路和系统。它主要用于描述ASIC(专用集成电路)或FPGA(现场可编程门阵列)等硬件设备的结构和行为。定义与用途:Verilog是一种硬件描述语言(HDL),主要用于数字电路的建模、仿真、综合与验证。设计人员利用它来描述电路的结构、行为以及时序关系,从而生成实际的硬件电路(如FPGA或ASIC)。发展背景:1984年,PhilMoorby

- 电路设计仿真软件:Eldo_(5).模拟与数字电路仿真技巧

kkchenjj

电路仿真模拟仿真仿真模拟电路仿真自动化

模拟与数字电路仿真技巧1.模拟电路仿真基础1.1电路仿真概述电路仿真软件如Eldo在现代电子设计自动化(EDA)中扮演着至关重要的角色。它允许设计师在实际制造之前对电路进行详细的模拟和测试,从而确保电路的性能和可靠性。Eldo支持多种类型的电路仿真,包括直流分析、交流分析、瞬态分析和噪声分析等。这些分析方法各自有不同的应用场景和特点。1.2直流分析直流分析是电路仿真中最基本的一种方法,主要用于分析

- Verilog基础(三):过程

TrustZone_

IC验证之旅fpga开发verilog

过程(Procedures)-Always块–组合逻辑(Alwaysblocks–Combinational)由于数字电路是由电线相连的逻辑门组成的,所以任何电路都可以表示为模块和赋值语句的某种组合.然而,有时这不是描述电路最方便的方法.两种alwaysblock是十分有用的:组合逻辑:always@(*)时序逻辑:always@(posedgeclk)always@(*)就相当于赋值语句–ass

- FPGA约束:如何生成时钟多路复用器及时钟约束?

编码实践

fpga开发matlab

FPGA约束:如何生成时钟多路复用器及时钟约束?在现代数字电路设计中,高速信号的传输对时钟信号的要求非常严格。设计者通常需要生成各种时钟信号,并为其指定合适的时钟约束。为了优化资源使用,FPGA中经常使用时钟多路复用器来同时提供多个时钟。本文将介绍如何使用VerilogHDL编写时钟多路复用器,并为其生成合适的时钟约束。时钟多路复用器的实现代码如下所示:moduleclk_mux#(paramet

- 电子信息工程专业学习过程中资料分享

莲月唯翼

学习电子信息工程单片机51单片机

①:一周搞定系列之模电链接:https://pan.baidu.com/s/1FGQvXCTbYqGVnsqL7Zb_nw?pwd=8888提取码:8888②:51单片机郭天祥十天学会单片机教学视频链接:https://pan.baidu.com/s/1tym6M-I8LFZa5rtdtH94hA?pwd=8888提取码:8888③:石油大学-《模拟电路》和《数字电路》视频教程各31集链接:htt

- ADC及DMA的使用原理和使用过程

Zack Zhou

linux运维服务器

ADC(Analog-DigitalConverter)模拟-数字转换器可以将引脚上连续变化的模拟电压转换为内存中存储的数字变量,建立模拟电路到数字电路的桥梁ADC主要用于传感器,传感器一般是利用电阻电容等测量外界信息的物理量,导致测量电路电压发生变化,产生模拟信号,二单片机只能读取数字信号,所以就需要我们把模拟信号转变为数字信号ADC的类型积分型:工作原理是将输入电压转换成时间(脉冲宽度信号)或

- 组合逻辑电路与时序逻辑电路的区别

@Luminescence

数字电路数电

组合逻辑电路和时序逻辑电路是数字电路设计中的两个基本类型,它们在功能和结构上有明显的区别。以下是对这两种电路的详细介绍:1.组合逻辑电路(CombinationalLogicCircuits)1.1定义组合逻辑电路的输出仅取决于当前输入信号的组合,而与过去的输入信号无关。换句话说,组合逻辑电路没有记忆功能。1.2特点无记忆元件:不包含存储元件(如触发器)。即时响应:输出信号即时响应输入信号的变化。

- 电磁兼容学习笔记12-电子设备中的主要骚扰源

胡你一脸团团团

学习笔记单片机

跟杨老师学习电磁兼容电子设备中的主要骚扰源#第16课典型的骚扰源(找du/dt、di/dt比较大的电路):骚扰源1:二次电源(几乎所有的电路都需要DC/DC),传导骚扰骚扰源2:数字电路,传导骚扰和辐射骚扰DC/DC模块骚扰产生原理:du/dt:开关导通时,直流电压直接传送到输出端;开关断开时,电流无法传送到输出端,依靠输出端电容进行供电。开关导通时,输出电压为0;断开时电容放电,开关上电压为输入

- 入门知识(JAVA基础)

一只藏羚吖

JAVA基础java开发语言

目录一、二进制二、变量的本质三、八种数据类型四、运算符1、算术运算符2、关系运算符3、逻辑运算符4、位运算符5、移位运算符6、条件运算符(三目操作符)五、类型转换一、二进制二进制(binary)是在数学和数字电路中以2为基数的记数系统,它使用两个不同的符号0(代表零)和1(代表一)来表示数值。二进制由德国数学家莱布尼茨在17世纪至18世纪提出,是现代计算机科学和数字电路的基础。二进制的特点主要有:

- 分频器code

一条九漏鱼

verilog开发实战指南fpga开发

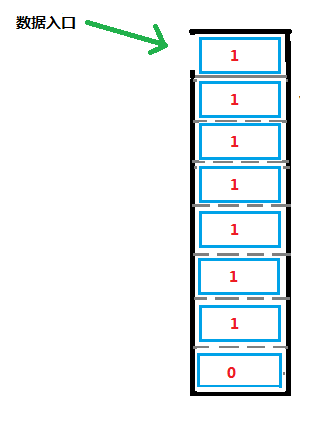

理论学习数字电路中时钟占有非常重要的地位。时间的计算都依靠时钟信号作为基本单元。一般而言,一块板子只有一个晶振,即只有一种频率的时钟,但是数字系统中,经常需要对基准时钟进行不同倍数的分频,进而得到各模块所需的频率。若想得到比系统时钟更慢的时钟,可以将基准时钟进行分频。若想得到比系统时钟更快的时钟,可以将基准时钟进行倍频。不管是分频还是倍频,都通过PLL实现或者用verilog描述实现。我们用ver

- 工业温湿度传感器芯片推荐

番茄老夫子

单片机嵌入式硬件

以下是一些工业温湿度芯片的推荐:一、SHT3x系列(如SHT30、SHT31、SHT35)特点:高精度:相对湿度测量精度可达±1.5%RH至±2%RH,温度测量精度可达±0.2℃至±0.3℃,能够满足大多数工业环境的高精度测量需求。宽电压范围:支持宽范围的供电电压,通常为2.15V至5.5V,适合不同的工业电源系统。通信接口:使用I2C接口,易于与微控制器或其他数字电路集成,通信协议简单,方便开发

- FPGA(Field-Programmable Gate Array,现场可编程门阵列)开发入门

MAMA6681

fpga开发

FPGA(Field-ProgrammableGateArray,现场可编程门阵列)开发入门是一个系统且深入的过程,涉及到硬件设计、编程语言、开发工具等多个方面。以下是一个简要的FPGA开发入门指南:一、基础知识准备数字电路与逻辑设计:了解数字电路的基本概念,如二进制、逻辑门电路、组合逻辑电路、时序逻辑电路等。熟悉布尔代数和逻辑门的功能及其实现方法。计算机体系架构:掌握CPU、内存、外设、总线等计

- 零基础怎么学习单片机?

an520_

c语言嵌入式开发stm32单片机学习嵌入式硬件stm32c语言

一般来说,想要学习单片机,很多也是因为嵌入式的原因,但是既然都选择学习单片机了,那么学习的内容就是要对单片机的硬件结构有所了解。第一步:数字I/O的应用在大多数的单片机实验中,跑马灯实验正是数字I/O的典型应用,也是跑马灯的实验被安排第一个的原因。通过将单片机的I/O引脚位进行置位或清零来点亮或关闭LED灯,虽然简单,但是这就是数字电路中的逻辑功能。数学I/O应用的实验还有按键实验,当按下某键时,

- Quartus网盘资源下载与安装 附图文安装教程

学习天使Alice

fpga开发学习

如大家所了解的,Quartus是一种FPGA设计软件(相信理工科的小伙伴,很多都接触或学习过FPGA),旨在为数字电路设计师提供一个高效、便捷的开发环境。它可以帮助用户完成数字逻辑电路的设计、仿真、综合和布局,以及与外围设备进行通信和控制。Quartus支持多种编程语言,包括VHDL、Verilog等,并具有丰富的功能和工具库,可满足不同级别、不同规模的数字电路设计需求。收藏的Quartus安装包

- 数字电路中卡诺图理解

Lambor_Ma

数字

简单理解就是,卡诺图是用来化简数字逻辑的图表,它将不同输入变量的组合枚举到图表中,然后填入是否为1或者0.化简有2种方式1种是SOP一种是POS。SOPsumofproducts就是P=ab+bc+abc这种形式化简方法为:1.圈出相邻的1(4个角也可以认为是相邻的)2.化简写出每个圈的最简式子3.将最简式相加举例假设A圈是BD构成,B圈是B’D’构成,则最后结果是BD+B’D’POSproduc

- 硬件工程师必须掌握的MOS管详细知识

硬件大脑

通信领域知识硬件工程射频工程信息与通信硬件架构嵌入式硬件

MOS管,全称为金属-氧化物半导体场效应晶体管(Metal-Oxide-SemiconductorField-EffectTransistor,MOSFET),是一种重要的半导体器件,广泛应用于电子工业中各种电路的开关、放大、调制、数字电路和模拟电路等领域。以下是对MOS管的详细知识介绍:一、定义与结构定义:MOS管是一种利用电场效应来控制其电流大小的半导体三端器件。它由金属栅极(G)、氧化物绝缘

- 笔试题-2023-思特威-数字电路设计(CIS)【纯净题目版】

lu-ming.xyz

2023面试实录面经刷题秋招数字IC设计

回到首页:2023数字IC设计秋招复盘——数十家公司笔试题、面试实录推荐内容:数字IC设计学习比较实用的资料推荐题目背景笔试时间:2022.08.18笔试时长:90min应聘岗位:数字电路设计工程师(CIS)笔试平台:showmebug题目评价难易程度:★★☆☆☆知识覆盖:★☆☆☆☆超纲范围:☆☆☆☆☆值得一刷:★☆☆☆☆文章目录1数字IC设计的流程包含哪些?2简述下D-Latch与D-Flipf

- 1.【Multisim仿真】数电模电学习,仿真软件的初步使用

m0_61659911

学习

学习计划路径:>Multisim电路仿真软件熟练掌握>数字电路基础课程>逻辑电路设计与应用>熟练掌握存储器、脉冲波形发生器、D/A和A/D转换器原理>基本元器件熟练掌握>晶体管放大电路及负反馈放大电路>集成运算放大器设计>电压变电流电路设计>绝对值电路设计>压力传感器电路设计>STM32最小系统设计一。Multisim仿真初步了解1.主页功能布置二。数字电路设计基础1.正逻辑与负逻辑1.数字信号是

- 基于Qt的RTL可视模拟器(VSRTL)配置

吹角连营G

qtubuntu系统架构

文章目录VSRTL介绍Qt5.15.2安装构建VSRTLVSRTL介绍寄存器传输逻辑的可视模拟器(VisualSimulationofRegisterTransferLogic,VSRTL)是一个可以描述、可视化和仿真数字电路的框架。VSRTL描述的电路可以作为独立的应用,也可以嵌入到基于Qt的C++应用中。基于RISC-V指令集的模拟器Ripes即使用VSRTL开发。VSRTL依赖于C++17工

- 【蓝桥杯单片机入门记录】认识单片机

La_gloire

51单片机单片机51单片机

目录单片机硬件平台单片机的发展过程单片机开发板单片机基础知识电平数字电路中只有两种电平:高和低二进制(8421码)十六进制二进制数的逻辑运算“与”“或”“异或”标准C与C51如何学好单片机端正学习的态度、培养自学能力、要有远大的目标要有学习的恒心、面对挫折的准备树立起学习勇气要追求质量而非速度,基础部分知识量大而小且必须无论简单还是复杂的程序,一定要自己写出无论出现什么样的错误,一定要找到错在哪多

- 普中51单片机学习(二)

Ccjf酷儿

51单片机学习嵌入式硬件

51单片机介绍所需基础知识基础数模电知识,简单的C语言。PS:如果有不懂的直接通义千问。。。什么是单片机在一片集成电路芯片上集成微处理器、存储器、I/O接口电路,从而构成了单芯片微型计算机,即单片机。学习方法多实践;学习必要的理论知识;多做项目工程。预备知识电平特性数字电路只有两种电平,高电平和低电平;高电平5V或3.3V,取决于单片机电源;低电平0V;RS232电平:计算机串口电平;高电平12V

- 一种基于IPsec的VXLAN“专线”解决方案

Danileaf_Guo

网络服务器运维linux

正文共:888字14图,预估阅读时间:1分钟我们前面曾经做过一个小实验(VXLAN小实验:降本增效,将MV互联网专线伪装成数字电路),那就是将互联网专线伪装成数字电路。实现的方案就是将具有公网IP地址的设备作为VXLAN的VTEP,采用VXLAN头端复制的方式,实现两端互联IP的直接通信。从上次的测试结果来看,传输带宽基本可以跑满,并且VXLAN封装对业务几乎无感知。但是受互联网传输的影响,实际链

- 专业140+总分420+浙江大学842信号系统与数字电路考研经验电子信息与通信,真题,大纲,参考书。

一个通信老学姐

博睿泽信息通信考研论坛博睿泽信息通信考研考研信息与通信信号处理经验分享

今年考研已经结束,初试专业课842信号系统与数字电路140+,总分420+,很幸运实现了自己的目标,被浙大录取,这在高考是想都不敢想的学校,在考研时实现了,所以大家也要有信心,通过自己努力实现逆袭,我觉得考研也是非常公平的,也是我们普通同学的上升通道,很多大佬都保研了,并不是参加考研,所以大家抓住机会,提高自己的平台。专业课:专业课842信号系统与数字电路140+算是圆满完成了自己的目标(信息通信

- 嵌入式系统设计

return_lin0

stm32嵌入式硬件物联网单片机

加粗样式@TOC一.电路(模拟电路、数字电路、PCB设计)1.超级电容错误:加载主类com.intellij.idea.Main时出现LinkageErrorjava.lang.UnsupportedClassVersionError:com/intellij/idea/MainhasbeencompiledbyamorerecentversionoftheJavaRuntime(classfil

- 利用多目标粒子群优化(MOPSO)算法对全加器中的晶体管大小进行重新调整以达到功率优化:详细步骤与Python实现

快撑死的鱼

python算法解析算法python开发语言

简介:随着技术的不断进步,微电子行业始终追求在保持性能的同时降低功率消耗。全加器作为数字电路中的基本元素,其功率优化显得尤为关键。本文将详细介绍如何使用一种称为多目标粒子群优化(MOPSO)的进化算法,重新调整晶体管的大小,以优化全加器中的功率。此外,我们还将提供Python代码实现,供读者参考和使用。具体的项目实现过程,我们已经准备了一个完整的项目文件,您可以下载以获取更多细节。1.多目标粒子群

- Verilog和Verilog-A有什么区别

幻象空间的十三楼

ASM-HEMTIC-CAP器件建模器件学习IC-CAP软件学习ADS软件学习

Verilog和Verilog-A都是硬件描述语言,用于设计和仿真电子系统。Verilog是一种硬件描述语言,广泛用于数字电路的设计、验证和仿真。它是一种结构化的语言,用于描述数字电路的行为和结构。Verilog可用于编写数字逻辑、寄存器传输级(RTL)设计、门级电路和系统级设计。Verilog-A是Verilog的扩展,专门用于建模和仿真模拟电路。它提供了描述和仿真模拟电路的能力,包括模拟器件、

- 【转载】高速信号关键信号的布线要求

山里天空蓝

高速设计关键信号时钟接口

关键信号的识别关键信号通常包括以下信号:时钟信号(*CLK*),复位信号(*rest*,*rst*),JTAG信号(*TCK*)部分关键信号布线要求汇总一、时钟信号布线要求在数字电路设计中,时钟信号是一种在高态与低态之间振荡的信号,决定着电路的性能。时钟电路在数字电路中点有重要地位,同时又是产生电磁辐射的主要来源。时钟的处理方法也是在PCB布线时需要特别重视的。在一开始就理清时钟树,明确各种时钟之

- java数字签名三种方式

知了ing

javajdk

以下3钟数字签名都是基于jdk7的

1,RSA

String password="test";

// 1.初始化密钥

KeyPairGenerator keyPairGenerator = KeyPairGenerator.getInstance("RSA");

keyPairGenerator.initialize(51

- Hibernate学习笔记

caoyong

Hibernate

1>、Hibernate是数据访问层框架,是一个ORM(Object Relation Mapping)框架,作者为:Gavin King

2>、搭建Hibernate的开发环境

a>、添加jar包:

aa>、hibernatte开发包中/lib/required/所

- 设计模式之装饰器模式Decorator(结构型)

漂泊一剑客

Decorator

1. 概述

若你从事过面向对象开发,实现给一个类或对象增加行为,使用继承机制,这是所有面向对象语言的一个基本特性。如果已经存在的一个类缺少某些方法,或者须要给方法添加更多的功能(魅力),你也许会仅仅继承这个类来产生一个新类—这建立在额外的代码上。

- 读取磁盘文件txt,并输入String

一炮送你回车库

String

public static void main(String[] args) throws IOException {

String fileContent = readFileContent("d:/aaa.txt");

System.out.println(fileContent);

- js三级联动下拉框

3213213333332132

三级联动

//三级联动

省/直辖市<select id="province"></select>

市/省直辖<select id="city"></select>

县/区 <select id="area"></select>

- erlang之parse_transform编译选项的应用

616050468

parse_transform游戏服务器属性同步abstract_code

最近使用erlang重构了游戏服务器的所有代码,之前看过C++/lua写的服务器引擎代码,引擎实现了玩家属性自动同步给前端和增量更新玩家数据到数据库的功能,这也是现在很多游戏服务器的优化方向,在引擎层面去解决数据同步和数据持久化,数据发生变化了业务层不需要关心怎么去同步给前端。由于游戏过程中玩家每个业务中玩家数据更改的量其实是很少

- JAVA JSON的解析

darkranger

java

// {

// “Total”:“条数”,

// Code: 1,

//

// “PaymentItems”:[

// {

// “PaymentItemID”:”支款单ID”,

// “PaymentCode”:”支款单编号”,

// “PaymentTime”:”支款日期”,

// ”ContractNo”:”合同号”,

//

- POJ-1273-Drainage Ditches

aijuans

ACM_POJ

POJ-1273-Drainage Ditches

http://poj.org/problem?id=1273

基本的最大流,按LRJ的白书写的

#include<iostream>

#include<cstring>

#include<queue>

using namespace std;

#define INF 0x7fffffff

int ma

- 工作流Activiti5表的命名及含义

atongyeye

工作流Activiti

activiti5 - http://activiti.org/designer/update在线插件安装

activiti5一共23张表

Activiti的表都以ACT_开头。 第二部分是表示表的用途的两个字母标识。 用途也和服务的API对应。

ACT_RE_*: 'RE'表示repository。 这个前缀的表包含了流程定义和流程静态资源 (图片,规则,等等)。

A

- android的广播机制和广播的简单使用

百合不是茶

android广播机制广播的注册

Android广播机制简介 在Android中,有一些操作完成以后,会发送广播,比如说发出一条短信,或打出一个电话,如果某个程序接收了这个广播,就会做相应的处理。这个广播跟我们传统意义中的电台广播有些相似之处。之所以叫做广播,就是因为它只负责“说”而不管你“听不听”,也就是不管你接收方如何处理。另外,广播可以被不只一个应用程序所接收,当然也可能不被任何应

- Spring事务传播行为详解

bijian1013

javaspring事务传播行为

在service类前加上@Transactional,声明这个service所有方法需要事务管理。每一个业务方法开始时都会打开一个事务。

Spring默认情况下会对运行期例外(RunTimeException)进行事务回滚。这

- eidtplus operate

征客丶

eidtplus

开启列模式: Alt+C 鼠标选择 OR Alt+鼠标左键拖动

列模式替换或复制内容(多行):

右键-->格式-->填充所选内容-->选择相应操作

OR

Ctrl+Shift+V(复制多行数据,必须行数一致)

-------------------------------------------------------

- 【Kafka一】Kafka入门

bit1129

kafka

这篇文章来自Spark集成Kafka(http://bit1129.iteye.com/blog/2174765),这里把它单独取出来,作为Kafka的入门吧

下载Kafka

http://mirror.bit.edu.cn/apache/kafka/0.8.1.1/kafka_2.10-0.8.1.1.tgz

2.10表示Scala的版本,而0.8.1.1表示Kafka

- Spring 事务实现机制

BlueSkator

spring代理事务

Spring是以代理的方式实现对事务的管理。我们在Action中所使用的Service对象,其实是代理对象的实例,并不是我们所写的Service对象实例。既然是两个不同的对象,那为什么我们在Action中可以象使用Service对象一样的使用代理对象呢?为了说明问题,假设有个Service类叫AService,它的Spring事务代理类为AProxyService,AService实现了一个接口

- bootstrap源码学习与示例:bootstrap-dropdown(转帖)

BreakingBad

bootstrapdropdown

bootstrap-dropdown组件是个烂东西,我读后的整体感觉。

一个下拉开菜单的设计:

<ul class="nav pull-right">

<li id="fat-menu" class="dropdown">

- 读《研磨设计模式》-代码笔记-中介者模式-Mediator

bylijinnan

java设计模式

声明: 本文只为方便我个人查阅和理解,详细的分析以及源代码请移步 原作者的博客http://chjavach.iteye.com/

/*

* 中介者模式(Mediator):用一个中介对象来封装一系列的对象交互。

* 中介者使各对象不需要显式地相互引用,从而使其耦合松散,而且可以独立地改变它们之间的交互。

*

* 在我看来,Mediator模式是把多个对象(

- 常用代码记录

chenjunt3

UIExcelJ#

1、单据设置某行或某字段不能修改

//i是行号,"cash"是字段名称

getBillCardPanelWrapper().getBillCardPanel().getBillModel().setCellEditable(i, "cash", false);

//取得单据表体所有项用以上语句做循环就能设置整行了

getBillC

- 搜索引擎与工作流引擎

comsci

算法工作搜索引擎网络应用

最近在公司做和搜索有关的工作,(只是简单的应用开源工具集成到自己的产品中)工作流系统的进一步设计暂时放在一边了,偶然看到谷歌的研究员吴军写的数学之美系列中的搜索引擎与图论这篇文章中的介绍,我发现这样一个关系(仅仅是猜想)

-----搜索引擎和流程引擎的基础--都是图论,至少像在我在JWFD中引擎算法中用到的是自定义的广度优先

- oracle Health Monitor

daizj

oracleHealth Monitor

About Health Monitor

Beginning with Release 11g, Oracle Database includes a framework called Health Monitor for running diagnostic checks on the database.

About Health Monitor Checks

Health M

- JSON字符串转换为对象

dieslrae

javajson

作为前言,首先是要吐槽一下公司的脑残编译部署方式,web和core分开部署本来没什么问题,但是这丫居然不把json的包作为基础包而作为web的包,导致了core端不能使用,而且我们的core是可以当web来用的(不要在意这些细节),所以在core中处理json串就是个问题.没办法,跟编译那帮人也扯不清楚,只有自己写json的解析了.

- C语言学习八结构体,综合应用,学生管理系统

dcj3sjt126com

C语言

实现功能的代码:

# include <stdio.h>

# include <malloc.h>

struct Student

{

int age;

float score;

char name[100];

};

int main(void)

{

int len;

struct Student * pArr;

int i,

- vagrant学习笔记

dcj3sjt126com

vagrant

想了解多主机是如何定义和使用的, 所以又学习了一遍vagrant

1. vagrant virtualbox 下载安装

https://www.vagrantup.com/downloads.html

https://www.virtualbox.org/wiki/Downloads

查看安装在命令行输入vagrant

2.

- 14.性能优化-优化-软件配置优化

frank1234

软件配置性能优化

1.Tomcat线程池

修改tomcat的server.xml文件:

<Connector port="8080" protocol="HTTP/1.1" connectionTimeout="20000" redirectPort="8443" maxThreads="1200" m

- 一个不错的shell 脚本教程 入门级

HarborChung

linuxshell

一个不错的shell 脚本教程 入门级

建立一个脚本 Linux中有好多中不同的shell,但是通常我们使用bash (bourne again shell) 进行shell编程,因为bash是免费的并且很容易使用。所以在本文中笔者所提供的脚本都是使用bash(但是在大多数情况下,这些脚本同样可以在 bash的大姐,bourne shell中运行)。 如同其他语言一样

- Spring4新特性——核心容器的其他改进

jinnianshilongnian

spring动态代理spring4依赖注入

Spring4新特性——泛型限定式依赖注入

Spring4新特性——核心容器的其他改进

Spring4新特性——Web开发的增强

Spring4新特性——集成Bean Validation 1.1(JSR-349)到SpringMVC

Spring4新特性——Groovy Bean定义DSL

Spring4新特性——更好的Java泛型操作API

Spring4新

- Linux设置tomcat开机启动

liuxingguome

tomcatlinux开机自启动

执行命令sudo gedit /etc/init.d/tomcat6

然后把以下英文部分复制过去。(注意第一句#!/bin/sh如果不写,就不是一个shell文件。然后将对应的jdk和tomcat换成你自己的目录就行了。

#!/bin/bash

#

# /etc/rc.d/init.d/tomcat

# init script for tomcat precesses

- 第13章 Ajax进阶(下)

onestopweb

Ajax

index.html

<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3.org/TR/xhtml1/DTD/xhtml1-transitional.dtd">

<html xmlns="http://www.w3.org/

- Troubleshooting Crystal Reports off BW

blueoxygen

BO

http://wiki.sdn.sap.com/wiki/display/BOBJ/Troubleshooting+Crystal+Reports+off+BW#TroubleshootingCrystalReportsoffBW-TracingBOE

Quite useful, especially this part:

SAP BW connectivity

For t

- Java开发熟手该当心的11个错误

tomcat_oracle

javajvm多线程单元测试

#1、不在属性文件或XML文件中外化配置属性。比如,没有把批处理使用的线程数设置成可在属性文件中配置。你的批处理程序无论在DEV环境中,还是UAT(用户验收

测试)环境中,都可以顺畅无阻地运行,但是一旦部署在PROD 上,把它作为多线程程序处理更大的数据集时,就会抛出IOException,原因可能是JDBC驱动版本不同,也可能是#2中讨论的问题。如果线程数目 可以在属性文件中配置,那么使它成为

- 正则表达式大全

yang852220741

html编程正则表达式

今天向大家分享正则表达式大全,它可以大提高你的工作效率

正则表达式也可以被当作是一门语言,当你学习一门新的编程语言的时候,他们是一个小的子语言。初看时觉得它没有任何的意义,但是很多时候,你不得不阅读一些教程,或文章来理解这些简单的描述模式。

一、校验数字的表达式

数字:^[0-9]*$

n位的数字:^\d{n}$

至少n位的数字:^\d{n,}$

m-n位的数字:^\d{m,n}$