ISE中启动modelsim时出现了下面的错误

1。我在ISE中启动modelsim时出现了下面的错误

Loading work.tb_ic1_func

# ** Error: (vsim-19) Failed to access library 'xilinxcorelib_ver' at "xilinxcorelib_ver".

# No such file or directory. (errno = ENOENT)

# ** Error: (vsim-19) Failed to access library 'unisims_ver' at "unisims_ver".

# No such file or directory. (errno = ENOENT)

# Loading work.fifoctlr_ic_v2

# ** Error: (vsim-19) Failed to access library 'xilinxcorelib_ver' at "xilinxcorelib_ver".

# No such file or directory. (errno = ENOENT)

# ** Error: (vsim-19) Failed to access library 'unisims_ver' at "unisims_ver".

# No such file or directory. (errno = ENOENT)

# ** Error: (vsim-3033) fifoctlr_ic_v2.v(126): Instantiation of 'BUFGP' failed. The design unit was not found.

是什么原因?

“点到仿真模式,在source里面选中你建立工程选择的芯片,然后看Processes,点开,有个compile HDL simulation library,运行一下就OK了”

2.ISE用modelsim仿真提示:# ** Error: (vish-4014) No objects found matching '*'.结果仿真时老是报错:

# ** Error: (vish-4014) No objects found matching '*'.

# Error in macro ./test_top_tb.fdo line 10

# (vish-4014) No objects found matching '*'.

# while executing

# "add wave *"

解决办法,改modelsim.ini文件中的一个参数:VoptFlow = 0

倘若不行,后来又搜到一种方法,我试了一下,可以解决问题:

点击工具栏中的“simulate”按钮,或用菜单中的命令“simualte->start simulation”调出start smulation窗口,关键是把窗口中最下边optimization栏中的Enable optimization项目前的钩钩去掉,然后选择仿真的文件,点击OK,就一切正常了,能看到objects了。

3.当对IP核修改后,用Modelsim仿真显示:No entity is bound for inst 或 CE is not in the entity。(CE是改动后添加的一个管脚),从而仿真无结果。

解决办法:首先选中该IP核的.xco文件点击右键->属性 将属性改为 "Synthesis/Imp + Simulation."

然后将其对应的.v或.vhd文件的属性也改为 "Synthesis/Imp + Simulation."

4.启动modelsim后,没有出错,但是有warning:(vsim-3009) [TSCALE] - Module 'ODDR' does not have a `timescale directive in effect, but previous modules do.输入信号均正确,调用的IP core或原语的输出为高阻态。

解决办法:modelsim中调用该IP core或原语的库不匹配,在xilinx中找到其所在的库unisims,并重新编译至modelsim的UNISIMS_VER库中。问题可得到解决。

2013-06-28 08:59:44周五

来源:http://blog.csdn.net/jbb0523/article/details/7932026

在ModelSim中执行View---FSM list命令,代码中所有状态机会生成一个列表。如何你想观察哪个状态机,直接双击就可以打开它。

这时观察生成的状态转换图发现,所有的状态都在复位的情况下返回了状态IDLE,这是我们不期望的,仔细观察这时的菜单栏可以发现,有一个FSM View项。将Show Transitions to "Reset"项前面的对勾去掉,就会发现不显示复位情况下返回状态IDLE了。

来源:http://wjfblack.blog.163.com/blog/static/18005148420117240336431/

保存仿真用了很长时间的波形,方便下次打开直接看,无需再花时间去跑一趟。且也可以用于比较。

1、在wave界面,将仿真波形保存为 .do文件(信号文件)。

2、切换左边任务栏至“sim”,,点击保存,给将要保存的 .wlf文件(波形文件)命名。

3、保存,OK,关闭modelsim.

4、重启modelsim,open 之前保存的 .wlf文件,然后 load 对应的 .do文件。

5、enjoy。

来源:http://www.cnblogs.com/nanoty/archive/2012/10/29/2745463.html

关于Modelsim仿真时不能编译`include文件解决办法【Verilog】【Modelsim】

问题描述:

只要用到include,编译就出错,抱怨Cannot open `include file "params.v",但是在使用params.v文件中定义的参数时,已经在调用文件中使用了“`include params.v”命令,如果在其他文件夹中进行编译,仿真器就会报出“cannot open。。。”或者找不到params.v中定义相应的参数。

解决办法:

- 将所有要编译文件放在同一个文件夹中,且编译时在该文件夹中进行编译;

- 使用include命令时,使用绝对路径对文件进行引用;

2013-02-23 08:32:06

来源:http://www.cnblogs.com/emouse/archive/2012/07/08/2581223.html 此博客描写了QuartusII调用ModelsimSE的两种方法,第一种是修改系统产生的*.vt测试激励,对仿真产生的DO文件(含库文件编译、设计文件编译、运行参数及开始)。同时还讲解了DO文件的修改,可以添加中间信号进行考察,可以免去库文件的编译。在免去库文件的编译时,首先在QII上一次性编译库(tool-launch EDA simulation Library Compiler ),然后返回QII的仿真设计界面(Assignment-settingèsimulation-more Nativelink setting )设定好刚才编译好的库路径。

但针对激励是多个文件时,仿真功能的设计并没有说明,所以问题暂时没解决,不过它也间接解决了问题,你可以采用上面这种方法来直接调用modelsim,省去库的编译。

2013-02-22 16:20:01

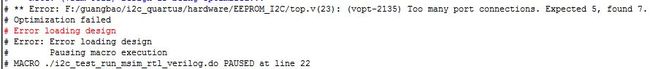

问题:在用QuartusII直接调用ModelsimSE进行仿真时,当测试激励是由多个文件组成时,就仿真不通过,提示的错误信息如下所示:

# ** Error: F:/guangbao/i2c_quartus/hardware/EEPROM_I2C/top.v(23): (vopt-2135) Too many port connections. Expected 5, found 7.

# Optimization failed

# Error loading design

# Error: Error loading design

# Pausing macro execution

# MACRO ./i2c_test_run_msim_rtl_verilog.do PAUSED at line 22

答案:

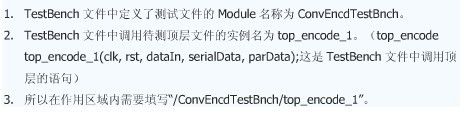

停止在22句上,第22句是vsim -t 1ps -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L arriav_ver -L arriav_hssi_ver -L arriav_pcie_hip_ver -L rtl_work -L work -voptargs="+acc" top

手动修改成 vsim -novopt work.top就可以仿真,不知道上面那句有什么错误,???待解答。

来源:http://www.ourdev.cn/thread-4814017-1-1.html

问题:

1、直接用Modelsim做仿真用.v文件,在Quartus下调用modelsim-altera仿真确是调用.vt文件。尝试了下直接把后缀改了交换用,不行!这很不方便啊,有没有什么好办法?

2、做功能仿真时要把Simulate->start simulate ->Design里的enable optimization设成无效,否则出不来波形。为什么?

3、做时序仿真时出现如下错误:Error:(vsim-SDF-3250)E:/.../counter_v.sdo(0):Failed to find INSTANCE 'counter_tb/counter'.

这貌似是个老问题了,试了网友说的各种办法,无效!添加SDF时Apply to Region也试了各种写法。比如:在“/”前写测试文件名,后写顶层例化名。

(我的测试文件名是counter_tb.v,模块名是counter_tb;功能实现文件是counter.v,模块名是counter在测试文件里的例化名是counter)。我试了这样写:counter_tb/counter这样写:counter/counter或这样写:/counter,都不行!

如果把Disable SDF warnings和Reduce SDF errors to warnings 都选上,波形倒能出来,但没有逻辑延时信息,也就是说.sdo里的信息没参与仿真,相当于只做了功能仿真。

回答:

modelsim 的默认testbench 后缀就是.vt的,要不就手动打开modelsim自己做编译。

1、优化过后一般都会综合掉一些软件认为中间多余的寄存器,所以波形出不来

2、将SDF 文件复制到和网表同一个目录就行。

3、重点是作用区域的命名规范,我在这花了很长时间,信息来源:http://wenku.baidu.com/view/46d3e14d2b160b4e767fcf88.html