aurix中AD采样

ADC的频率也是连接SPB频率的。

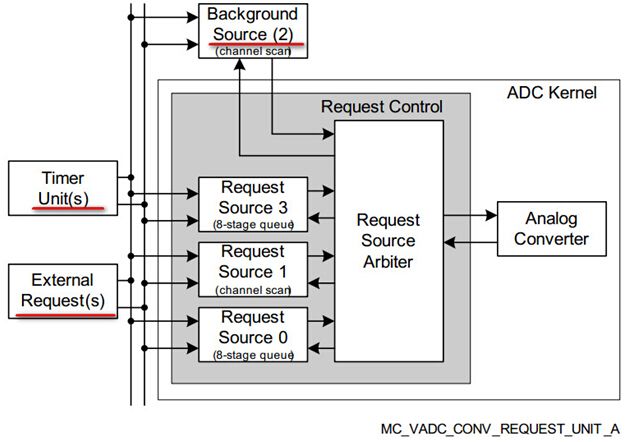

AD转换过程通过background 请求、Timer单元请求、外部请求三种来请求AD转换。如下:

而来自Backgroud的请求,只能是在没有任何一个AD group被占用时请求响应。其具有转换的最低优先级。

同时对于请求源的仲裁采用优先级的方式,而对中断优先级的处理有如下几种:

1、cancel-inject-repeat mode直接中断当前转换,高优先级抢占低优先级

2、wait-for-startmode等待当前AD转换完成后立即转换

3、wait-for-read mode如果结果寄存器没被读,则延迟等待读完后再AD转换。

而AD转换的方式有三种通道仲裁方式:

1、fixed channel conversion

2、Auto scan conversion

3、Channel sequence conversion

中断事件(也就是在如下各个阶段都可以触发事件给CPU或DMA):

Source events—-》转换序列排列完成后触发事件,可以用在建立新的转换顺序

Channel event—》指定通道转换完成后触发事件,中断后可以获取转换完的值

Result event—-》当结果寄存器中更新新值时在data reduction mode下触发事件

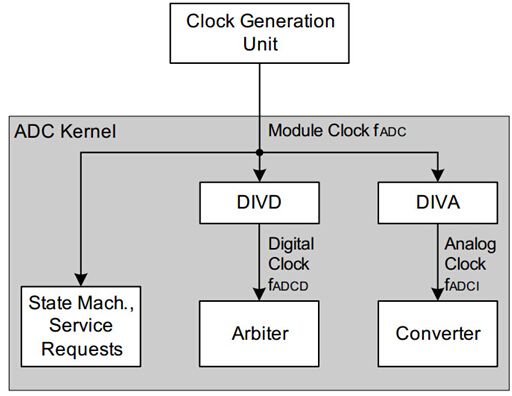

AD相关的时钟源

AD时钟基于SPB频率,设置GLOBCFG寄存器

由图可以看到,AD的时钟涉及两部分:

DIVA:模拟时钟(AD转换时钟,默认是20M)

DIVD:数字时钟(仲裁时钟,设置和SPB频率一致)

ADC模块还包含一些保护策略,防止adc的寄存器位发生不可预知的写访问。

对AD补偿的设置:

1、在GLOBCFG中设置了SUSL位,startup了calibration

2、需要检测查看对应AD group中的ARBCFG寄存器中CAL位是否被激活,激活表明calibration开启成功。

通过ACCPROT0/1对一些寄存器的写访问权限可以进行控制。

对于AD Group 的设置:

首先是请求源,包括如下几种请求源:

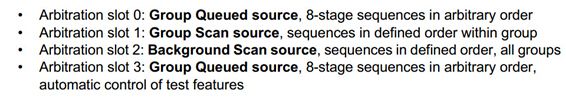

通过GxARBPR寄存器可以设置:

三个请求源的优先级(数字越大优先级越高)、是否加入仲裁round、启动AD转换的模式。

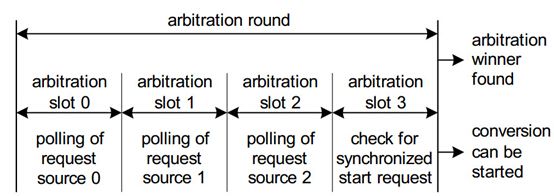

关于请求源仲裁时间:

The duration of an arbitration slot is configurable tSlot = (DIVD+1) / fADC.

The duration of an arbitration round, therefore, is tARB = 4 × tSlot (or 8×tSlot).

上图显示的仲裁时间,就是在一个仲裁周期中划分仲裁时间,可以分为4、8、12个等分,每个等分的时间也会缩短。

请求方式:

Queue source

scan source

其中scan 方式有分为group-specify和global

在Request queue中,仲裁器按照优先级中仲裁的序列组成队列,如果在cancel-inject-repeat mode模式下直接被中断,原来未转换完的并不会被丢弃,而是backup等待下一次转换。

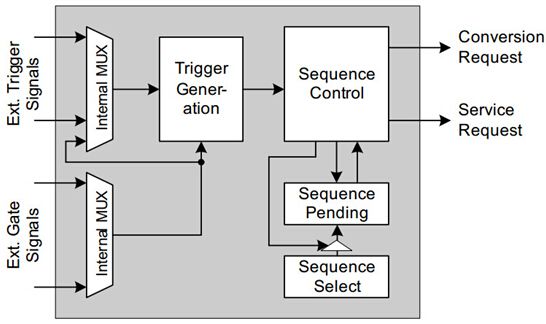

开启触发方式分为软件触发和外部触发

在配置时,需要按想要的顺序将请求源加入队列,

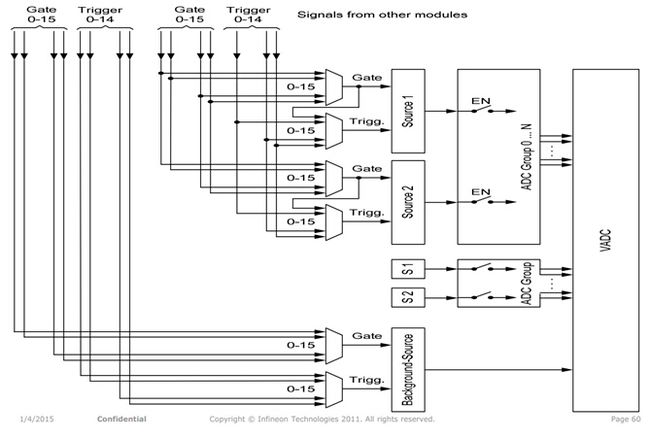

然后根据需求设置Gate 和trigger的模式和源

设置触发源和触发方式

在Request scan中,则是从按照通道号逐个扫描。

首先scan mode下,存在的请求源包括group request source 和background source。

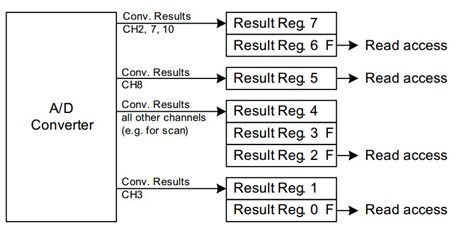

AD中结果寄存器:

在GxRESx寄存器中放结果值

•

关于执行请求转换的条件:

Queue 下,如果要能转换,可以选择不判断Gate input(GxQSR0寄存器),queue0值直接pending就转化,也可以加个Gate input条件。根据mode设置来进行

IfxVadc_GatingMode_disabled = 0, /**< \brief Gating is disabled, no conversion request are issued */

IfxVadc_GatingMode_always = 1, /**< \brief Conversion request is issued if at least 1 conversion pending bit is set */

IfxVadc_GatingMode_gatingHigh = 2, /**< \brief Conversion request is issued if at least 1 conversion pending bit is set and the gating signal is high */

IfxVadc_GatingMode_gatingLow = 3 /**< \brief Conversion request is issued if at least 1 conversion pending bit is set and the gating signal is low */等于说在转换着加了一个与逻辑,由Gate控制,也可以选择不控制。

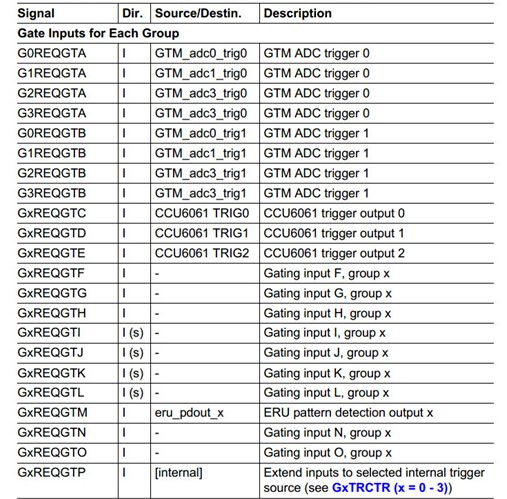

而Gate input的来源参考下表:

其中在Backgroud scan模式下也有这样的Gate

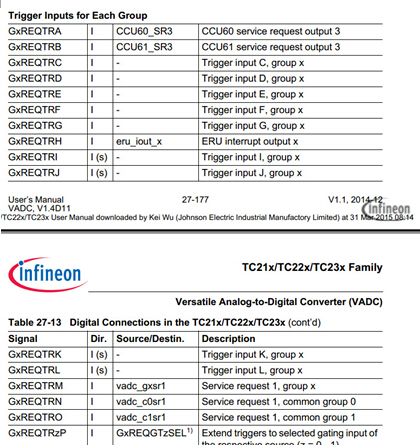

同时触发源则是按照如上的列表:

默认没有使用Gate,只有触发源输入,触发源见下表,常用pwm作为触发源进行ad采样

初始化channel

转换模式:

1、标准转换模式

2、Fast compare mode

对于最终值的处理包括:

FIFO:关于结果寄存器的使用,可以一一对应channel,也可以用结果寄存器组成FIFO。

通过设置GxRCRy.FEN = 01B,将相邻的结果寄存器联系起来

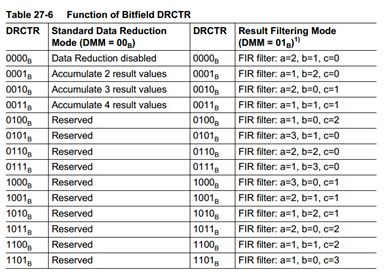

累加、滤波、限幅检测三种处理

需要滤波处理,修改如下寄存器:

边界限幅检测,在大于或小于边界时会产生flag的变化。

AD数据对齐方式就如下面的方式:

配置好channel将channel加入到queue中,然后等待触发事件

也可以通过

IFX_INLINE void IfxVadc_startQueue(Ifx_VADC_G *group)

{

group->QMR0.B.TREV = 1;

}

手动触发产生软件事件。

关于AD中断的设置,代码中演示了转换完后触发中断的函数,制定中断触发的CPU。

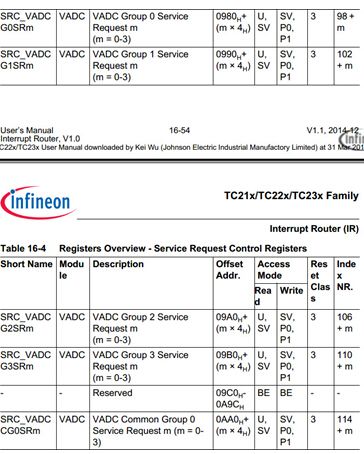

AD相关的事件触发,每个AD 有4个group-specific service request output signals和4个shared service request output signals。

能触发cpu中断或DMA:

有如下的三个典型事件能产生AD事件触发中断:

Request source events(请求源完成请求转换的序列排序)

Channel events(转换完成触发)

Result events(结果寄存器值更新触发)

一般只用后两个

因为每个AD规定的典型事件都需要通过某个service request output signal去连接SRN,

所以还需要按照下面的表,设置对应service request output signal接口的寄存器SRC

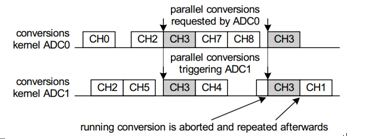

并行采样的同步转换:

确保相关通道的采样阶段同步开启。

需要定义一个AD为master 一个为Slave,同步采样触发。

Master的配置:

1、需要将仲裁器一直打开(GxARBCFG (x = 0 - 3).ARBM = 0)

2、需要设置GxSYNCTR寄存器中STSEL位,设置master和slave.

3、同时AD master在收到请求某个通道的时候,slave也会被请求。注意对应channel中GxCHCTRy的SYNC要被置1。

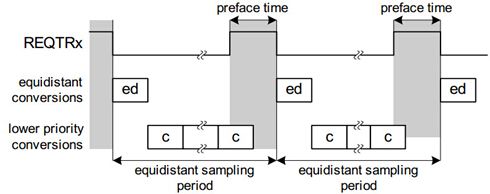

等间隔采样:

设置GxQCTRL0 (x = 0 - 3) 或者GxASCTRL (x = 0 -3) )中的TMEN位,开启等间隔模式,出现如下效果:

如何用结果寄存器组成FIFO?

只能配置序号连续的结果寄存器把他们组合起来,如下图:

从上图可以看到去result值是从index序号较小的reg读,至于存放的顺序,则

主要就是设置结果寄存器的控制寄存器GxRCRy,配置对应的结果寄存器。

主要就是GxRCRy寄存器中的FEN位