基于FPGA的呼吸灯设计

一:背景介绍:

网上类似的标题很多,有一些呼吸灯的设计是基于单片机的,还有一部分设计是基于FPGA的,我也一时手痒,将这两天自己重新写的verilog描述语句晒出来,免得压箱底放久了,出现发霉点。

为什么说重新写的呢,之前有老师教过,讲过呼吸灯,并且画出了 波形图和框图,这段时间,略有闲暇,就将之前学习的程序,重新再写一遍,看看自己是不是真的掌握了,还是说仅仅停留在 知道 这一层面上。

如果哪一天,我的大脑在看到某一课题项目时,能够立刻在脑海里构建出 框图,并且瞬时构思出 波形图,哈哈,那就真的达到了我内心期盼的高峰;

我目前参加的培训班在上海,报的是周末班课程,培训班的老师上课认真、细致的,而且还很热情,有什么问题能够快速给你解惑,我是我所最看重的。其他的培训班老师怎么样我不知道了,也无权置评;没有经历是没有发言权嘛!

二:呼吸灯简介

言归正传,咱们讲讲呼吸灯方面的知识;

呼吸灯最早是被苹果公司开发出来的,已经面世,立刻吸引众多科技公司效仿;

呼吸灯,顾名思义,就是模仿人的呼吸,由亮变暗===》再===》由暗变亮===》由亮变暗.......,如此循环往复。

三:呼吸灯思路分析

1:呼吸灯分为两个部分,一个部分是 由亮变暗,

一个部分是 由暗变亮,

2:当由亮变暗,也就是:

首先,占空比100%为零,

然后,占空比99%为零,1%为1;等于占空比100%

然后,占空比98%为零,2%为1;等于占空比100%

。。。。。。。。

。。。。。。。。

然后,占空比2%为零,98%为1;等于占空比100%

然后,占空比1%为零,99%为1;等于占空比100%

3:当由暗变亮,也就是:

首先,占空比100%为1,

然后,占空比99%为1,1%为零;等于占空比100%

然后,占空比98%为1,2%为零;等于占空比100%

。。。。。。。。

。。。。。。。。

然后,占空比2%为1,98%为零;等于占空比100%

然后,占空比1%为1,99%为零;等于占空比100%

四:呼吸灯功能定义

01)定义:一个完整的呼吸灯时间为2s,也就是,由亮变暗需要1s,由暗变亮需要1s;

02)将 1s分为1000等份,也就是 由亮变暗,需要1000次的变化,每次为1ms

03)将1ms分为1000等份,占空比100%过渡到0%,需要1000次的变化,每次为1us;

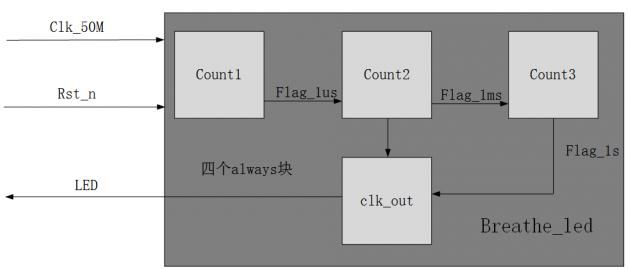

五:功能框图

( 借鉴雾盈网友的图,我们的方法是相同的 ,都是一个老师教授的,估计是我之前几届的)

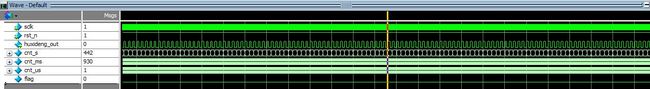

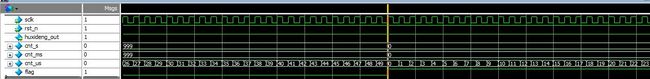

六:波形图

七:小结

呼吸灯是之前LED显示案例相关思路的一个汇总集成,属于一次升华;解题的思路很重要,思路清晰了,描述起来会如有神助,很快就能结束这个课题项目。

有的人觉得可能很简单,技术层面的事情如果捅破窗户纸,本就是很简单。夯实基础真的很重要,在基础厚实的过程中,你的感觉或者多次的锻炼形成的一直解题直觉会形成,这是极为重要的。

会者不难,难者不会;懂的人再接再厉,不懂的人埋头赶路,哪天抬头时,或许你会惊讶于自己已然成熟悟道。

八:推荐文章

01)雾盈FPGA笔记之(一):基于FPGA的呼吸灯简单实验程序

http://bbs.elecfans.com/jishu_922087_1_1.html

02)“流水灯”升级,基于FPGA的呼吸灯设计

http://dengkanwen.com/24.html

九:程序

//======================================//

//==Fosc : 50MHz

//==Timescale : 1ns/1ns

//==File name : huxideng.v

//==Date : 2016-09-27

//==Author : CY

//==Function : huxideng,由灭到亮再到灭....循环往复

//==Description:

//

//

//======================================//

module huxideng(

input wire sclk,

input wire rst_n,

output reg huxideng_out

);

//==================//

parameter T_s=10'd999; //1000

parameter T_ms=10'd999; //1000

parameter T_us=6'd49; //1us

// parameter T_2us=10'd999;

//==================//

// reg [25:0] cnt_2s;

// reg [15:0] cnt_2ms;

// reg [6:0] cnt_2us;

/*w我想的是错的,我一直囿于以前的印象,cnt_2s, 需要吗?

你是不是用不到,只是将2是分为100份,你写的是啥?需要自己的想法*/

reg [9:0] cnt_s;

reg [9:0] cnt_ms;

reg [5:0] cnt_us;

// reg [5:0] cnt_sclk;

reg flag;

//======cnt_1us======//

always@(posedge sclk or negedge rst_n)

if(!rst_n)

cnt_us <=6'd0;

else if(cnt_us==T_us)

cnt_us <=6'd0;

else

cnt_us <= cnt_us+1'b1;

//=====cnt_1ms========//

always@(posedge sclk or negedge rst_n)

if(!rst_n)

cnt_ms <=10'd0;

else if(cnt_us==T_us&&cnt_ms==T_ms)

cnt_ms <=10'd0;

else if(cnt_us==T_us)

cnt_ms <= cnt_ms+1'b1;

//=====cnt_1s=========//

always@(posedge sclk or negedge rst_n)

if(!rst_n)

cnt_s <=10'd0;

else if(cnt_s==T_s&&cnt_ms==T_ms&&cnt_us==T_us)

cnt_s <=10'd0;

else if(cnt_ms==T_ms&&cnt_us==T_us)

cnt_s <= cnt_s+1'b1;

//======flag========//

always@(posedge sclk or negedge rst_n)

if(!rst_n)

flag <=1'b0;

else if(cnt_s==T_s&&cnt_ms==T_ms&&cnt_us==T_us)

flag <= ~flag;

else

flag <= flag;

//=====control=======//

always@(posedge sclk or negedge rst_n)

if(!rst_n)

huxideng_out <=1'b1;

else if(cnt_scnt_ms&&flag==1'b1)

huxideng_out <=1'b0;

else

huxideng_out <=1'b1;

endmodule

cnt_ms&&flag==1'b1)

huxideng_out <=1'b0;

else

huxideng_out <=1'b1;

endmodule