基于FPGA的关于flash一些学习记录

基于FPGA的关于flash一些学习记录

使用 winbond 公司的 128Mbit Qual SPI 接口的 FLASH,芯号为 W25Q128BV, 支持 SPI, Dual SPI 和 Quad SPI 接口方式。在 Fast Read 模式,接口的时钟速率最大可以达到 104Mhz。FLASH 的容量由 65,536 个 256-byte 的 Page 组成。W25Q128 的擦除方法有三种,一种为 Sector 擦除(16 个 page,共 4KB),一种为 Block 擦除(128 个 page,共 32KB), 另一种为 Chip 擦除(整个擦除)。

△flash 编程芯片手册解析

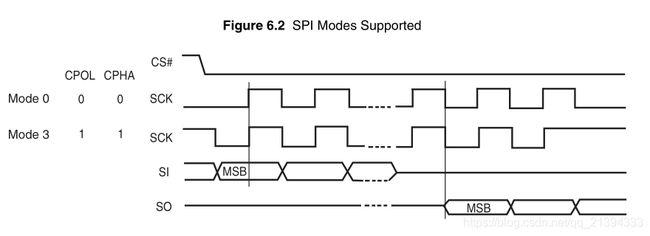

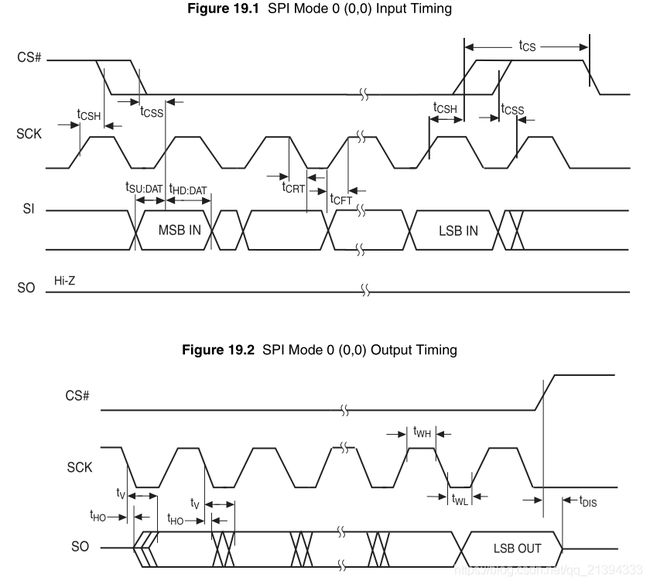

SCK上升沿输入数据,下降沿输出数据。8bit方式。

SPI数据读取方式: (READ: 03h)

RDID:读身份信息 (RDID: 9Fh)

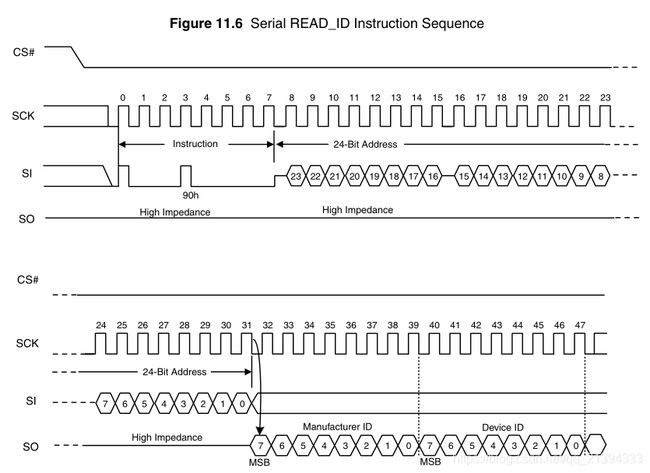

读设备ID: (READ_ID: 90h)

写命令使能: (WREN: 06h) (WRDI: 04h)

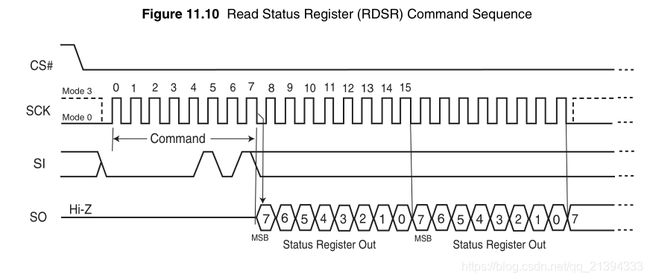

读取状态寄存器:(RDSR: 05h)

写状态寄存器:(WRSR: 01h)

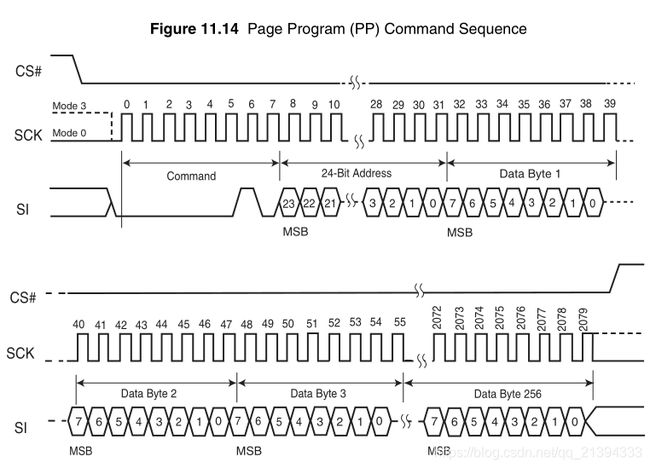

对整页进行数据编程:Page Program (PP: 02h)

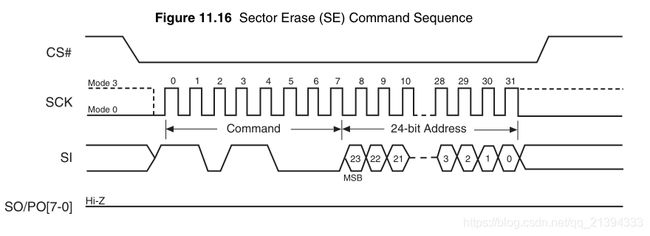

扇区擦除:(SE: 20h, D8h)

块擦除: (BE: C7h, 60h)

命令汇总:

02H是带地址的命令,所以是可以跟随地址写数据的,只是写数据范围只在当前页里而已。

读状态寄存器:Read Status Register (RDSR: 05h)

模式0的读写时序:

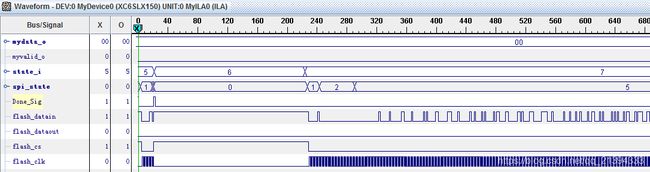

△测试结果

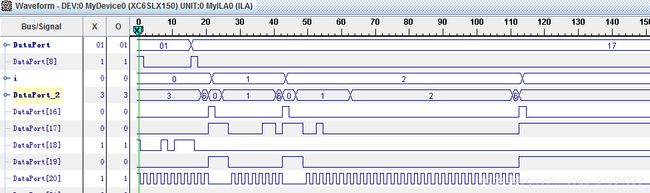

ID读取正常。

数据读写测试正常。

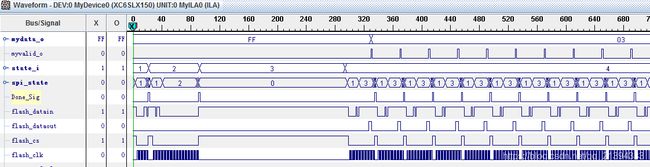

△实测:

1,首先进行擦除

2,写入数据

3,读取数据成功

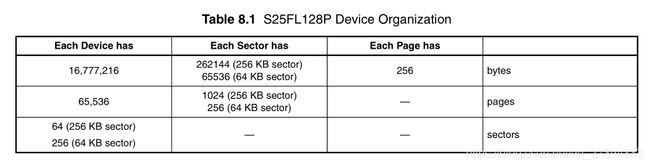

△flash的内存梳理

用的是256KB的。

1,每个设备有64个扇区,2,每个扇区有1024个页,3,每个页有256字节。

对应的地址位置:

设计思路:先只用一个扇区,后面再实现更多的。即地址只有:000000-03ffffh,有1024页,最多存下262143字节(=256*1024)的数据。262144/9=29127次!

如果只用一页的话,只有256字节,可存28次。

但要加末尾地址,不然断电后,不知道写到哪儿了,所以是一次写入12字节,256/12=21次。

△说明:

顶层向该层(Flash_top)提供命令数据(共9字节),起始存储信号(start_pp),读取flash数据信号(GetAllData)。

此模块的功能要求是:

①在检测到start_pp信号后,将9字节命令数据依次存入flash;每接收完STM32数据一次,就会有一个start_pp信号高电平脉冲。

②在接收到GetAllData信号后,将前面存储在flash中的数据,全部读出;数据输出接口拟为:output [7:0] Flash_Data。

附言:若要等到全部存完才可读取flash数据,在上位机视角,不知道该何时才能读取数据。所以还需实现功能②的要求。

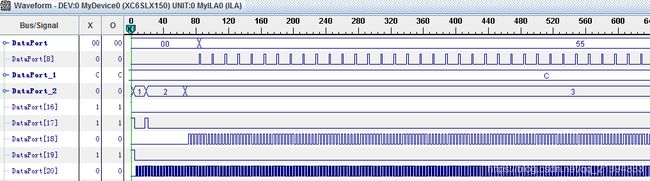

△程序完善:

1,只写入temp=55是可以的。

2,变化的数写入与读取成功。

简单地梳理了下flash的使用,只做到初步的数据读写,后面要用起来,还要更多的研究和测试。