什么信号需要绕等长?(网口信号,PCIE信号,DDR信号,LVDS信号)

来自专治PCB疑难杂症总群(添加杨医生微信号:johnnyyang206可入群讨论)微友的疑难杂症:关于PCB设计时,如何确定信号bus是否需要等长处理?另外Tr,Td对于等长有什么影响?

袁医生从骨髓里来分析下到底你说的这组不知道什么bus的bus需不需要绕长。从以下三个方面分析:1,为什么要绕等长?2,常见的哪些信号需要绕等长?3。如何预估等长要求的长度?

首先我们来了解下绕等长的目的。

等长线是为了减少信号相对延时;由于信号在PCB走线上存在延时,正比于信号线的长度。假设PCB上有两个完全相同的信号,但是布线长度不同。那么发端完全相同的信号在接收端就会由于延时的差异造成两个信号相位的不同。不相关的信号布线差异都不会引起问题。但是如果两根信号有时序要求,那么信号延时就可能造成信号错误。所以有时序要求的信号就会有等长要求。

等长的核心目的其实是为了系统的等时。最终我们研究的目的就到了时序上。简而言之,绕等长是为了满足时序要求。

为了了解时序,我们需要了解下信号得传输方式,一般可以分为以下几类:

1. 异步方式;信号靠握手传输。

2. 外时钟同步方式;两块芯片均使用外部时钟。

3. 内时钟同步方式;两块通讯芯片中,一块芯片给另一块芯片提供时钟。

4. 源同步方式;时钟、数据输出时固定相位同时传输。

5. 时钟数据恢复方式;从信号中同时提取数据与时钟。

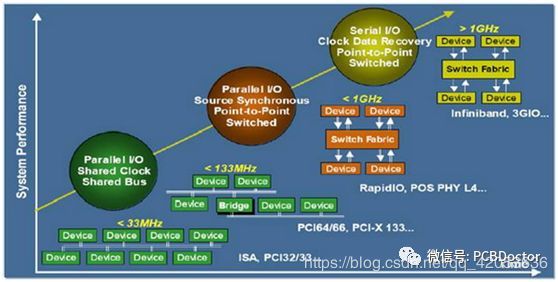

而涉及到谈论时序分析的一般就是:共同时钟时序,源同步时钟时序,串行信号时序。如下图关于信号传输的一个发展。

因为共同时钟的信号速率一般都较低,(通常适用于中等速度的总线设计,比如200MHz~300MHz 以下的频率),对时序的要求一般不严苛,我们更多的不是去关注他的等长,而是注意走线的长度不要太长。我们重点对等长有要求的是源同步时钟和串行信号。

随着速率的升高,那么就要用到其他传输方式。比如源同步时钟。

源同步时钟:是一种时钟或选通信号和数据同时从驱动芯片产生并同步传输的一种技术,是指时钟选通信号CLK由驱动芯片伴随发送数据一起发送,它并不象公共时钟同步那样采用独立的时钟源。在源同步数据收发中,数据首先发向接收端,经稍短时间选通时钟再发向接收端用于采样锁存这批数据。

一听到时序这个词,对于PCB设计者来说绝对是晕的,Tco,缓冲延时,传播延迟,最大/小飞行时间,建立时间,保持时间,建立时间裕量,保持时间裕量,时钟抖动,时钟偏斜等等,任何一个概念都对PCB设计者都是一个莫大的挑战。

其实从设计的角度根本不用知道那么详细,只要明白真正的原理就是:数据从驱动端发出,到达接收端有足够的建立时间;第二个数据来到之前,前一个数据要有足够的保持时间;

我们来举个例子:

首先我们来了解一个词:裕量,简单点说就是设计满足要求之外多出的那一部分。时序逻辑信号要满足建立时间和保持时间并有一定的裕量。只要满足这个条件,信号其实是可以不严格等长的。然而,实际情况是,对于高速信号来说(例如DDR2、DDR3、DDR4),在设计的时候是无法知道时序是否满足建立时间和保持时间要求(影响因素太多,包括芯片内部走线和容性负载造成的延时差别都要考虑,很难通过计算估算出实际值),必须在芯片内部设置可控延时器件(通过寄存器控制延时),然后扫描寄存器的值来尝试各种延时,并通过观察信号(直接看波形,测量建立保持时间)来确定延时的值使其满足建立时间和保持时间要求。不过同一类信号一般只对其中一根或几根信号线来做这种观察,为了使所有信号都满足时序要求,只好规定同一类信号走线全部严格等长。

以上我们分析了绕等长的目的以及一些哪些信号传输类型需要考虑时序接下来我们就直接过度到常见的哪些信号需要绕等长?即之前疑难杂症的问题:如何确定bus是否需要等长处理?

第一步,首先确定信号的传输方式:

1,如果是100M以上的共同时钟总线,可以做下时序分析,做等长处理,注意绕线长度。

2,如果是源同步时钟总线,按前面的分析,严格做等长,满足时序处理。

3,高速串行总线,时钟内嵌,差分传输,更多的是做对内等长处理。

第二步:知道那些常见的信号需要做等长。

DDR信号是典型的源同步时钟

LVDS需要满足时序要求,一般基于ADC的LVDS信号的接收通常采用源同步接收再加时序约束来保证接收的过程满足接收数据的建立时间和保持时间。

我们常说的百兆网口或者千兆网口速率都等于或者超过100兆,所以网口

PHY信号也需要满足时序做等长处理。变压器前端的差分信号做差分对内等长处理,PHY芯片以后的RMII信号以时钟为参考做BUS等长处理。

高速串行信号做对内等长;如SATA信号,PCIE等,高速串行总线采用的是时钟和数据恢复技术,这样就解决了限制数据传输速率的信号时钟偏移问题,同时也减少了布线冲突、降低了开关噪声等。所以差分对与差分对之间基本没有等长要求;时钟是依赖串行解串的技术进行传输与恢复。

其他信号根据第一步来判定是否需要等长处理。

最后我们谈谈等长约束的范围。

对于轻度熟悉信号完整性的,关于等长约束范围一般两种办法:其一,一般datasheet或者客户设计要求会告知等长约束要求;其二,根据经验值来知道等长约束范围。

当然深度知道怎么计算等长约束范围的信号完整性及PCB设计工程师就不一样了。

比如有一组BUS总共24根线,查数据得到信号的建立时间和保持时间都是1ns,最长的线和最短的线的信号传输差大于8ns才会影响信号,按照按照pcb上走线1000mil延时180ps计算,一个10inch的板子走线差就按10inch计算也才1.8ns,那么1ns的话是需要5.5*1000mil为 5500mil。

经常看到的还有内存颗粒的等长要求。有些约束说DDR2的等长要求数据线时钟线等长控制在正负50mil,地址线等长控制在正负100mil等等。实际画图的时候可能一个小的弯角就能差出几十个mil。其实这些约束条件比较苛刻,是为了满足绝大部分应用的需要。在我们每一个具体设计当中,可以根据芯片具体要求和运行速率的不同放宽约束条件,同样能满足要求,降低PCB设计复杂度。只要清楚PCB板上走线延时,表层走线大约140ps/inch,内层走线大约166ps/inch,再根据芯片运行速度和信号上升时间保持时间,推算出具体等长要求就可以了。

另外关于另外Tr,Td对于等长有什么影响?

其实信号上升时间以及时延对绕等长没有直接影响,只不过信号速率高,时序窗口会窄,等长会更严格。结合上面的文章分析即可更好的理解。

关注微信公众号:专治pcb疑难杂症 (PCBDoctor) 解决遇到的各种PCB疑难杂症。

袁医生简介

资深信号完整性工程师。专业从事信号以及电源完整性分析八年。擅长业界常见的高速接口总线的信号完整分析,如PCIe,SATA,USB3.0,10g光模块等,尤其擅长DDR模块的信号以及电源完整性分析。精通业界常用仿真软件,如Cadence,sigrity,ADS,HFSS,ANSYS。多次主持公司团队超高速PCB布线预研工作,熟悉业界常用的高速板材。运用仿真技术解决高速PCB设计中遇到的阻抗失配,串绕,损耗,时序等问题。精通电源完整性分析,运用仿真手段解决供电网络的AC噪声以及大电流网络的IRdrop问题。SI/PI设计,我们是专业的!

袁医生医道:以此为生,精于此道!