DDS正弦信号发生器

虽然临近考试,还是偷着时间把DDS的初级操作给搞定了,O(∩_∩)O哈哈哈。从搞清理论原理,到下载调试出波形,还真费了点功夫。

这也算从VHDL转战verilog的第一仗吧,把模块化设计小过了把瘾,嘿嘿……

不管这能不能算个项目,但我还是在短时间内弄出来了,至于细节问题还有功能加强,考试之后再说喽!

首先还是要理清DDS中的理论计算关系,好的设计总是靠些理论的,呵呵。以输出信号为正弦信号为例好啦,主要关系和公式如下。

为把t数字化(量化),选取基准时钟(系统时钟)![]() 和基准相位(把2

和基准相位(把2![]() 分成2N等份)

分成2N等份)![]() ,从而使得每个相位都有一个量化值,基准相位就是相位量化的精度。

,从而使得每个相位都有一个量化值,基准相位就是相位量化的精度。

在基准时钟的一个周期内,输出信号相位增量为:

所以,就可以变换得到输出频率:![]() ,可知,

,可知,![]() 和

和![]() 是线性关系,

是线性关系,![]() 所起到的作用就是对基准时钟

所起到的作用就是对基准时钟![]() 进行分频得到输出时钟,且有:

进行分频得到输出时钟,且有:

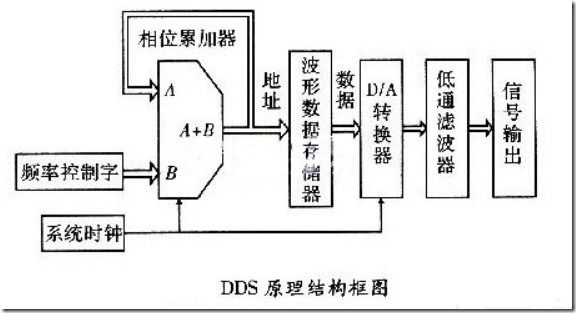

DDS的基本工作流程就是通过相位的累加,得到当前的相位值,然后用当前的相位值(转换为ROM地址)进行查表,得到相应的幅值,然后输出。

DDS主要由相位累加器、相位调制器、ROM查找表和DAC。其中,相位调制器用于信号的相位调制,设计波形发生器时可以不用。

由于没有示波器,所以DAC部分也不设计,采用SignalTap II 观察。(示波器?YY下吧!)

DDS的基本原理框图如下;

ROM中的数据量由DAC位数决定,假设精度为10位,则ROM中需要存放一个周期![]() 的1024个点的数据,而每个点的数据大小由此点的幅度值

的1024个点的数据,而每个点的数据大小由此点的幅度值![]() 确定。

确定。

对ROM的读取时钟频率就是![]() 。当然ROM的数据要由C或MATLAB得到啦,手动输入的话早就吐血了。

。当然ROM的数据要由C或MATLAB得到啦,手动输入的话早就吐血了。

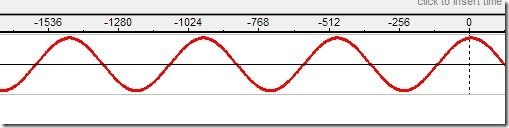

这次实验,采用的基准时钟是50MHZ,所取输出时钟是1KHZ。SignalTapII所得波形如下,这波形还算过得去啊:

程序部分倒是没有遇到什么问题,可是一开始居然挂在mif文件上,幸好在群里头遇到高人,用MATLAB重新弄了个,终于得到正确结果!

离场悲剧对DDS工作原理的解释可谓一针见血: