CDC:跨时钟域处理

前言(还未整理好)

CDC(clock domain crossing)检查(跨时钟域的检查)是对电路设计中同步电路设计的检查。非同步时钟没有固定的相位关系,这样Setup/Hold不满足而产生了亚稳态是无法避免的。我们采用同步设计的方法保证亚稳态不会无序的在电路中传播,从而导致功能问题。

随着当今SOC设计的规模越来越大,时钟越来越多,工作模式越来越复杂。跨时钟域电路不但多,而且非常复杂。 在当今的电路设计中我们通常使用多级同步,异步FIFO,握手等同步设计来保证亚稳态信号不会在电路中无序的传播。

但同步设计中,同步处理不当依然会出现glitch,多路扇出等问题导致电路实际运行出现故障。

目前我们的数字设计大部分是基于RTL设计的,直接通过RTL检查"跨时钟域的同步设计" 很难做到100%覆盖的检查,特别是当今SOC中集成大量IP,直接通过RTL检查几乎不可能的。 电路设计中同步电路设计的检查都是使用专门的EDA工具做静态的CDC检查。常用的CDC检查工具有Conformal CDC 和 Spyglass CDC。

此外CDC检查也是前端sign off 重要项目和数字IC设计工程师的必备的技能。

第一讲 时钟域

1.1 什么是时钟

· 时钟信号是一个按一定电压幅值、一定时间间隔连续发出的脉冲信号。

- 脉冲信号之间的时间间隔称为周期;

- 将单位时间(如1秒)内所产生的脉冲个数称为频率。

· 每一次脉沖到来,芯片内的晶体管就改变一次状态,让整个芯片完成一定任务

时钟偏斜(clock skew)

时钟偏斜,指的是同一个时钟信号到达两个不同寄存器之间的时间差值,Skew的定义就是时钟最长路径减去最短路径的值。

时钟抖动(jitter)

时钟抖动,指的是两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者PLL内部电路有关。

1.2 什么是时钟源

数字电路里一般用晶振提供基本的时钟信号。晶振是晶体振淓器( Quartz Crystal OSC)的简称。

・有些芯片的一部分时钟来自于其他芯片。它的时钟源就是外部芯片的输出信号。比如芯片12C、SPI接口时钟就来自外部芯片。

1.3 同步时钟

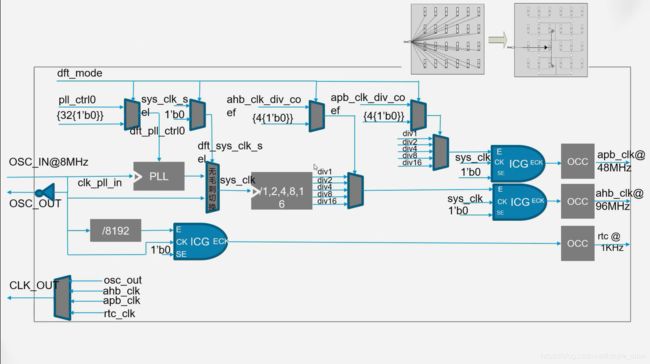

ASIC中的时钟结构

FPGA中的时钟结构

-

MMCM( Mixed- Mode Clock Manager)混合模式时钟管理器

-

High-performance Clock

-

BUFG(全局时钟缓冲器)

-

BUFH( horizontal clock buffers横向BANK时钟绶冲器)

-

BUFR(用于纵向BANK时钟缓冲器)

-

BUFMR (multi-clock region buffers)

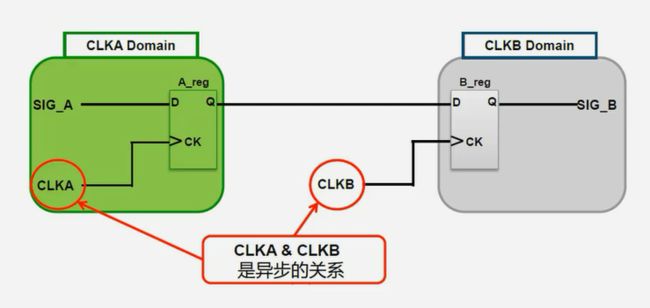

1.4 异步时钟

- 不同源

- 没有固定的相位关系

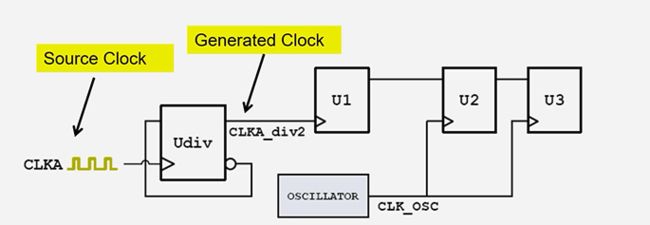

下图中,CLKA和CLK_OSC就是异步时钟。

问题:有两个不同频率的时钟A和B。A:clk0 为100MHz,B:clk1为99MHz。他们两个是不是异步时钟?

不一定!

问题:有两个相同频率的时钟A和B,他们无固定相位,他们两个是不是同步时钟?

不是同步时钟!

1.5 什么是时钟域

时钟域(Clock Domain)是以捕获时钟划分时钟域

单时钟(Single clock domain):数据发送和接收是一个时钟

多时钟(Multiple clock domain):数据发送和接收不是一个时钟

1.6 跨时钟域问题

跨时钟域

- 若一个电路 launch时钟和 capture时钟不是同一个时钟,就是跨时钟电路

- 若两个时钟是同步时钟就是同步时钟域

- 若两个时钟是异步时钟就是异步时钟

- 跨时钟域的例子

- 单个模块:switches, UART receivers, USB-FPGA interfacing

- 整个系统:Different clock in a large design, e.g., Socs

跨时钟域问题

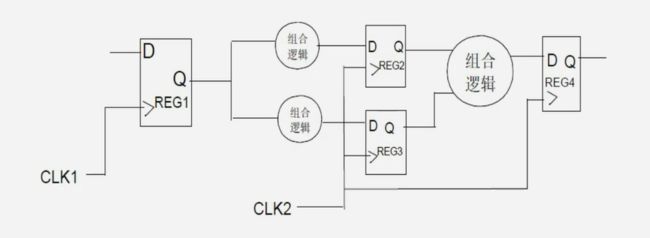

CLK1与CLK2来自不同的时钟源。

由于时钟源不同,对REG2和REG3来讲,在同一时刻,一个认为REG1的输出是1,另一个认为是0,这必定造成电路判断出现错误。

第二讲 亚稳态

2.1 建立时间和保持时间

-

建立时间t(su)(setup time)

-

对任何一种触发器,在时钟触发沿前后的一个小时向窗口内,输入信号必须稳定。

-

触发器的时钟信号上升沿到来以前,数据稳定不变的时间。输入信号应提前时钟上升沿(假设上升沿有效)T时间到达芯片,这个T就是建立时间 Setup time。如不满足setup time,这个正确的数据(或稳定后的数据)就不能被这一时刻时钟打入触发器

-

保持时间t(H)(hold time)

-

保持时间是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间。如果 hold time不够,数据同样不能被正确打入触发

2.2 什么是亚稳态

亚稳态

触发器无法在某个规定时间段内达到一个可确认的状态。亚稳态会带来功能的错误

亚稳态时

既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。触发器输岀一些中间级电平,或者可能处于振荡状态。

亚稳态传播

这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去

2.3 如何处理亚稳态

- ①降低系统时钟

- ②用反应更快的FF

- ③引入同步机制,防止亚稳态传播

- ④改善时钟质量,用边沿变化快速的时钟信号

2.4 二级寄存器

使用同步器降低亚稳态发生的概率:

1.亚稳态需要一段时间才能到达稳态

2.二级寄存器可以增加一个 clock cycle的时间使亚稳态稳定

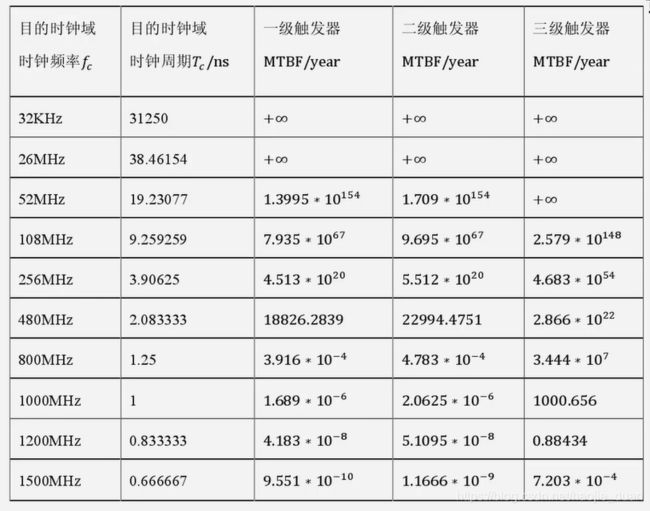

2.5 MTBF

平均故障间隔时间MTBF (Mean Time Between Failure )

使用同步器降低亚稳态发生的概率

两级并不能完全隔离亚稳态危害,但极大的概率隔离了亚稳态发生概率。

第三讲 跨时钟域设计——单比特信号的跨时钟域处理

3.1 慢时钟域信号同步到快时钟域的处理方法

两级触发器同步

慢时钟信号进入到更快的时钟域时(频率相差2倍以上),此时不用考虑快时钟域信号采样的丢失,可以考虑使用两级触发器进行同步处理

边沿检测同步器

慢时钟信号进入到更快的时钟域时(频率相差2倍以上),为了避免快时钟多次采样到有效信号,快时钟域需要对信号进行边沿检测。需要使用边沿检测同步器

握手处理

当一个慢时钟域的单比特信号进入到更快的时钟域,但是两个时钟频率相差不大(频率相差2倍下),为了避免快时钟采样丢失,需要进行握手的同步处理

3.2 信号上升沿检测

快时钟先将输入信号进行两级同步处理,再进行一个时钟的延迟,延迟后的信号取反与同步信号做与逻辑,得到信号的上升沿

3.3 信号下降沿检测

快时钟先将输入信号进行两级同步处理,再进行一个时钟的延迟,延迟后的信号与取反同步信号后做与逻辑,得到脉冲信号的下降沿

3.4 双沿检测器

快时钟先将输入信号进行两级同步处理,再进行一个时钟的延退,延迟后的信号与同步信号做异或逻辑,就可得到信号的双沿脉冲。

3.5 快时钟域信号同步到慢时钟域的处理方法

电平拓展

如果已知慢时钟域的时钟频率,可以考虑将快时钟域的信号进行电平扩展,使其足以被慢时钟域采样。

脉冲同步器

快时钟域中需要同步的信号是脉冲信号,它触发原时钟域的反转电路,每当翻转电路收到脉冲时,电路翻转一次慢时钟域的同步器对翻转后的信号进行采样,和边沿检测,重新在本时钟域恢复出脉冲信号

握手处理

当一个快时钟域的单比特信号进入到慢的时钟域,同样可以使用握手的方式进行同步处理

3.6 脉冲同步器(快时钟域到慢时钟域)

脉冲同步器的使用中,快时钟域的有效信号需要时单脉冲信号,且两个有效信号的时间间隔需要大于等于两个同步器的时钟周期,否则无法恢复出有效信号

3.7 典型电路案例分析(此处再看)

对跨时钟域的 Timing path如果不处理容易导致亚稳态。如果做了同步处理,但同步处理不当俨然会出现 glitch,多路扇出,Re-convergence,Datahold等问题导致电路实际运行出现故障

CLKA domain中,DA1和DA2分别为两个DFF的输出,理想状态下,DA1和DA2到达与门两个输入端的时间是一样的,这样设计就不会出问题。但由于后端布局,环境等因素导致的传播延迟Td会使A&B存在一个 Glitch。而由于CLKB和CLKA为两个 clock domain,之间不存在固定的相位关系,假设这个 Glitch恰好被CLKB锁存住,那么就会在DB2生成一个有效的高电平信号,这个高电平信号不是我们的设计所期望的,那就会导致后继的电路功能出现问题。

错误解决方案

跨时钟域的多个相关连的单比特信号不可以通过打拍的方式同步到目的时钟域

第四讲 跨时钟域设计——多比特信号的跨时钟域处理

4.1 两级触发器的问题

两级触发器用来处理多比特信号的同步的问题

- 如果简单的按照单比特信号穿越方法各bit打两拍单独穿越,则会造成各个bit穿越时间不一致(寄存器

对于每个信号的延迟时间不ー样),则会造成另一个时钟域里面有一些被前一个时钟沿采到了,有些

被后面的采到了,导致目的时钟域采到的值错误,造成中间态无意义的数据。

两级触发器同步多比特信号的解决方法

如果多比特信号之间存在逻辑相关性。可以在源时钟域将信号合成一个单一的控制信号然后进行两级寄存器同步

4.2 多比特信号跨时钟域的处理方法

格需码编码

通过编码的方式将多位信号转化为每次只有一位变化的信号,将“多比特”的跨时钟域变换成“单比特”进行处理。

异步FFO

异步FIFO融合了寄存器同步,格雷码编码,握手控制等处理方式,是处理跨时钟域数据传输最常用的方式。

握手处理

所谓握手,是指通信双方使用了专用控制信号进行数据收发的状态指示。这个控制信号既有发送域给接收域的,也有接收域给发送域的,有别于前面的单向控制信号检测方式。类似于DMA与外设模块的通信,会用到dma_req,dma_ack

4.3 格雷码编码处理跨时钟域

什么是格雷码

格码编码的跨时钟域处理

格雷码的特点是相邻的两个编码之间只有1位不同,消除了在同一个时钟沿,多比特信号或者数据同时变化所带来的跨时钟域问题

应用局限:只有在数据在相数值间连续变化的情况下才有用,不适用于大多数信号传输或者数据传输的情况。

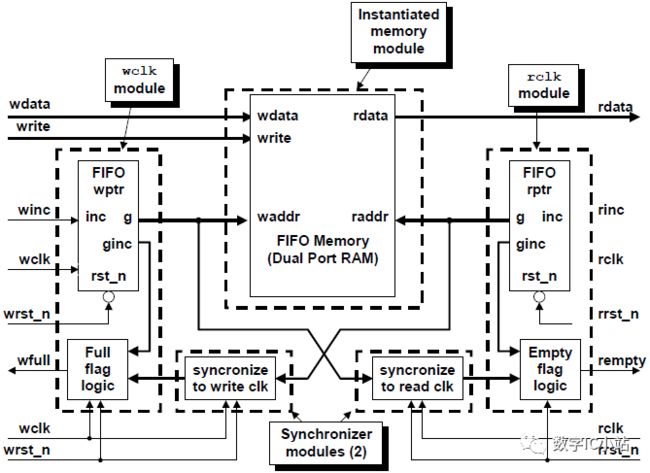

4.4 异步FIFO

异步FIFO的特点

- 异步FIFO的特点是拥有两个相互独立的读写时钟,允许两个独立时钟的频率有较大的差距

- 跨时钟域的读写地址传输采用格雷码编码,然后加上两级寄存器同步的方式。

- “满”逻辑用来控制写信号,将读时钟域的读指针同步到写时钟域,在写时钟域进行比较。

- “空”逻辑用来控制读信号,将写时钟域的写指针同步到读时钟域,在读时钟域进行比较。

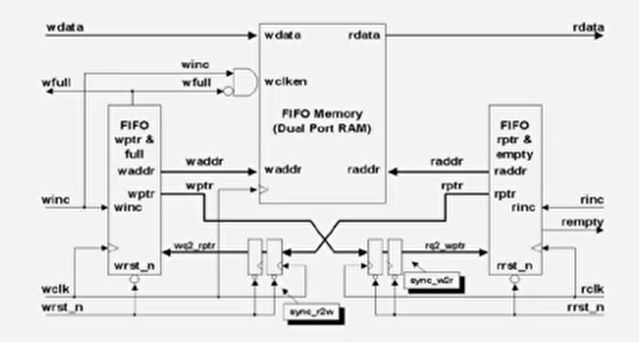

异步FIFO的结构

- 写控制逻:控割写操作与满信号(wfuI)的判断与产生。

- 读控制逻辑:控割读操作与空信号(empy)的判断与产生

- RAM:双端口RAM

- 二进制码与格雷码转换模块:用于将读写地址二进剖码转成格番码。

- 跨时钟同步模块:将读地址的格雷码与wclk同步;将写地址的格雷码与rclk同步。主要操作就是两级寄存器同步

4.5 多比特跨时钟域的握手处理

握手方式的原理

- 握手方式处理跨时钟域数据传输,需要对双方的握手信号(req和ack)分别使用脉冲检测方法进行同步。

- 在具体实现中,发送域先把数据放入总线,随后发送有效的req信号给接收域。接收域在检测到有效的req信号后锁存数据总线,然后回送一个有效的ack信号表示读取完成应笞。发送域在检测到有效ack信号后撤销当前的req信号,接收域在检测到req撤后也相应撤销ack信号,此时完成一次正常握手通信。

- 握手方式是一种稳定可靠的同步处理方式,但控制信号握手检测会消耗通信双方较多的时间。

第五讲 跨时钟域设计——握手处理

5.1 握手的原理

握手,即通信双方使用约定的控制信号进行数据传输的状态指示。这个控制信号既有发送域给接收域的,也有接收域给发送域的。

5.2 什么时候使用握手同步处理

- 通信过程需要保障数据的稳定可靠,并能允许通信过程消耗双方较多的时间

- 当通信双方不能预知相互的响应时间时,握手能让两个时钟域间实现有效的通信

- 方式一般使用在总线数据的传输上

5.3 握手电路的实现

第六讲 跨时钟域设计——异步FIFO

6.1 异步FIFO的应用

异步FIFO的作用

解决两个不同时钟域之间批量数据的高效传递。

异步FIFO的应用

数据速率的转换,比如突发速率转换为线性均匀速率( burst write and single read).

不同时钟域数据快速传输与緩存。

不同数据位宽的数据接口的匹配。

6.2 异步FFO的结构

异步FIFO的一般结构

- 双端口RAM:用于存储效据。

- 读控制逻辑:控制读操作与空信号( empty)的判断与产生,属于读时钟域。

- 写控制逻辑:控制写操作与满信号(wfull)的判断与产生,属于写时钟域。

- 二进制码与格雷码转换模块:用于将读写地址二进制码转成格雷码。

- 跨时钟同步模块:将读地址的格雷码与wclk同步;将写地址的格雷码与rclk同步。

异步FIFO处理的核心问题

- FIFO深度的计算。

- 读写地址的编码

- 控制信号、读写地址的跨时钟域同步

- 读写控制信号的产生。

经典异步FIFO的结构一

将读时钟域的读地址(经格雷码转换后),再同步到写时钟域,进行逻辑比较

将写时钟域的写地址(经格雷码转换后),再同步到读时钟域,进行逻辑比较

经典异步FFO的结构二

将读写地址(经格雷码转换后)同步到一个组合逻辑电路中(异步比较)直接比较空满,然后将空满信号同步到各自对应的模块中。

6.3 异步FIFO深度的计算

异步FIFO深度的计算

- 计算异步FIFO的深度,需要综合考虑读、写的时钟频率,读、写数据的位宽,读、写的频率等。

- 写快读慢的情况下,突发 burst写入的数据减去该 burst时间内读出的数据,多余的数据需要能缓冲下来,让接收端在剩下空闲的时间能从容地把多余的数据读出来。

- 读快写慢的情况下,FIFO的深度最小可以设置为1.

异步FIFO深度的计算示例1

-

FIFO读、写位宽都为8,写时钟 wclk为100MHz,读时钟rclk为95MHz,写入数据的总长为4Kbit,且两次写操作之间的时间间隔足够大。每一个rclk读取一个数据。求FIFO的深度。

-

写入的突发长度: burst_length=4K/8=500字节(即T时间内写入了500字节的数据)

-

要保证FIFO不溢出,那么在T时间内,500字节数据要被全部读出。T=500/100MHz.

-

T时间段读取的数据量为:T95MHz=475字节,FIFO的深度至少要大于等于25

-

公式总结:fifo_depth= burst_ length-( burst_ length /w_clk)r_cIkX/Y

-

这里X、Y代表的意思:每Y个rclk会有X个数据读出FIFO

异步FIFO深度的计算示例2

-

FIFO读、写位宽都为8,写时钟wclk为80MHz,读时钟rclk为40MHz,写入数据的总长为120byte,每2个写时钟写入一个数据,每4个读时钟读取一个数据。求FIFO的深度。

-

写入的突发长度: burst length=120字节(即T时间内写入了120字节的数据)

-

等效的写时钟频率wclk=80/2=40M

-

等效的读时钟频率rclk=40/4=10M

-

要保证FIFO不溢出,那么在T时间内,120字节数据要被全部读出。T=120/40MHz

-

T时间段读取的数据量为:T*10MHz=30字节,FIFO的深度至少要大于等于90字节

6.4 异步FIFO读写地址的编码

异步FIFO读写地址的格雷码编码

- FIFO的读写地址都是连续的。采用格雷码编码,每次地址的变化,都只有1位数据跳变,有利于信号的跨时钟域同步。

二进制码转换成格雷码

转换规则:从最右边一位起(最低位开始),依次与前一位“异或",作为该位的输出,最高位不变

module BINARY_TO_GRAY(binarycode,graycode);

parameter n = 4;

input [n-1:0] binarycode;

output reg [n-1:0] graycode;

integer i;

always@(binarycode)begin

graycode[n-1] = binary[n-1];

for(i=0;i<n;i++)

graycode[i] = binarycode[i]^binarycode[i-1];

end

endmodule

格雷码转换成二进制码

转换规则:最高位不变,从最左边起将产生的每一位二进制码,与下一位相邻的格雷码"异或”,作为二进制码的下一位。

module GRAY_TO_BINARY(graycode,binarycode);

parameter n = 4;

input [n-1:0] graycode;

output reg [n-1:0] binarycode;

integer i;

always@(graycode)begin

binarycode[n-1] = graycode[n-1];

for(i=0;i<n;i++)

binarycode[i] = graycode[i]^graycode[i-1];

end

endmodule

6.5 异步FIFO读写时钟域的信号同步

异步FIFO的跨时钟域信号同步

- 满”信号控制写逻辑,在写时钟域产生。“满控制信号不需要同步到读时钟域。只需要将写地址进行跨时钟域的同步。

- “空信号控制读逻辑,在读时钟域产芏。“空”控制信号不需要同步到写时钟域。只需要将读地址进行跨时钟域的同步。

- 跨时钟域地址同步:将读地址的格雷码与wclk同步;将写地址的格雷码与rclk同步。主要操作就是两级寄存器同步。

为什么使用两级寄存器同步多比特位宽的地址信号?

- 异步FIFO读写地址都是连续变化的,在进行两级寄存器同步之前,进行格雷码编码,可以将多比特变化的信号变成每次只有单一比特変化的信号进行同步。

6.6 异步FFO满空信号的产生

异步FIFO空满信号的产生

- 读写控制信号判断与产生是通过对读写地址指针的比较判断出来的

- 二进制比较:因为跨时钟域同步后的地址是格雷码,需要在本时钟域对地址进行二进制转换

- 格雷码直接比较:省去了二进制的转换,直接将本时钟域的格雷码编码地址与同步过来的格雷码地址进行比较

传统二进制比较

当wren有效,写地址=读地址-1或者写地址=读地址+ FIFO_DEP,full为1.写指针超越读指针

当rden有效,读地址=写地址-1或者读地址=写地址+FIFO_DEP, empty为1;读指针超越写指针

格需码直接比较产生空满信号

- 假如FIFO的深度为8,我们用宽度为4的指针对FIFO进行寻址

- 如果读指针的最高位为0,而写指针的最高位为1,说明写指针超前于读指针,这时如果读写指针指向同一存储空间(次高位相异),则可判断为full

- 如果读指针的最高位为1,而写指针的最高位为0,说明写指针发生了回转,这时如果读写指针指向同一存储空间(次高位相异),则可判断为full

- 当读指针完全与写指针相同时,则判断为 empty

格码直接比较产生空满信号举例

- 假如FIFO的深度为8,我们用宽度为4的指针对FIFO进行寻址

- 起初初始化时。Wr_ptr_bin=“0000,rd_ptr_bin=0000、此时,FIFO空”

- 首先执行8次写操作。Wr_ptr_bin=1100,rd_ ptr bin=0000此时,FIFO满。

- 然后执行8次读操作。Wr_ptr_bin=“1100,rd_ptr_bin=21100.此时,FIFO空”。

- 最后执行8次写操作。Wr_ptr_bin=0000,rd_ptr_bin=1100,此时,FIFO满。

6.7 异步FIFO读写时钟快慢对信号同步的影响

读写指针的两级寄存器同步所带来的延迟,对空满信号的判断有影响吗

- 将写指针同步到读时钟域再和读指针比较进行FIFO空状态判断时,因为在同步写指针时需要时间,而在这个同步的时间内有可能还会写入新的数据,因此同步后的写指针一定是小于或者等于当前实际的写指针,所以此时如果FIFO为空”,则实际的写指针可能仍然大于读指针,FIFO并不是真的“空。这样可能会影响FIFO的性能,但是并不会出错。

- 将读指针同步到写时钟域再和写指针比较进行FIFO满状态判断,同步后的读指针一定是小于或者等于当前的读指针所以此时判断FIFO为满不一定是真满

- 总结来说异步逻辑转到同步逻辑不可避免需要额外的时钟开销,这会导致满空趋于保守,但是保守并不等于错误,这么写会稍微有性能损失,但是不会出错。

异步FFO读写时钟频率相差很大,对空满信号的判断有影响吗

- 假设异步fifo,写时钟500M,读时钟100M,相差5倍。

- 满信号的判断是在写时钟域,比较同步过来的读指针,由于写时钟500M大于读时钟100M,快时钟采样慢信号,满的判断不会有间题。

- 空”信号的判断是在读时钟域,比较同步过来的写指针,由于读时钟频率低,采样的写指针可能是离散值(3,6,9).但是采样到的写指针,必定小于写时钟域的写指针。所以判断出来的空”信号,是一个保守的“空”信号。在实际应用中没有问是题。

第七讲 跨时钟域设计——复位同步问题

7.1 同步复位和异步复位的特点

同步复位

- 复位信号只有在时钟上升沿到来时,オ能有效。复位时间需要大于系统周期,否则,无法完成对系统

的复位工作。 - 同步复位可以滤除高于时钟频率的毛刺。是完整的同步设计,有利于时序分析。

- 同步复位会耗费较多的逻辑资源,并会产生组合逻辑路径延时,复位延时等。

异步复位

- 只要综合工艺库有可异步复位的触发器,那么该触发器的数据输入通道就不需要额外的组合逻辑

- 无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。

- 异步复位设计简单,可以很方便的实现系统的全局复位。

7.2 异步复位的问题

异步复位的问题

- 最大的问题在于它属于异步逻辑,间题出现在复位释放时,如果复位释放接近时钟有效沿,则触发器

的输出可能进入亚稳态,从而使复位失败 - 可能因为噪声或者毛刺造成虚假复位信号

如何解决异步复位的问题

异步复位同步释放

7.3 异步复位同步释放

- 复位信号是异步有效的,即复位的发生与clk无关。后半句“同步释放”是指复位信号的撤除的时侯收到时钟信号的同步(同步释放)。

- rst_async_n异步复位后, rst_sync_n将拉低,即实现异步复位。当复位信号rst_async_n撤除时,由于双緩冲电路(两级蝕发器)的作用, rst_sync_n复位信号不会随着 rst_async_n的撤除而撤除。

第八讲 跨时钟域设计——跨时钟的代码检查

8.1 Spyglass功能

Spyglass

- Lint

在RTL阶段对代码的语法,可综合性,结构进行深入分析,并且对代码的错误提供完整、可调试的修改方案 - SDC

帮助设计人员在设计的整个流程中生成,验证和管理他们的约東文件。 - CDC

提供了业界最完整的多时钟域解决方案,能自动识别各种同步手段(包括 Handshake,FIFO),能采用 Formal引擎验证同步方法在功能上的正确性 - DFT

提供了能的骭测ATPG的测试覆盖率分析的能力,基于这个选项,用户可以很容易地预计所作设计的可测试性并且利用工具提供的指导来提高设计的可测试性。 - Power

能够让用户能够快速分析出设计中的功耗效率问题,从而在还没有达到后端工序的情况下快速地进行功耗的优化,用户甚至可以在不进行逻辑综合和物理实现的情况下对功耗进行量化的计算。

Spyglass优势

Spyglass的检查验证处在设计的前段RTL阶段,枏比较于后端的时序分析和网表验证, spyglass前能更早的发现问题并修正。

能够让用户能够快速分析出设计中的功耗效率问题,从而在还没有达到后端工序的情况下快速地进行功耗的优化,用户甚至可以在不进行逻辑综合和物理实现的情况下对功耗进行量化的计算。

Spyglass CDC的特点

Spyglass CDC检查可以发现仿真、FPGA测试中很难发现的潜在的跨时域处理问题。

可以检查出复位、时钟是否使用正确,对跨时域设计进行评估检查。

8.2 Spyglass CDC使用流程

Spyglass CDC使用方式

- TCL脚本的方式,TCL方便快捷省去了UI界面上的繁琐操作。

- 软件UI界面操作,跨时域设计一般设计到的层次较多,界面方式 debug较直观。

- 通常我们会用脚本启动 Spyglass,走流程,然后在UI界面里面 Debug

Spyglass CDC所需文件

- Filelist.f:用户RTL的文件列表。

- spyglass. sgc: spyglass用的sgdc约東文件。

- spyglass.tcl:如果是脚本方式启动需要准备tcl脚本文件,并在脚本中对CDC的Goal做声明。

Spyglass CDC界面方式

下面是界面方式的使用流程:

- 建立好文件夹,准备好们elst. spyglass. sgc文件。

- 打开 Terminal,输入命令: spyglass&。启动 spyglass。

- 点击 Add File(s),添加filelist和 spyglass.sgdc文件。并点击OK确认。

8.3 CDC rules check1

8.4 CDC rules check2

第九讲 跨时钟域设计——时钟域的综合处理

9.1时钟的定义

9.2.同步时钟的约束

9.3.异步时钟的约束

9.4.DC的综合处理

9.5. DC timing分析

9.6.FPGA的综合处理

后记

文章中未展开说明的部分,不是小编目前关注的点。供大家参考。