LVDS_FPGA

来源:http://bbs.ednchina.com/BLOG_ARTICLE_1988415.HTM

http://hi.baidu.com/shouzhishi/blog/item/8a348bfabbc05c284e4aead6.html

对于Xilinx芯片而言,LVDS与BANK的连接是有要求的。因为LVDS的输出只能布局在bank0或者bank2上,而LVDS的输入并没有这个要求。所以在看Spartan6板子上的布局时,发现CN3插槽有连接到bank0但主要还是连接到bank3上。而CN4全部连接到bank3所以只能作为LVDS的输入部分。而CN5全部连接到bank0上,所以即可以作为LVDS的输入也可以作为LVDS的输出。所以做这个插槽是最好的。发现洪鸿榕好聪明。这种都能发现。

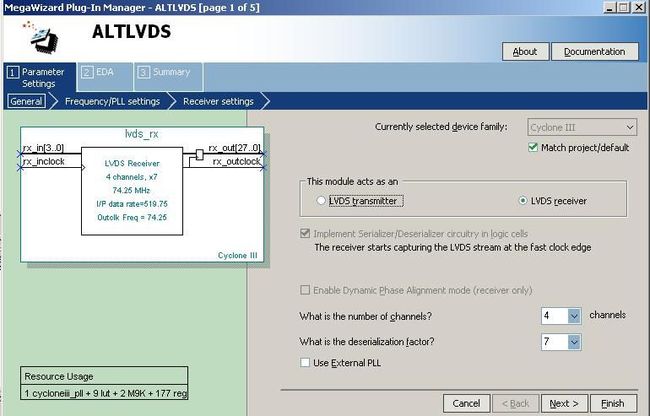

LVDS输入和输出在FPGA中都是有IP core的。以7bit,4+1,时钟74.25MHz为例。说明IP core的设置

首先,选择你所用的器件,我用的是Cyclone 3。 再选择LVDS receiver,

what is the number of channels ? 选择4...........表示4组数据;

what is the deserialiation factor ? 选择7...........表示每个CLK传7bit;

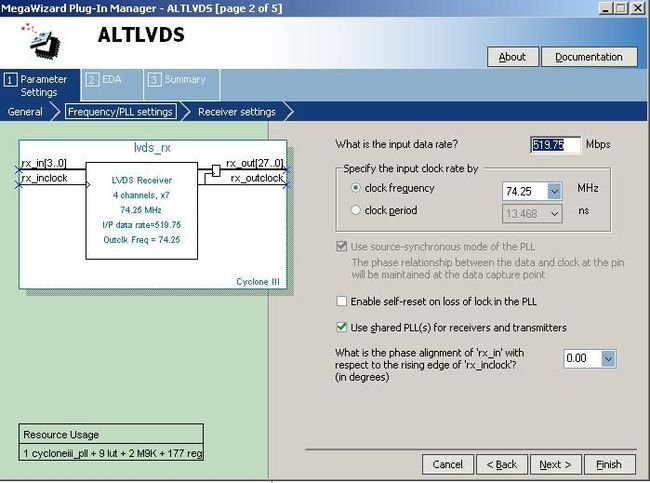

what is the input data rate? 填519.75.................即74.25*7

选择use shared PLL..........

what is the phase ............这个选项是选择数据线与时钟的相位差,因为LVDS的相位有差别,接收IP core能调整.

FPGA中IBUFDS、IBUFGDS&OBUFDS

与全局时钟资源相关的Xilinx器件原语包括:IBUFG、IBUFGDS、BUFG、BUFGP、BUFGCE、BUFGMUX、BUFGDLL和DCM等

全局时钟资源的使用方法 全局时钟资源的使用方法(五种)

1.IBUFG + BUFG的使用方法:

IBUFG后面连接BUFG的方法是最基本的全局时钟资源使用方法,由于IBUFG组合BUFG相当于BUFGP,所以在这种使用方法也称为BUFGP方法。

2. IBUFGDS + BUFG的使用方法:

当输入时钟信号为差分信号时,需要使用IBUFGDS代替IBUFG。

3. IBUFG + DCM + BUFG的使用方法:

这种使用方法最灵活,对全局时钟的控制更加有效。通过DCM模块不仅仅能对时钟进行同步、移相、分频和倍频等变换,而且可以使全局时钟的输出达到无抖动延迟。

4. Logic + BUFG的使用方法:

BUFG不但可以驱动IBUFG的输出,还可以驱动其它普通信号的输出。当某个信号(时钟、使能、快速路径)的扇出非常大,并且要求抖动延迟最小时,可以使用BUFG驱动该信号,使该信号利用全局时钟资源。但需要注意的是,普通IO的输入或普通片内信号进入全局时钟布线层需要一个固有的延时,一般在10ns左右,即普通IO和普通片内信号从输入到BUFG输出有一个约10ns左右的固有延时,但是BUFG的输出到片内所有单元(IOB、CLB、选择性块RAM)的延时可以忽略不计为“0”ns。

5. Logic + DCM + BUFG的使用方法:

DCM同样也可以控制并变换普通时钟信号,即DCM的输入也可以是普通片内信号。使用全局时钟资源的注意事项全局时钟资源必须满足的重要原则是:使用IBUFG或IBUFGDS的充分必要条件是信号从专用全局时钟管脚输入。换言之,当某个信号从全局时钟管脚输入,不论它是否为时钟信号,都必须使用IBUFG或IBUFGDS;如果对某个信号使用了IBUFG或IBUFGDS硬件原语,则这个信号必定是从全局时钟管脚输入的。如果违反了这条原则,那么在布局布线时会报错。这条规则的使用是由FPGA的内部结构决定的:IBUFG和IBUFGDS的输入端仅仅与芯片的专用全局时钟输入管脚有物理连接,与普通IO和其它内部CLB等没有物理连接。另外,由于BUFGP相当于IBUFG和BUFG的组合,所以BUFGP的使用也必须遵循上述的原则。

IBUFDS、IBUFGDS和OBUFDS都是差分信号缓冲器,用于不同电平接口之间的缓冲和转换。IBUFDS 是差分输入的时候用,OBUFDS是差分输出的时候用,而IBUFGDS则是时钟信号专用的输入缓冲器。

程序LVDS_GENERATE的说明:

Xilinx的Vertex系列FPGA均在IO端口集成了LVDS收发器。要采用LVDS差分标准传输信号,

需要对FPGA的IO端口进行配置,从而使综合工具在FPGA布局布线流程中,将LVDS驱动器结合到IO端口上。

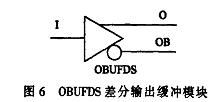

1、在发送端,应在IO端口配置OBUFDS模块(图6)。

OBUFDS OBUFDS_inst(

.O(O),//Diff_P output

.OB(OB) ,//Diff_n output

.I(I) //Buffer input

);

Defpamm OBUFDS_inst.DRIVE=12;

Defparam OBUFDS_inst.IOSTANDARD=“LVDS_25”;

Defparam OBUFDS_inst.SLEW=“SLOW”;

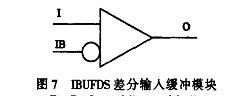

2、在接收端,应配置IBUFDS模块(图7)。

IBUFDS IBUFDS_inst (

.O(O) ,//buffer output

.I(I) ,//Diff_P buffer input

.IB(IB) //Diff_n buffer input);

//reflection the this defparam.

Defparam IBUFDS_inst.IOSTANDARD=“LVDS_25”;

3、IBUFGDS则是时钟信号专用的输入缓冲器

IBUFGDS #(

.DIFF_TERM ("TRUE" ),

//时钟信号专用的输入缓冲器// Differential Termination

.IOSTANDARD ("LVDS_25" )

// Specifies the I/O standard for this buffer

)

IBUFGDS_inst (

.O (clk74m_ibuf ), // Clock buffer output

.I (clk74m_p ), // Diff_p clock buffer input

.IB (clk74m_n ) // Diff_n clock buffer input

);

Spartan-6是面向低成本的低端产品。

spartan 6里bufio2到底怎么用

来源:FPGA开发实用教程 第4节 Xilinx公司原语的使用方法

http://www.eefocus.com/article/08-03/37457s.html

BUFG如果要对全局时钟,实现PLL或DCM等时钟管理,则需要手动例化该缓冲器。

IBUFDS原语用于将差分输入信号转化成标准单端信号,且可加入可选延迟。

IBUFDS原语的例化代码模板如下所示:

// IBUFDS: 差分输入缓冲器(Differential Input Buffer)

// 适用芯片:Virtex-II/II-Pro/4, Spartan-3/3E

// Xilinx HDL库向导版本,ISE 9.1

IBUFDS #(

.DIFF_TERM("FALSE"),

// 差分终端,只有Virtex-4系列芯片才有,可设置为True/Flase

.IOSTANDARD("DEFAULT")

// 指定输入端口的电平标准,如果不确定,可设为DEFAULT

) IBUFDS_inst (

.O(O), // 时钟缓冲输出

.I(I), // 差分时钟的正端输入,需要和顶层模块的端口直接连接

.IB(IB) // 差分时钟的负端输入,需要和顶层模块的端口直接连接

); // 结束IBUFDS模块的例化过程

OBUFDS将标准单端信号转换成差分信号,输出端口需要直接对应到顶层模块的输出信号,和IBUFDS为一对互逆操作。

OBUFDS原语的例化代码模板如下所示:

// OBUFDS: 差分输出缓冲器(Differential Output Buffer)

// 适用芯片:Virtex-II/II-Pro/4, Spartan-3/3E

// Xilinx HDL库向导版本,ISE 9.1

OBUFDS #(

.IOSTANDARD("DEFAULT")

// 指名输出端口的电平标准

) OBUFDS_inst (

.O(O), // 差分正端输出,直接连接到顶层模块端口

.OB(OB), // 差分负端输出,直接连接到顶层模块端口

.I(I) // 缓冲器输入

); // 结束OBUFDS模块的例化过程

IBUFGDS是IBUFG的差分形式,当信号从一对差分全局时钟管脚输入时,必须使用IBUFGDS作为全局时钟输入缓冲。

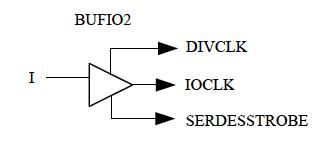

BUFIO2:全局时钟脚输入,产生一个同频的时钟,一个整数分频和占空比可调的时钟,一个用于SERDES的控制信号;每一个GCLK连接着两个BUFIO。

BUFPLL:图1所示为BUFPLL的原语,主要用来驱动高速I/O,为ISERDES2和OSERDES2提供时钟。

它会将PLL的LOCK输出与GCLK、SERDES选通和PLL时钟对齐。其中的IOCLK仅仅是将输入时钟通过了一级缓冲的版本。LOCK输出信号其实与PLL的LOCKED信号具有相同的功能,它们的区别在于,在PLL 锁定、BUFPLL对齐SERDES选通信号之前,LOCK不会变高。

Spartan-6器件每个BANK有两个BUFPLL,专用于PLL,不建议将其用作逻辑时钟。

来源:http://bbs.21ic.com/icview-274771-1-1.html

http://xilinx.eefocus.com/yq000cn/blog/

S6时钟资源整理:

S6系列的芯片提供16个全局时钟网络,并提供40个区域时钟,用于ISERDES和OSERDES串并转化或者并串转换;全局时钟网络被BUFGMUX驱动,区域时钟被BUFIO2驱动,PLL被BUFPLL驱动;BUFIO2和BUFPLL只用于IO clock;

16个时钟网络被16个BUFGMUX驱动,BUFGMUX的时钟来源有三个:上下bank的时钟源,左右bank的时钟源和内部来自DCM/PLL的内部时钟;这些时钟源通过位于FPGA中部的时钟交换矩阵到达整个FPGA;

BUFG是用BUFGMUX做出来的,即将BUFGMUX固定选择一个时钟就是BUFG了;BUFGCE也是来自BUFGMUX,即BUFGMUX是真正的物理资源;

BUFIO2:全局时钟脚输入,产生一个同频的时钟,一个整数分频和占空比可调的时钟,一个用于SERDES的控制信号;每一个GCLK连接着两个BUFIO。BUFIO可以设定和输入时钟反向;

扩展频谱的时钟可以通过配置DCM_CLKGEN来产生;

DDR2,LVDS和ISERDES,OSERDES时钟部分的设计可以参考该文档;