matlab sar adc建模,Simulink环境下的SAR ADC行为建模与仿真分析

韩笑 孙玲 吴秀山

摘 要: 逐次逼近型模/数转换器由于电路复杂度较低,且功耗和速度等性能可以随着集成电路工艺的进步而不断提升,在高速、高精度ADC設计中被广泛应用。借助Matlab软件环境下的Simulink工具,该文以14位SAR ADC为例给出了电路的行为级建模方法,分析了SAR ADC采样频率、输入信号频率以及内部时钟之间的关系,充分讨论了Simulink下各模块的具体实现并给出了仿真结果。该分析为SAR ADC的晶体管极电路设计与实现提供了重要参考依据。

关键词: 模/数转换器; 逐次逼近型结构; 行为级建模; Simulink

中图分类号: TN911?34; TN492 文献标识码: A 文章编号: 1004?373X(2017)06?0136?04

Abstract: The analog?to?digital converter (ADC) of the successive approximation register (SAR) has been widely used in the design of the high?speed and high?precision ADC because its circuit complexity is low, and its performances such as power dissipation and speed can be constantly improved with the improvement of the integrated circuit technique. By virtue of the Simulink tool under Matlab software environment, the 14?bit SAR ADC is taken as an example to give the behavior modeling method of the circuit, and the relationship among the sampling frequency, input signal frequency and internal clock of SAR ADC is analyzed. Each module implemented with Simulink is discussed, and the simulation results are given. The simulation analysis provides an important reference for the design and implementation of the transistor circuit of SAR ADC.

Keywords: ADC; successive approximation register; behavioral modeling; Simulink

近年来电子技术发展迅猛,随处可见的电子产品不仅使人们的日常生活变得更加便捷,还丰富了人们的娱乐生活。模/数转换器(Analog?to?Digital Converter,ADC)作为连接数字世界和模拟世界的桥梁,是现代电子信息系统中必不可少的一个重要电路单元[1?2]。目前常用的ADC有全并行结构(FLASH)、分级型结构(Subranging)、流水线结构(Pipeline)、折叠插值型结构(Folding and Interpolating)、∑?Δ型结构和逐次逼近型结构(SAR: Successive Approximation Register)等实现方式[3?4]。其中,SAR ADC由于电路复杂度较低,且功耗和速度等性能随着集成电路工艺的进步而不断提升,在高速、高精度ADC设计中被广泛应用[5?8]。

尽管SAR ADC的电路结构相对简单,但却有多种不同的晶体管级实现方法[9?10]。深刻掌握该电路的工作原理,及其采用、量化以及编码这一工作流程,对晶体管级的实现将起到事半功倍的作用。本文借助Matlab软件环境下的Simulink工具完成了一个14位SAR ADC的行为级建模,在分析SAR ADC采样频率、输入信号频率以及内部时钟之间关系的基础上详细仿真分析了电路的工作原理和各模块间的工作流程,具体介绍如下。

1 SAR ADC工作原理分析与建模

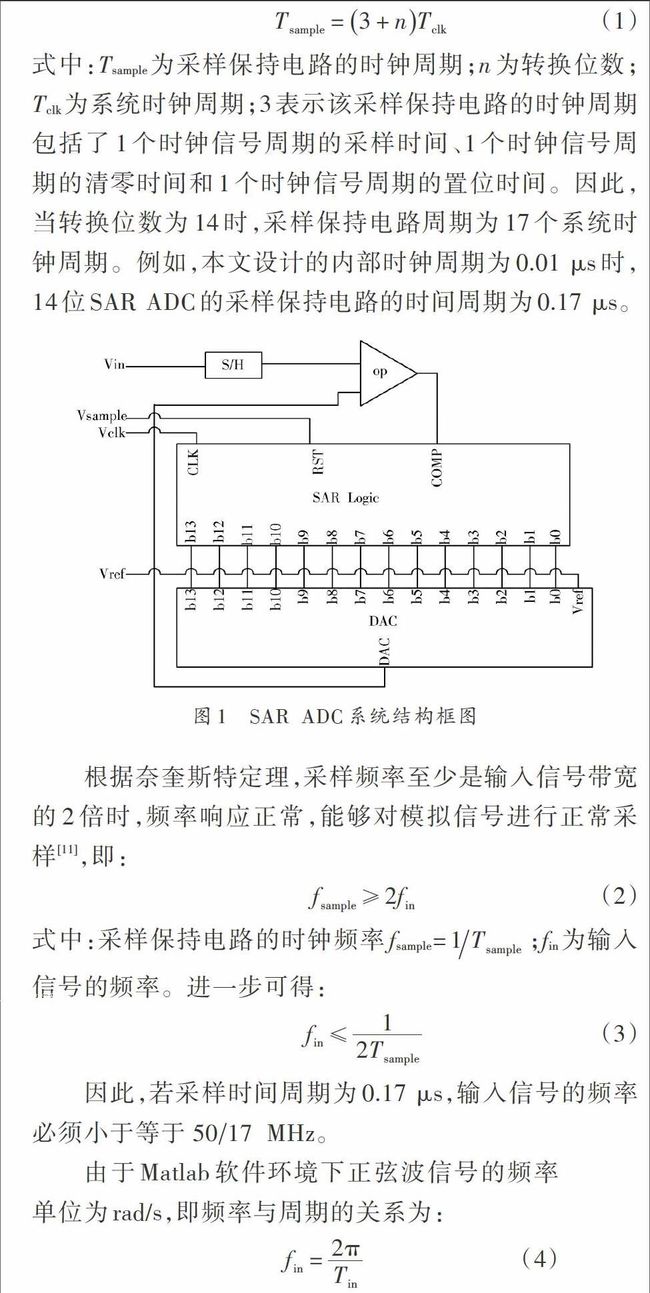

本文设计的14位SAR ADC系统结构如图1所示,它主要包括采样保持电路(Sample and Hold)、比较器电路(Operator)、逐次逼近寄存器(SAR Logic)以及数/模转换电路(DAC)四个单元模块。下面分别给出各模块的分析与设计实现。

1.1 采样保持电路

采样保持电路是整个SAR ADC电路转换的起始点,其作用是采集当前时刻模拟信号的电压值,并使该电压值保持一定时间以供后续电路进行量化处理。考虑到从该电压值的采集到量化过程结束所需的时间,并结合后续移位寄存器的清零和置位要求,本文将采样保持电路时钟周期与系统时钟周期的关系设置为:

1.2 比较器电路

比较器电路用来比较采样保持电路输出电压与DAC电路输出电压,当采样保持电路输出电压大于DAC电路输出电压时,比较器输出为高电平;当采样保持电路输出电压小于等于DAC电路输出电压时,比较器输出为低电平。

1.3 逐次逼近寄存器

1.3.1 D触发器设计

逐次逼近寄存器主要由D触发器构成。由于Simulink工具自带的D触发器仅有清零功能,而逐次逼近寄存器还需要有复位功能以使得一次采用过程结束后能够为下一次采用过程做好准备。为了使D触发器具有如表1所示的功能,本文设计了如图2所示的带有清零和置位功能的D触发器行为级模型,图2中的清零端和置位端都为高电平有效。当置位端为高电平时,输出为1;当置位端为低电平,清零端为高电平时,输出为0。

1.3.2 寄存器设计

图3给出了本文设计的逐次逼近寄存器行为级模型的结构示意图。图3主要分为上下两部分,上半部分由14个如图2所示的D触发器构成,用来在时钟周期下将信号1从最高位移至最低位;下半部分也是由14个D触发器构成,用以读取来自比较器的输出信号COMP。表2为整个寄存器工作的转换流程。

由表2可见,本文设计的寄存器工作流程为:第1个时钟周期下,图3中上半部分左边第1个触发器置位;第2个时钟周期下,图3中下半部分所有触发器清零;第3个时钟周期下,图3下半部分左边第1个触发器开始置位;第4个时钟周期开始寄存器输出COMP结果并保持到采用过程结束。

由于寄存器的每个输出端对应的保持时间不同,因此,本文在图3下半部分所有触发器的CLK端和D端设计了专门的电路。以下半部分左边第1个触发器为例,由于该触发器仅需要前两个系统时钟周期完成清零,随后的两个系统时钟周期完成比较输出,之后的13个系统时钟周期内始终保持输出不变,所以设计中增加了C1信号和C2信号。其中,C1信号在触发器完成比较输出所对应的两个系统时钟周期内为高电平,即第3和第4个系统时钟周期内为高电平,其余时刻为低电平;C2信号在前4个系统时钟周期内为高电平,其余时刻为低电平。同理,图3中的C3信号在第4和第5个系统时钟周期内为高电平,其余时刻为低电平;C4信号在前5个系统时钟周期内为高电平,其余时刻为低电平。以此类推直到最后一个D触发器。

1.4 DAC电路设计

DAC电路的主要功能是将数字信号转化为模拟信号,图4为设计的DAC电路行为级模型,主要由14个乘法器和一个加法器构成,其输出模拟电压值与输入数字信号的关系为:

[vo=Vref214i=013Di?2i] (5)

式中:Vref为参考电压值,本例中该参考电压设置为2 V;Di为输入的14位数字量。

2 行为级仿真分析

本设计中采用正弦波信号作为SAR ADC的输入信号,该输入信号的周期设置为3.4 μs,采样保持电路周期为0.17 μs,仿真时间设为4 μs,使用示波器模塊scope来观测Simulink下的行为级仿真波形。图5为仿真时间内采样保持电路的输出波形,相应时间下DAC电路的输出波形如图6所示。

选取采样保持电路输出为1 V时,放大对应的DAC电路输出波形,得到如图7所示结果。此时,逐次逼近寄存器14位数字输出结果为10 000 000 000 000,即1 V输入电压对应的输出数字量。

3 结 语

由于SAR ADC在精度、速度、功耗和成本等方面的综合优势,使得其仍然是工业界与学术界在实现高速、高精度ADC时可选的主流结构之一。本文以14位SAR ADC为例,介绍了Simulink工具下SAR ADC的行为级建模方法,详细讨论了各单元模块的设计实现,分析了输入输出信号间的关系,给出了仿真结果。为深刻学习掌握SAR ADC的工作原理,全面了解各模块间的相互关系,为后续更好地进行SAR ADC的晶体管设计奠定了坚实的基础。

注:本文通讯作者为孙玲。

参考文献

[1] 王祁钰.8位纳米级高速SAR A/D转换器设计[D].西安:西安电子科技大学,2014.

[2] 杨明,赵毅强,夏璠.基于混合编码DAC的低功耗SAR ADC设计[J].微电子学与计算机,2013,30(7):92?94.

[3] 居水荣,魏天尧,朱樟明.超低功耗逐次逼近寄存器型模数转换器的设计[J].半导体集成电路,2015,40(3):174?180.

[4] 李现坤,张瑛,郭宇锋,等.一种10 bit MS/s SAR ADC的设计实现[J].计算机技术与发展,2014,24(8):211?214.

[5] SONG Yan, XUE Zhongming, YAN Pengcheng, et al. A 0.6?V 8.3?ENOB asynchronous SAR ADC for biomedical applications [J]. Journal of semiconductors, 2014, 35(8): 158?164.

[6] WANG Ya, XUE Chunying, LI Fule, et al. A low power 11?bit 100 MS/s SAR ADC IP [J]. Journal of semiconductors, 2015, 36(2): 1?5.

[7] 万鑫,谈熙.一种非二进制权重的高能效比逐次比较型模数转换器[J].固体电子学研究与进展,2013,33(4):383?388.

[8] WONG S S, CHIO U F, ZHU Y, et al. A 2.3 mW 10?bit 170 MS/s two?step binary?search assisted time?interleaved SAR ADC [J]. IEEE journal of solid?state circuits, 2013, 48(8): 1783?1794.

[9] 李文石.可编程采样率的超低功耗逐次逼近型模数转换器的设计[D].苏州:苏州大学,2013.

[10] 黄玲.一种12位1 MSps全差分SAR ADC的研究与设计[D].北京:北方工业大学,2014.

[11] 李庆山.一种带数字校准电路的10位SAR ADC设计[D].长沙:湖南大学,2013.