FPGA深度学习加速(1) - Xilinx ug892-Vivado design flows overview (Vivado设计流程简述) - 阅读笔记

FPGA深度学习加速(1)

Xilinx ug892-Vivado design flows overview 阅读笔记

ug892简述了Vivado的设计流程,官方文档链接:

https://china.xilinx.com/support/documentation/sw_manuals/xilinx2020_2/ug892-vivado-design-flows-overview.pdf

本篇简要地记录了阅读原文档的笔记,融入了笔者自己的理解,部分翻译了原文,现更新至第三章-Vivado工程模式(内容约占原文80%,非工程模式暂时不会用到,会在未来能够用到的时刻更新)。

目录

-

- FPGA深度学习加速(1)

- Xilinx ug892-Vivado design flows overview 阅读笔记

-

- 第一章:Vivado系统级设计流程

-

- 1.1 RTL-比特流设计流程

-

- RTL设计

- IP设计与系统级设计集成

- IP子系统设计

- I/O和时钟规划

- Xilinx平台开发板支持

- 综合

- 设计分析与仿真

- 布局和布线

- 硬件Debug及验证

- 1.2 RTL-比特流之外的设计流程

-

- 加速内核流程(Accelerated Kernel Flows)

- 嵌入式处理器设计

- 基于模型的设计:使用模型生成器(Model Composer)

- 基于模型的DSP设计:使用Xilinx系统生成器(Xilinx System Generator)

- 高层次综合(HLS):基于C的设计

- 动态函数替换设计(Dynamic Function Exchange,DFx)

- 层次化设计

- 第二章:了解使用模式

-

- 2.1 使用Vivado IDE

- 2.2 使用Tcl命令

- 2.3 了解工程模式与非工程模式

-

- 工程模式

- 非工程模式

- 使用第三方工具

- 第三章:Vivado工程模式

-

- 3.1 Vivado工程模式的优势

- 3.2 创建工程

-

- 不同的工程类型

- 在工程模式下管理源码

- 3.3 了解流程向导(Flow Navigator)

- 3.4 执行系统级设计输入(System-Level Design Entry)

-

- 自动层次化源码编译和管理

- RTL开发

- 时序约束开发和验证

- 3.5 IP设计

-

- 配置IP

- 生成IP输出结果

- IP核容器

- 上下文无关的设计流程(Out-of-Context Design Flow)

- IP约束

- 验证IP

- 使用存储器IP

- 打包用户IP

- 更新IP

- 3.6 使用IP Integrator创建IP子系统

- 3.7 逻辑仿真

-

- 编译仿真库

- 仿真时间设定

- 设计流程中的早期功能仿真

- 使用结构化Netlist进行仿真

- 仿真流程

- 3.8 执行逻辑综合与实现

-

- 逻辑综合

- 实现

- 配置综合与实现的运行

- 使用增量编译运行实现

- 实现的工程变更(Implementing Engineering Change Orders, ECOs)

- 3.9 查看日志文件、消息、报告和属性

-

- 查看Log文件

- 查看消息

- 查看设计报告

- 查看或修改设备属性

- 3.10 打开设计进行设计分析和约束定义

-

- 打开细化的RTL设计(Elaborated RTL Design)

- 打开综合设计

- 打开实现设计

- 更新设计

- 切换视图

- 保存更改

- 关闭设计

- 分析实现报告

- 时序分析

- DRC、功耗和元件使用分析

- 3.11 设备编程、硬件验证与Debug

- 3.12 工程模式下的Tcl命令

第一章:Vivado系统级设计流程

本用户指南概述了如何使用Vivado®设计套件创建新的设计,以便在Xilinx®设备中编程。它简要描述了各种使用模型、设计特性和工具选项,包括准备、实现和管理设计源及IP核。Vivado设计套件提供了多种方法来完成Xilinx设备设计、实现和验证中涉及的任务:

- 传统的 RTL-比特流 设计流程(见1.1 RTL-比特流设计流程)

- 系统级集成流程,侧重于以IP为中心的设计和基于C的设计(见1.2 RTL-比特流以外的设计流程)

Vivado设计套件提供了一款IDE集成了上述功能。Vivado IDE为硬件设计的集成、实现和验证提供了接口。此外,所有设计流程都可以使用Tcl命令来运行。Vivado设计套件支持以下的设计标准:

- Tcl

- AXI4, IP-XACT

- Synopsys design constraints (SDC)

- Verilog, VHDL, VHDL-2008, SystemVerilog

- SystemC, C, C++

下图展示了Vivado设计套件的高层次设计流程:

1.1 RTL-比特流设计流程

RTL设计

RTL: Register Transfer Level,所谓RTL设计即是编写硬件描述语言代码进行硬件设计。Vivado支持指定RTL源文件来创建项目,并将这些源文件用于RTL代码开发、分析、合成和实现。Vivado的综合与实现支持多种源文件类型,包括Verilog、VHDL、SystemVerilog和XDC(Xilinx Design Constraints),详情见用户指南:ug895-vivado-system-level-design-entry 。而UltraFast侧重于RTL层次化设计及XDC的设计技术,并介绍了Vivado设计套件的高级特性及硬件设计性能优化方法,详情见用户指南:ug949-vivado-design-methodology 。

IP设计与系统级设计集成

IP: Intellectual Property,理解为已经设计并验证好的硬件模块。Vivado设计套件可以将IP作为独立模块或在系统级设计的上下文中进行配置、实现、验证和集成。自定义IP按照IP-XACT协议打包,然后通过Vivado IP目录提供。IP目录提供了对IP的快速访问,用于配置、实例化和验证IP。Xilinx IP利用AXI4互连标准实现更快的系统级集成。现有的IP可以在设计中使用RTL或netlist格式,详见用户指南:ug896-vivado-ip 。

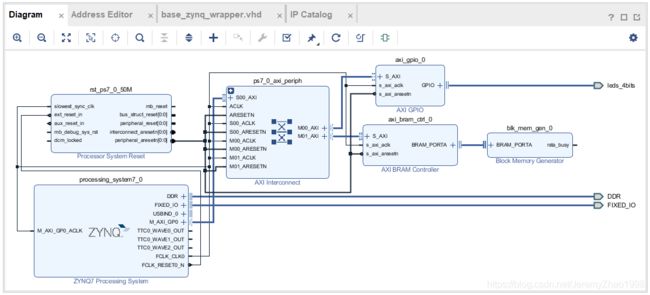

IP子系统设计

IP子系统指的是多个IP互连形成的子系统。Vivado IP integrator使用AMBA®AXI4互连协议将各种IP缝合到IP子系统中。连接过程可以使用图形界面,通过绘制与原理图类似的DRC来轻松连接整个接口,并提供了自动化链接以确保正确的IP配置和连接。详见用户指南:ug994-vivado-ip-subsystems

I/O和时钟规划

Vivado IDE提供了一个I/O管脚规划环境,该环境支持将I/O端口分配到特定的设备封装管脚或内部芯片板上。内存接口可以交互式地分配到特定的I/O组中,以获得最佳的数据流。Vivado pin planner用以分析设备和与设计相关的I/O数据。该工具还提供I/O DRC和同步开关噪声(SSN)分析命令,以验证I/O分配。详见用户指南:ug899-vivado-io-clock-planning。

Xilinx平台开发板支持

在Vivado设计套件中,可以选择现有的Xilinx平台开发板作为设计目标。目标板上实现的所有IP接口都是公开的,以便能够快速选择和配置设计中使用的IP。生成的IP配置参数和物理约束(如I/O标准和封装管脚约束)将自动分配并在整个设计中扩展。详见用户指南:ug895-vivado-system-level-design-entry 。

综合

所谓综合Synthesis,指的是将硬件描述语言转化为实际电路设计的过程。Vivado执行整体RTL设计的全局或自顶向下的综合,但在综合IP目录中的IP核,或IP Integrator中的模块时,Vivado设计套件使用上下文无关(OOC)或自底向上的综合。在层次化RTL设计中,也可以选择特定的模块或IP核进行上下文无关的综合。在层次化、模块化和团队协作的设计中,OOC设计流程是重要的技术手段。

设计分析与仿真

Vivado设计套件支持在设计过程的每个阶段分析、验证和修改设计,可以通过运行设计规则和设计方法检查、逻辑模拟、时序和功耗分析来提高电路性能,详见用户指南:ug906-vivado-design-analysis 。

Vivado模拟器支持在设计流程的不同阶段运行行为级和结构逻辑级仿真。该模拟器支持Verilog和VHDL混合模式仿真,仿真结果可以在vivadoide集成的波形查看器中显示。还可以使用第三方模拟器,这些模拟器可以集成到Vivado IDE中并从中启动。

布局和布线

当综合的netlist可用时,Vivado实现(implementation)提供了所有必要的功能,以优化、放置netlist并将其路由到目标部件的可用设备资源上。Vivado实现可以满足设计的逻辑、物理和时间限制。

对于具有挑战性的设计,Vivado IDE还提供了高级的层次规划功能,其中包括将特定逻辑约束到特定区域的能力,或手动放置特定设计元素并修复它们以供后续实现运行。详见用户指南:ug906-vivado-design-analysis 。

硬件Debug及验证

在实现(Implementation)之后,可以对设备进行编程,然后使用Vivado逻辑分析器进行分析,或者在独立的Vivado Lab Edition环境中进行分析。可以将Debug核添加到RTL源文件、综合netlist,或使用工程变更单(ECO)流实现的设计中。还可以修改连接到调试探测的网络,或者将内部信号路由到封装管脚,以便使用ECO流进行外部探测。详见用户指南:ug908-vivado-programming-debugging 。

1.2 RTL-比特流之外的设计流程

Vivado设计套件支持几种RTL-比特流之外的设计流程,这些高层次设计流程都从RTL-比特流设计流程衍生而来,因而同样适用上节的流程。

加速内核流程(Accelerated Kernel Flows)

Xilinx® Vitis™ 平台将加速用例引入Vivado® 流。Vitis使用Vivado的平台来添加加速内核(Accelerated Kernel),硬件设计由平台和加速器组成。在这种情况下,最终的比特流是由Vitis创建的,而完整的设计在Vivado中是不可见的,详见用户指南:ug1393-vitis-application-acceleration 。

嵌入式处理器设计

嵌入式处理器的设计,除硬件外还需要软件来进行系统的启动和有效运行,软硬件的设计须相一致,而两个域见的数据传递和相互验证是成功设计的关键。使用Vivado设计套件中的IP integrator可以进行嵌入式处理器的模块化设计,包括了处理器核及其接口的实例化、配置核集成。在IP核在实现(implementation)过程中被编译好之后,在Vitis™进行其相应的软件设计核验证。

Vitis设计套件是包含了Xilinx平台所有嵌入式应用程序和加速器的编译器。Vitis支持用更高级的语言进行开发,利用开源库,并支持特定领域的开发环境。有关嵌入式处理器设计流程,详见以下用户指南:ug898-vivado-embedded-design、ug940-vivado-tutorial-embedded-design、ug1046-ultrafast-design-methodology-guide 。

基于模型的设计:使用模型生成器(Model Composer)

模型生成器(Model Composer)是一种基于模型的图形化设计工具,可在MathWorks MATLAB®和Simulink®产品中实现快速设计探索,并通过自动代码生成加速Xilinx设备,详见用户指南:ug1262-model-composer-user-guide 。

基于模型的DSP设计:使用Xilinx系统生成器(Xilinx System Generator)

作为Vivado设计套件的一部分安装的Xilinx系统生成器工具可用于实现DSP功能。使用系统生成器创建DSP函数,并将其打包到Vivado IP 目录的IP模块中,其生成的IP可以作为子模块实例化到Vivado设计中,详见用户指南:ug897-vivado-sysgen-user 。

高层次综合(HLS):基于C的设计

Vivado设计套件中的高层次综合(HLS)支持使用C、C++、SystemC语言描述DSP函数,并应用到Vivado设计中。使用高级语言的特性可以更便捷地实现DSP函数,同时支持修改参数以优化性能。HLS支持在设计环境中直接使用基于C的测试用例进行RTL设计的仿真。C-RTL综合可以将基于C的设计转化为RTL模块,其可以打包并实现为大的RTL设计的一部分,或独立的IP integrator模块。详见用户指南:ug902-vivado-high-level-synthesis、ug871-vivado-high-level-synthesis-tutorial 。

动态函数替换设计(Dynamic Function Exchange,DFx)

动态函数替换(Dynamic Function Exchange,DFx)机制支持实时地修改Xilinx设备运行时的部分设计。可重构模块(reconfigurable modules)须合理地设计,保证其功能与性能的最优化,以及动态替换时的无故障操作,因此DFx有一套严格的设计流程,包括了减少进入可重构模块的接口信号数量、布局规划设备资源和引脚配置;以及遵守特殊的DFx drc。详见用户指南:ug909-vivado-partial-reconfiguration、ug947-vivado-partial-reconfiguration-tutorial 。

层次化设计

层次化设计(Hierarchical Design)可以将复杂的功能拆分为更容易实现的子功能。层次化设计的流程包括了合理的模块接口设计、限制(constraints)定义、布图规划以及特殊命令和设计技巧等。层次化设计让子功能的设计独立于整体系统,减少了顶层模块的复杂程度,也更有利于团队协作和模块复用。Vivado设计套件的很多功能支持层次化的设计流程,详见用户指南:ug905-vivado-hierarchical-design 。

第二章:了解使用模式

以下的用户指南介绍了Vivado设计套件快速入门:ug910-vivado-getting-started,包括了系统支持、安装和打开方式。在阅读本章前可以阅读该指南进行基本的Vivado安装。

本章讲述了Vivado设计套件的使用模式。上一章所描述的设计流程,Vivado设计套件中都提供了相应的支持,本章介绍使用Vivado的以下几个使用模式:

- 使用界面:图形用户界面Vivado IDE / Vivado Tcl命令行

- 设计模式:工程模式(Project Mode) / 非工程模式(Non-Project Mode)

- 与版本控制系统的交互

- 第三方设计工具的使用

2.1 使用Vivado IDE

Vivado IDE将设计流程中的每一项操作都集成到了用户界面中,包括IP子系统连接IP核、管脚配置等等步骤都可以直观地在图形化的界面进行操作。具体的功能和操作见用户指南:ug893-vivado-ide。上图展示了Vivado IDE打开Xilinx官方例程的界面。

2.2 使用Tcl命令

如果用户更习惯使用命令行,Vivado提供了独立于IDE的Tcl Shell,可以使用命令行,或编写Tcl脚本来进行设计流程的控制。此外,如上图下部所示,Vivado IDE之中也可以使用Tcl命令行来控制或获取工程信息。具体的方法见用户指南:ug894-vivado-tcl-scripting、ug835-vivado-tcl-commands。

Xilinx在Github开放了开源的Tcl脚本社区,用户可以从Tool→Settings中找到Xilinx XHub Stores,下载开源的Tcl脚本,或向社区贡献自己的开源脚本。

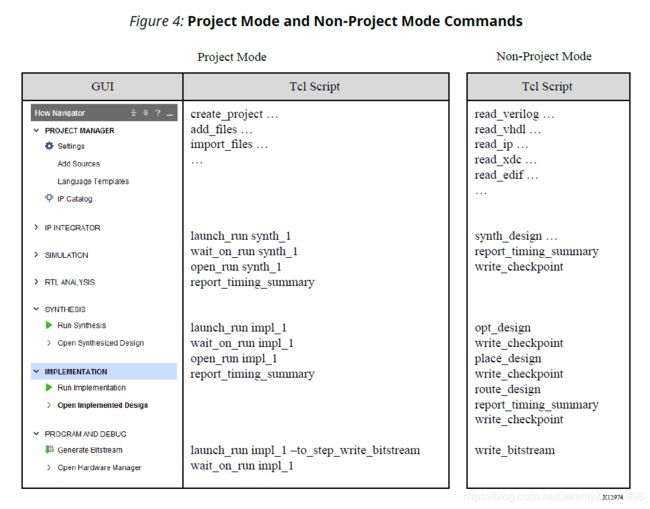

2.3 了解工程模式与非工程模式

工程模式(Project Mode)和非工程模式(Non-Project Mode)时Vivado的两种主要使用模式,两种模式都受Vivado IDE和Tcl命令的支持,其中Vivado IDE为工程模式提供了很多便捷的功能,而非功能模式可以更轻量地通过Tcl命令直接运行。

工程模式

工程模式的主要优势在于,充分利用Vivado设计套件的功能。Vivado自动建立工程文件夹,将工程的所有环节纳入控制,并可以将多个环节或操作自动化进行。例如,在综合后修改HDL源码,系统会自动提示进行重新综合;整个工程可以一键运行,等等。工程模式将在本用户指南第三章详细介绍。

非工程模式

非工程模式可以让用户通过Tcl命令完全自主地控制整个设计流程的每一个阶段,其优势在于灵活、高自主权。用户可以自主建立工程文件夹,手动地通过Tcl命令来执行设计流程中的步骤。非工程模式将在本用户指南第四章详细介绍。

工程模式与非功能模式在使用方式和Tcl命令方面都有一些不同,以下的表格总结了这些差异:

使用第三方工具

Vivado设计套件也支持一些第三方的综合与仿真工具,具体细节和支持见原文档和官网,在此不再细述。

第三章:Vivado工程模式

3.1 Vivado工程模式的优势

如上文所述,Vivado工程模式为项目自动创建工程文件,提供一键运行仿真、综合或实现的用户界面,以及自动生成标准的设计报告。工程模式可以最简便地利用Vivado的强大功能,是官方推荐的使用模式。工程模式的优势有以下几点:

- 自动管理项目状态、HDL源码、约束文件、IP核和模块设计

- 生成和保存综合和实现结果

- 高级设计分析功能,包括从实现结果到RTL源文件的交叉检测

- 使用运行策略(Run Strategies)自动设置命令选项并生成标准报告

- 支持创建多个运行结果,以配置和探索可用的约束或命令选项

3.2 创建工程

不同的工程类型

- RTL工程:从RTL源码开始创建工程,经历RTL源码 - 生成IP - 设计IP子系统 - 综合 - 实现 - 布线和分析等流程

- 综合后工程:导入第三方综合netlist,经历实现 - 布线和分析等流程

- I/O规划工程:创建只有I/O规划,而尚未有RTL实现的空工程

- 导入工程:从Xilinx其它软件平台导入已有的工程

- 例程:Xilinx官方提供的基于具体开发板的例程

- DFx:动态地、实时地添加部分比特流文件,修改设备的可重构部分

在工程模式下管理源码

工程模式提供了便捷的源码管理功能,任何层次的源码(RTL源码、IP、约束、仿真)都可以导入工程,而在导入源码时,不论是远程的还是本地的,工程模式都会记录源码修改的记录,并在工程中相关联的流程进行更新提示。工程模式还会自动检测源码的include依赖。此外,工程模式还会在窗口显示编译顺序或代码逻辑层级,帮助检查缺失的模块。File → Project → Archive可以支持将工程文件打包为.zip压缩包,其中远程源码会被复制到本地的.zip。

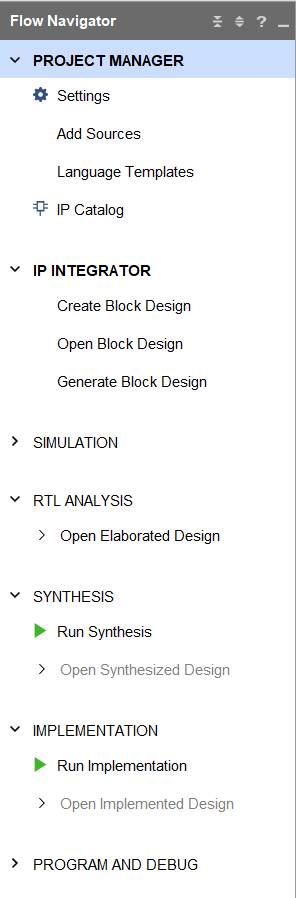

3.3 了解流程向导(Flow Navigator)

Vivado界面左侧的控制栏即是流程向导,如下图

流程向导展示了设计流程中各个步骤的执行入口,其中尚不能执行的步骤会变为灰色,直到其依赖的前序步骤完成。不同的工程模式下流程向导中的入口种类有相应的不同。

3.4 执行系统级设计输入(System-Level Design Entry)

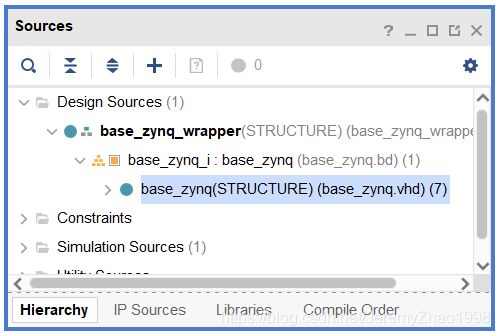

自动层次化源码编译和管理

上图展示了源码管理窗口,其中层次化地显示出工程文件中已有的源码,源码根据它们被编译的顺序排列。如果用户没有为工程明确指定了顶层模块,Vivado会自动检测顶层模块。

RTL开发

Vivado提供了一系列有利于RTL开发的功能,包括内置的IDE、自动格式检测、语言模板、搜索模板库、RTL优化和交互式分析、设计规则检查、管脚约束和I/O布局等。

时序约束开发和验证

Vivado IDE提供了时序约束编辑窗口,可以定义和编辑时序约束,该窗口在综合与实现之后可用。

3.5 IP设计

Vivado设计套件支持以IP为中心的设计流程,IP可以在Vivado IDE中被创建、配置和整合。Vivado提供了IP目录,其中包含了Xilinx LogiCORE™ IP中的大量IP可供配置和使用,同时用户自己设计的IP也可以通过IP-XACT协议打包并在IP目录中使用。

配置IP

上图所示的IP目录中包含了大量的IP,其中使用权限有Included(无需额外付费)和Purchase(需要付费)两种,在Reports → Report IP Status选项中可以查看IP的权限情况。双击一个IP即可进入配置界面,将其实例化到工程中。当IP被配置并实例化后,Vivado为其生成一个.xci文件,记录了所有配置信息。

生成IP输出结果

IP输出结果(IP Output Product)让综合和实现工具可以使用特定的配置的IP。Vivado在生成IP输出结果时自动创建相应的文件夹,其中包括了实例化模板、RTL源文件和约束文件、综合设计检查点(Synthesized design checkpoint)、第三方仿真和综合源码、样例设计、测试文件、C模板等。在工程模式下,综合时会自动生成所有的IP输出结果,而在非工程模式下需要用户手动生成。

IP核容器

为了实现IP版本控制的简化,Vivado提供了一种IP核容器,将IP从松散的文件夹形式打包为二进制文件(XCIX文件),详细方法见用户指南:ug896-vivado-ip 。

上下文无关的设计流程(Out-of-Context Design Flow)

Vivado支持上下文无关的设计流程,即模块化地综合或实现IP系统中的每个子IP模块,这样会在最终的顶层模块综合时直接调用已经综合或实现好的子IP,节省最终的综合时间,并有利于模块的复用。在IP子系统中添加IP,或生成IP输出结果时都默认地采用上下文无关的设计流程。Vivado也支持从顶层开始的全局综合,用户可以在综合的过程中任意勾选全局综合所包含的子模块。在顶层模块综合开启前,设计报告中不会包含OOC综合模块的资源使用信息,因此如果想要获得更准确的项目是资源使用报告,应当开启顶层模块综合。

IP约束

详见用户指南:ug896-vivado-ip 。

验证IP

综合后的IP可以使用行为仿真核逻辑仿真来验证,实现后的IP可以验证时序、电源和资源使用情况。一般情况下可以使用一些特定的设计来验证工程设计(这些设计即称为Test Bench)。IP目录中的大多数IP都有Vivado生成的样例Test Bench,在源码中找到.xci文件,右击选择Open IP Example Design选项即可生成样例Test Bench。有关IP的样例Test Bench参见用户指南:ug896-vivado-ip,有关仿真参见用户指南:ug900-vivado-logic-simulation 。

使用存储器IP

详见用户指南:ug899-vivado-io-clock-planning、pg150-ultrascale-memory-ip、xapp1180。

打包用户IP

用户自己创建的IP可以被打包和加入IP目录,用户IP的来源可以是RTL源码、一个IP子系统或一整个工程。在Tools → Settings选项中可以指定用户IP放置的默认文件夹,该文件夹下打包好的IP会在IP目录中显示。Create and Package IP窗口可以引导用户一步步创建和配置IP核。注意,在打包和使用用户IP前应首先确保其设计的正确性。详见用户指南:ug1118-vivado-creating-packaging-custom-ip、ug1119-vivado-creating-packaging-ip-tutorial 。

更新IP

Vivado提供的IP会持续更新,因此在用户项目中使用的IP应当在新版本中作相应的更新。用户也可以选择在工程中使用静态的IP而无需更新。

3.6 使用IP Integrator创建IP子系统

IP Integrator是用以创建模块设计(Block Design, .bd)的窗口,其支持快速将多个IP或Xilinx嵌入式设备通过AXI4协议相连接。如上图,IP Integrator可以图形化地连接各IP的接口,其生成的模块设计.bd文件可以保存以供在其他工程设计中复用。详见用户指南:ug994-vivado-ip-subsystems、ug898-vivado-embedded-design 。

3.7 逻辑仿真

Vivado提供了内置于IDE的仿真器,实现各个层次的仿真,上图展示了各层次的仿真在设计流程中的使用。此外Vivado还支持一些第三方仿真器的使用,详见用户指南:ug900-vivado-logic-simulation 。

编译仿真库

在使用Vivado内置仿真器时,Vivado自动编译了需要用到的仿真库,但使用第三方仿真器时应注意提前编译仿真库,在Tools →

Compile Simulation Libraries选项中。

仿真时间设定

Vivado推荐用户使用1ps的仿真时间粒度。过于精细的时间粒度会被截断或四舍五入,而过于粗糙的时间粒度也并不会显著提升性能。

设计流程中的早期功能仿真

在RTL代码被综合前,使用功能仿真来验证代码语法和功能的正确性。Vivado推荐用户在大型工程中独立地对每个IP或子模块进行功能仿真,再对顶层模块进行功能仿真,而在最后的流程使用相同的Test Bench进行时序仿真。

使用结构化Netlist进行仿真

所谓Netlist理解为RTL源码综合或实现之后的结果,Netlist仿真在综合或实现之后进行,用于检查综合或实现过程中配置带来的错误。Netlist仿真对于Verilog语言支持功能和时序仿真,而对其他语言仅支持功能仿真。从File → Export → Export Netlist选项中可以调用已经综合或实现的模块的Netlist。对于时序仿真,其耗费的运行时间可能较长,但这是最接近硬件实现的仿真方式。

仿真流程

Vivado支持内置于IDE的集成仿真(Integrated Simulation),同时也支持使用脚本和外部验证环境的批仿真(Batch Simulation)。集成仿真可以在IDE中一键运行仿真器或第三方仿真器,而如果用户所使用的外部验证环境包含了自动检查的Test Bench,则推荐使用脚本生成批仿真。具体的方法见用户指南:ug900-vivado-logic-simulation 。

3.8 执行逻辑综合与实现

逻辑综合

Vivado IDE内置了综合选项,并支持并行综合多个模块,在Linux版本下的Vivado还支持将项目提交到远程服务器进行综合。详见用户指南:ug901-vivado-synthesis 。

实现

与逻辑综合相似,实现也可以在Vivado IDE中并行实现多个模块,或对同意模块的不同约束配置进行实现,得到不同的设计报告。详见用户指南:ug904-vivado-implementation、ug903-vivado-using-constraints。

配置综合与实现的运行

在工程模式下,用户可以提前定义好一套综合与实现的运行配置(Run Strategies),也可以将多种配置保存用于综合与实现。在配置好综合与实现配置后,可以采用以下几种方式运行综合或实现:

- 在Flow Navigator窗口,选择Run Synthesis, Run Implementation, or Generate Bitstream 或 Generate Device Image选项

- 在Design Runs窗口,选择一个运行程序,右键选择Launch Runs

- 在上方选项的Flow → Run Synthesis, Flow → Run Implementation, 或 Flow → Generate Bitstream 或 Generate Device Image

同时运行多个综合或实现进程,可以在Flow Navigator窗口右击Synthesis或Implementation,选择Create Synthesis Runs或Create Implementation Runs,添加多个进程同时运行。在Design Runs窗口可以编辑运行的配置,Vivado IDE会自动展示已经激活的运行的相关信息,双击一个运行可以显示其详细信息。

使用增量编译运行实现

在对工程项目进行少量修改的时候,Vivado支持工程进行增量编译,保留大部分原有的实现结果,节约时间和计算资源。在Implementation Settings窗口,或Design Runs窗口右击可以选择Set Incremental Compile选项。详见用户指南:ug904-vivado-implementation 。

实现的工程变更(Implementing Engineering Change Orders, ECOs)

为了将工程变更对源码的影响降到最低,Vivado ECOs机制支持对已有的实现netlist进行修改,重新实现后生成比特流,详见用户指南:ug904-vivado-implementation 。

3.9 查看日志文件、消息、报告和属性

查看Log文件

界面下部的Log窗口可以查看综合、实现和仿真过程中的Log文件,这些Log信息还会被写入Vivado launch文件夹的vivado.log文件中。

查看消息

界面下部的Messages窗口层次化地展示了各个设计流程的消息,包括了Error、Warning、Info等。

查看设计报告

界面下部的Report窗口展示了各环节的设计报告入口,从中双击任意一个报告可以在IDE的文本编辑器中显示。工程模式下默认展示标准的设计报告,用户还可以通过Tcl脚本自行定义设计报告。

查看或修改设备属性

当综合或实现设计窗口打开时,可以通过Tools → Edit Device Properties选项查看或修改与比特流相关的设备属性信息,如上图。

3.10 打开设计进行设计分析和约束定义

在完成RTL设计、综合或仿真后,都可以打开相应的设计以查看设计分析。Vivado专门定义了“打开设计”功能,当设计被打开时,Vivado会编译设计netlist,为其配置与所选设备相匹配的管脚约束。虽然Vivado支持同时打开多个设计进行交叉分析,但若无此需求,建议每次打开一个设计以节省计算机内存。许多与设计分析和管脚约束的功能仅在相应设计被打开时才可用。

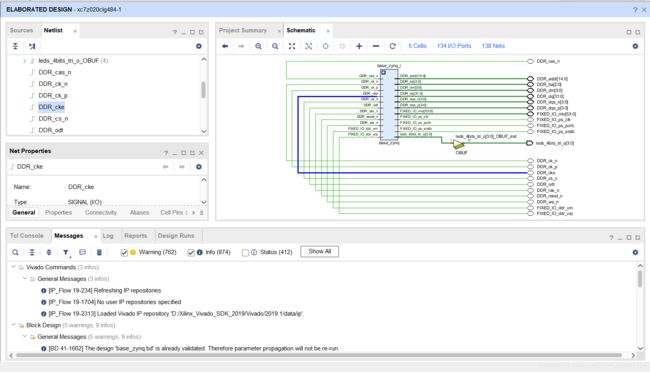

打开细化的RTL设计(Elaborated RTL Design)

在RTL设计打开后,用户可以在Message窗口查看Error信息并点击链接进行修改,示意图窗口(Schematic Window)可以查看RTL设计的连接和层次化信息,其中每一条连线都可以对应到RTL Netlist中。但RTL设计不包含任何与FPGA相关联的映射,因此一些与综合后有关的管脚约束可能会在RTL设计中报出Warning信息,这些不匹配在综合后就会消失。同样由于上述原因,Vivado推荐在综合后进行I/O和管脚约束的配置。

打开综合设计

与RTL设计相似,综合设计打开后也有一系列窗口配置约束等信息,此时的Device窗口展示了综合结果到电路图的映射。在综合设计中还可以添加测试模块来进行综合结果的验证,详见用户指南:ug908-vivado-programming-debugging。

打开实现设计

在实现过后,实现设计会包含最接近真是设备的设计情况,包括了时序、功耗、元件使用分析等,详见用户指南:ug906-vivado-design-analysis。

更新设计

当设计流程中后序的流程完成后,前序的某一流程发生了更改,会导致后序流程的结果“失效”,即仍然可用,但没有与更新后的前序流程相匹配,例如综合后修改了RTL源码,旧的综合结果即失效。此时Vivado提供了失效检查和更新功能,在失效提醒信息中点击More Info,或直接关闭失效的设计再重新打开,后序设计将会自动更新(重新执行)。

切换视图

如上图右上角所示的视图切换可以在各种特定视图下完成特定的功能。

保存更改

用户界面做出对项目任一流程配置信息的更改后,可以选择将更改存储到原有的配置文件,也可以选择另存为新的配置文件。点击File → Constraints → Save选项,或页面左上角的保存图标可以保存当前配置到原配置文件,新的配置将添加在原有配置之后。点击File → Constraints → Save As则可以将配置另存为额外的配置文件。

关闭设计

当前设计配置修改查看完毕时,为了节省计算机内存,建议点击叉号或在左侧点击关闭设计。

分析实现报告

实现报告的Device窗口展示了工程在开发板上的实际部署情况,时序结果窗口可以选择和高亮实际布线,而其他配置也可以在实现设计中修改和保存,详见用户指南:ug904-vivado-implementation。

时序分析

Tools → Timing选项中的工具可以配置时序分析,详见用户指南:ug906-vivado-design-analysis。

DRC、功耗和元件使用分析

Vivado IDE提供DRC、功耗和元件使用分析报告,其中的链接直接指向工程中相应的位置以便调试,使用Tools → Settings → Strategies → Report Strategies选项可以设置报告策略,以生成定制的报告。详见用户指南:ug906-vivado-design-analysis。

3.11 设备编程、硬件验证与Debug

Vivado IDE提供了多种工程的验证和Debug功能。可以构建Debug IP来验证RTL设计和综合结果,Vivado Logic Analyzer可以针对已经生成的比特流文件还可以进行硬件验证,详见用户指南:ug908-vivado-programming-debugging。

3.12 工程模式下的Tcl命令

Vivado工程模式的IDE中也可以键入Tcl命令来控制运行,常用命令如下:

更多Tcl命令见用户指南:ug835-vivado-tcl-commands。

工程模式下同样可以编辑和使用Tcl脚本

RTL工程的Tcl脚本如下形式:

# run_bft_kintex7_project.tcl

# BFT sample design

#

# NOTE: Typical usage would be "vivado -mode tcl -source

run_bft_kintex7_project.tcl"

# To use -mode batch comment out the "start_gui" and "open_run impl_1" to

save time

#

create_project project_bft ./Tutorial_Created_Data/project_bft -part

xc7k70tfbg484-2

add_files {./Sources/hdl/FifoBuffer.v ./Sources/hdl/async_fifo.v ./

Sources/hdl/bft.vhdl}

add_files -fileset sim_1 ./Sources/hdl/bft_tb.v

add_files ./Sources/hdl/bftLib

set_property library bftLib [get_files {./Sources/hdl/bftLib/round_4.vhdl \

./Sources/hdl/bftLib/round_3.vhdl ./Sources/hdl/bftLib/round_2.vhdl ./

Sources/hdl/bftLib/round_1.vhdl \

./Sources/hdl/bftLib/core_transform.vhdl ./Sources/hdl/bftLib/

bft_package.vhdl}]

import_files -force

import_files -fileset constrs_1 -force -norecurse ./Sources/

bft_full_kintex7.xdc

# Mimic GUI behavior of automatically setting top and file compile order

update_compile_order -fileset sources_1

update_compile_order -fileset sim_1

# Launch Synthesis

launch_runs synth_1

wait_on_run synth_1

open_run synth_1 -name netlist_1

# Generate a timing and power reports and write to disk

report_timing_summary -delay_type max -report_unconstrained -

check_timing_verbose \

-max_paths 10 -input_pins -file ./Tutorial_Created_Data/project_bft/

syn_timing.rpt

report_power -file ./Tutorial_Created_Data/project_bft/syn_power.rpt

# Launch Implementation

launch_runs impl_1 -to_step write_bitstream

wait_on_run impl_1

# Generate a timing and power reports and write to disk

# comment out the open_run for batch mode

open_run impl_1

report_timing_summary -delay_type min_max -report_unconstrained -

check_timing_verbose \

-max_paths 10 -input_pins -file ./Tutorial_Created_Data/project_bft/

imp_timing.rpt

report_power -file ./Tutorial_Created_Data/project_bft/imp_power.rpt

# comment out the for batch mode

start_gui

Netlist工程的Tcl脚本如下形式:

# Kintex-7 Netlist Example Design

#

# STEP#1: Create Netlist Project, add EDIF sources, and add constraints

#

create_project -force project_K7_netlist ./Tutorial_Created_Data/

project_K7_netlist/ -part xc7k70tfbg676-2

# Property required to define Netlist project

set_property design_mode GateLvl [current_fileset]

add_files {./Sources/netlist/top.edif}

import_files -force

import_files -fileset constrs_1 -force ./Sources/top_full.xdc

#

# STEP#2: Configure and Implementation, write bitstream, and generate

reports

#

launch_runs impl_1

wait_on_run impl_1

launch_runs impl_1 -to_step write_bitstream

wait_on_run impl_1

open_run impl_1

report_timing_summary -delay_type min_max -report_unconstrained -

check_timing_verbose \

-max_paths 10 -input_pins -file ./Tutorial_Created_Data/project_K7_netlist/

imp_timing.rpt

report_power -file ./Tutorial_Created_Data/project_K7_netlist/imp_power.rpt

#

# STEP#3: Start IDE for design analysis

#

start_gui