Verilog的基本用法

目录

- 1.数制的字母表示

- 2.位拼接运算符:

- 3.仿真精度 `timescale 1ns/1ps

- 4. `define 的使用

- 5. 异或运算符

- 6. 小数的二进制表示

- 7. 单端信号转差分信号

- 8. bt1120格式中的同步码 EAV 、SAV

- 9. 原码、反码、补码

- 10. 二进制数的加减乘除

-

- 10.1 二进制数的加减法

- 10.2 二进制数的乘法

- 11. &、&&以及单目运算符(&)的区别

- 12. “+:”、“-:”语法

- 13. `ifdef语法

- 14. bmp文件格式

- 15. for循环的用法

- 16. $fseek的用法

- 17. $fread的用法

- 18. if条件表达式

- 19. DDR芯片型号

- 20. vivado中多线程编译设置

1.数制的字母表示

| 字母 | 代表含义 |

|---|---|

| h | 十六进制 |

| d | 十进制 |

| o | 八进制 |

| b | 二进制 |

| 例子: |

数字表达式:<位宽><进制><数字>

eg. 4’b1110 表示4位二进制数1110

10’d0表示10位宽的数值0,0000000000

10‘d15,则表示十进制15, 0000001111。

2.位拼接运算符:

z={x,y}或z<={x,y}

若x=1110,y=0101,则z=11100101。

3.仿真精度 `timescale 1ns/1ps

先回忆一下秒数的进制转换:

1s = 103ms = 106us = 109ns = 1012ps

`timescale 仿真时间单位/时间精度

4. `define 的使用

参数定义常用的三种方法:

(1)define

(2)localparam

(3)parameter

define 与localparam和parameter最大的区别就是define 可以跨文件传递参数;parameter只能在模块间传递参数;而localparam只能在其所在的module中起作用,不能参与参数传递。

5. 异或运算符

在Verilog中^代表异或运算。

6. 小数的二进制表示

例:

( 1101.01 ) 2 = 1 × 2 3 + 1 × 2 2 + 0 × 2 1 + 1 × 2 0 + 0 × 2 − 1 + 1 × 2 − 2 = 13.25 (1101.01)_2=1\times2^3+1\times2^2 +0\times2^1+1\times2^0+0\times2^{-1}+1\times2^{-2} = 13.25 (1101.01)2=1×23+1×22+0×21+1×20+0×2−1+1×2−2=13.25

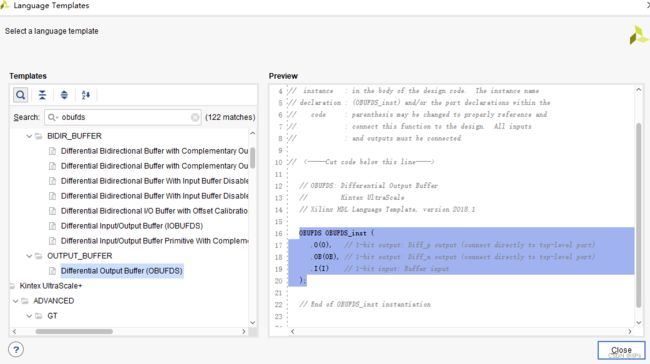

7. 单端信号转差分信号

采用OBUFDS原语:

OBUFDS OBUFDS_inst (

.O(O), // 1-bit output: Diff_p output (connect directly to top-level port)

.OB(OB), // 1-bit output: Diff_n output (connect directly to top-level port)

.I(I) // 1-bit input: Buffer input

);

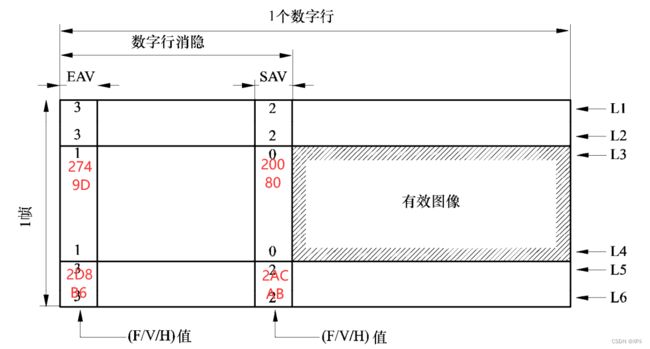

8. bt1120格式中的同步码 EAV 、SAV

| EAV(10bit) | SAV(10bit) | EAV(8bit) | SAV(8bit) | |

|---|---|---|---|---|

| 有效区域 | 274 |

200 |

9D |

80 |

| 消隐区域 | 2D8 |

2AC |

B6 |

AB |

9. 原码、反码、补码

- 原码: 原码的最高位为符号位,其余位均为数值位。

- 反码: 正数的反码等于原码;负数的原码符号位不变,数值位按位取反即为负数的反码。

- 补码: 正数的原码、反码、补码均相等;负数的反码+1即为补码;

10. 二进制数的加减乘除

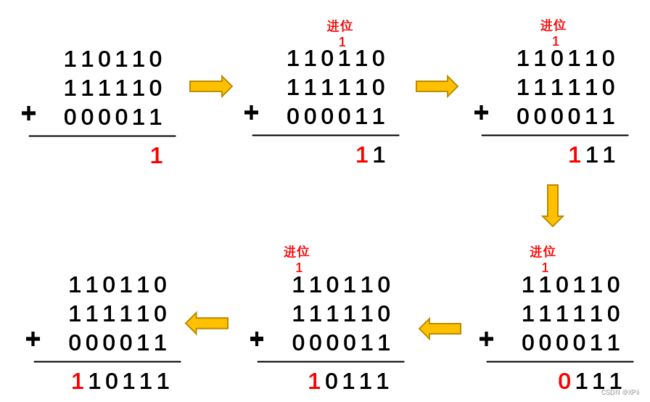

10.1 二进制数的加减法

二进制数的加减法Verilog编写方法:

- 将要进行加减的数据全部转换为补码。

- 选取位宽最大的那个数据的位宽+1作为计算结果的位宽。

- 将要进行加减运算的补码拓展符号位(正数为0,负数为1)至计算结果的位宽。

- 计算结果中的最高位即为符号位,其余位则为计算结果数据位。(此时的数据仍为补码,可根据需求将补码转换为原码输出即可)。

举例如下:

(-10)+(-2)+3

- -10的原码为1_1010,其反码为1_0101,则其补码为1_0110 ;

- -2的原码为1_10,其反码为1_01,则其补码为1_10 ;

- 3的原码为0_11,其反码、补码均为0_11 ;

- 最大位宽为5,故选取最终计算结果的位宽为6;

- 将-10的补码拓展至6位,即11_0110 ;

- 将-2的补码拓展至6位,即1111_10 ;

- 将3的补码拓展至6位,即0000_11 ;

- 即(-10)+(-2)+3=11_0110+1111_10+0000_11=1_10111(补码) ,计算过程如下图所示 ;

- 将1_10111转换为原码即为-9 。

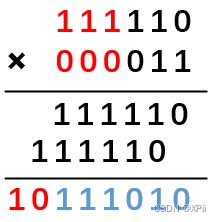

10.2 二进制数的乘法

二进制数的乘法Verilog编写方法:

- 将所有乘数全部转换为补码。

- 计算结果的位宽为乘数的位宽之和。

- 将乘数的补码拓展符号位(正数为0,负数为1)至计算结果的位宽。

- 计算结果位宽中的最高位即为符号位,其余位则为计算结果数据位。(此时的数据仍为补码,可根据需求将补码转换为原码输出即可)。

举例如下:

(-2)*3

- -2的原码为1_10,其反码为1_01,则其补码为1_10 ;

- 3的原码为0_11,其反码、补码均为0_11 ;

- -2的补码的位宽为3位,3的补码的位宽也为3位,故最终计算结果的位宽为3+3=6;

- 将-2的补码拓展至6位,即1111_10 ;

- 将3的补码拓展至6位,即0000_11 ;

- 即(-2)3=1111_100000_11=10_111010(补码) ,计算过程如下图所示 ;

- 因为计算结果的位宽为6位,因此只需取10_111010的低6位作为最终结果即可,即111010 。

- 此时的111010 仍为补码,转换为原码即为100110,即-6。

11. &、&&以及单目运算符(&)的区别

- &:按位与,即按位进行与。

- &&:逻辑与

- 单目运算符(&):如下所示

reg [2:0] A;

B= &A;

即B=((A[0]&A[1])&A[2])

12. “+:”、“-:”语法

reg [0 +: DATA_WIDTH] data;代表从0开始升序位宽为DATA_WIDTH。

即data[DATA_WIDTH-1:0]

+::位宽转换(升序)

********************Define:***********************

reg [15:0] test_big_vect;

reg [0:15] test_little_vect;

*********************Question:********************

test_big_vect[0 +:8]

test_little_vect[0 +:8]

*********************Answer:***********************

test_big_vect[0 +:8] => test_big_vect[7:0]

test_little_vect[0 +:8] => test_little_vect[0:7]

-::位宽转换(降序)

********************Define:***********************

reg [15:0] test_big_vect;

reg [0:15] test_little_vect;

*********************Question:********************

test_big_vect[15 -:8]

test_little_vect[15 -:8]

*********************Answer:***********************

test_big_vect[15 -:8] => test_big_vect[15:8]

test_little_vect[15 -:8] => test_little_vect[8:15]

13. `ifdef语法

`ifdef IMG_1080P

parameter IMAGE_WIDTH_VALID = 'd1920;

parameter IMAGE_HEIGHT_VALID = 'd1080;

`elsif IMG_720P

parameter IMAGE_WIDTH_VALID = 'd1280;

parameter IMAGE_HEIGHT_VALID = 'd720;

`else

parameter IMAGE_WIDTH_VALID = 'd1920;

parameter IMAGE_HEIGHT_VALID = 'd1080;

`endif

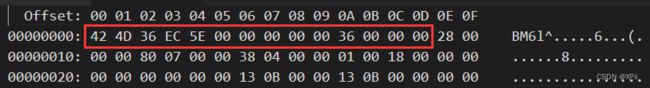

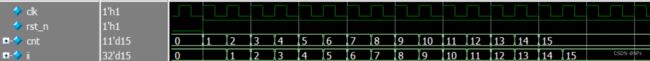

14. bmp文件格式

bmp以小端方式存储,即低地址存放低位数据,高地址存放高位数据。且Windows有“补零”的习惯!即要求位图的每一行像素所占字节数必须被4整除。若不能倍4整除,则在该位图每一行的十六进制码末尾“补”1至3个字节的“00”。

| 位置 | 字节数 | 描述 |

|---|---|---|

| 1-2 | 2 | 头文件字段,为0x4D42 |

| 3-6 | 4 | 整个.bmp的大小 |

| 7-10 | 4 | 保留字段,为0 |

| 11-14 | 4 | 图片信息的开始位置 |

| 15-18 | 4 | DIB header的大小,为0x28 |

| 19-22 | 4 | 图片宽度 |

| 23-26 | 4 | 图片高度 |

| 27-28 | 2 | 色彩平面的数量,为1 |

| 29-30 | 2 | 每个像素所占用的bit数 |

| 31-34 | 4 | 采用何种压缩方式,通常为0 |

| 35-38 | 4 | 原始位图数据的大小,对于不压缩的图片为0 |

| 39-42 | 4 | 横向分辨率(像素/米) |

| 43-46 | 4 | 纵向分辨率(像素/米) |

| 46-50 | 4 | 调色板中的颜色数量,通常为0 |

| 51-54 | 4 | 重要的颜色数量,通常为0,表示每种颜色都重要 |

-

由于是小端模式,所以刚开始的两个字节为0x4D42

-

接下来的4个字节为保留字节,为0

-

0x00000036即十进制的54,代表第54字节开始为有效的图像数据。

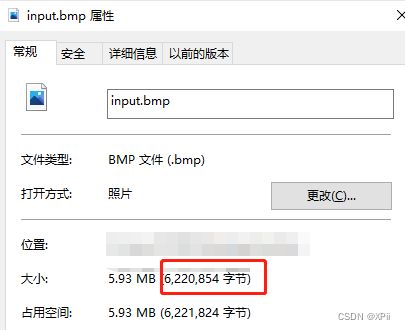

15. for循环的用法

Verilog中for循环的语法如下:

for(循环变量赋初值;循环需要满足的条件;循环变量的增值) begin

执行语句;

end

例:

reg [10:0] cnt=0;

integer ii;

initial begin

for ( ii=0 ;ii<15 ;ii=ii+1 ) begin

wait(rst_n);

cnt=cnt+1;

@(posedge clk);

end

end

代码运行结果如下图所示:

16. $fseek的用法

<integer> = $fseek(<file_desc>, <offset_value>, <operation_number>);

- integer: 定义整型变量,用于

$fseek的返回值。如果$fseek成功执行,返回0;$fseek执行失败,返回-1。 - file_desc: 为打开的文件句柄。

- offset_value: 相对于文件的参考指针,偏移的位置, 可以是正数,也可以是负数。

- operation_number: 定位文件指针的位置。 0,文件的起始位置;1,文件的当前位置; 2 文件结束的位置。

17. $fread的用法

integer <integer>;

<integer> = $fread(<store>,<file_desc>);

<integer> = $fread(<store>,<file_desc>, <start> );

<integer> = $fread(<store>,<file_desc>, <start>, <count> );

<integer> = $fread(<store>,<file_desc>, , <count> );

- integer: 定义整型变量,用于

$fread的返回值。如果$fread成功执行,返回0; $fread执行失败,返回-1。 - store: 将二进制文件中的数据读取到寄存器或者二维数组中。

- file_desc: 为打开的文件句柄

- start: 为二维数组的起始地址

- count: 从起始地址开始, 写入二维数组的数量。

例:

integer code;

reg [7:0] mem [4:0];

integer fd;

initial

begin

fd = $fopen("tinput.bmp", "r");

code = $fread(mem, fd); //表示从二进制文件中读取数据,依次存放到mem[0],mem[1],mem[2],mem[3]。

code = $fread(mem, fd,1); //表示从二进制文件中读取数据,依次存放到mem[1],mem[2],mem[3]。

code = $fread(mem, fd,1,2); //表示从二进制文件中读取数据,依次存放到mem[1],mem[2]。

code = $fread(mem, fd, ,3); //表示从二进制文件中读取数据,依次存放到mem[0],mem[1],mem[2]。

end

18. if条件表达式

reg[31:0] bus;

reg bus_is_active ;

always@(posedge clk or negedge rst_n) begin

if(bus) begin

bus_is_active <=1'b1;

end

else begin

bus_is_active <=1'b1;

end

end

针对上述代码,只要bus的值不为0,则bus_is_active 即为1。

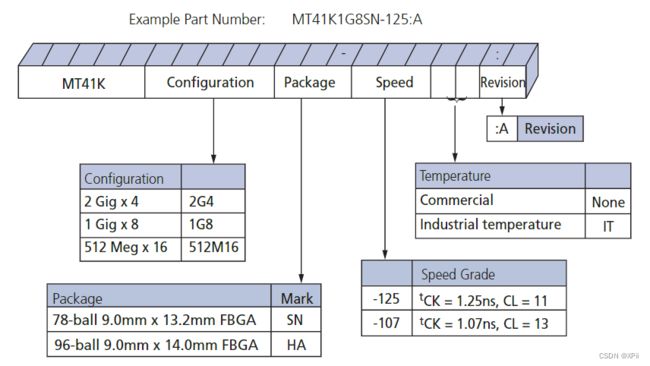

19. DDR芯片型号

MT41K512M16芯片在MIG IP核中没有型号,作为替代可以选择两块MT41K512M8作为替换,仅需在选择数据位宽时选择正确的数据位宽即可。即在MIG IP配置时选择DATA WIDTH=16即可。

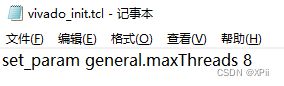

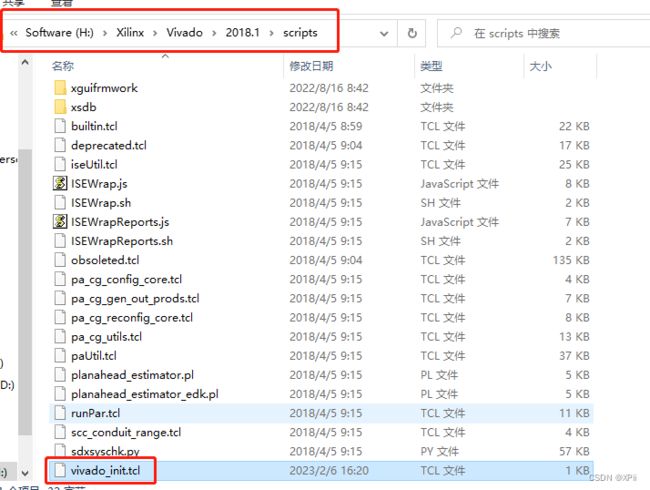

20. vivado中多线程编译设置

Windows下的Vivado默认线程数为2,Linux系统下的默认线程数为8。

可以通过以下tcl命令来获取当前的最大线程数:

get_param general.maxthreads

set_param general.maxthreads 8

该方法在重启Vivado后最大线程数都会回到默认的2个。可以通过以下方式解决:

- 新建

vivado_init.tcl文件。 - 在

vivado_init.tcl文件中输入以下命令,如下所示:

set_param general.maxThreads 8