数字逻辑 期末

概述

教材:《电子技术基础(数字部分)》 第六版

7400系列是TTL型芯片,商用型

数制

十进制->二进制 除2取余法&乘2取整法(注意精度,但计科简单不考)

十六进制->二进制 一位变四位

八进制->二进制 一位变三位

二进制加减

无符号加减

码

0不能省略

BCD码

8421 前10个

2421 前5+后5

5421 前5+8~12

余三码 8421+3

余三循环码 余三码异或

格雷码

表示0-15 余三循环码前加三个后加三个

前加0000 0001 0011 后加1011 1001 1000

ASCII码

逻辑运算

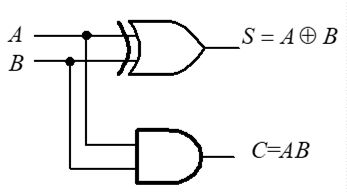

与 或 非 与非 或非 异或 同或

奇数个1异或是1

奇数个0同或是1

表达式 真值表 电路图 卡诺图 波形图

交换律 结合律 分配律 反演律

吸收律A+AB=A A+A非B=A+B (A+B)(A+C)=A+BC

常用恒等式 AB+A非C+BC=AB+A非C

代入规则

反演规则 变量取反 +x 10

对偶规则 +x 10

与或式二次取非得与非-与非式 继续化简+二次取非得或非-或非式

最简与或式

标准与或式 最小项

卡诺图 逻辑相邻 1、2、4、8包围圈 无关项x 可以正难则反

组合逻辑电路

编码器Encoder CD4532

输入高电平有效,输出低电平有效

EI是使能端,GS/EO是干啥的

2片CD4532 级联形成16-4线优先编码器

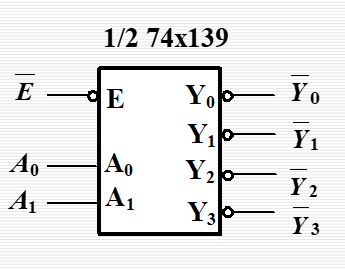

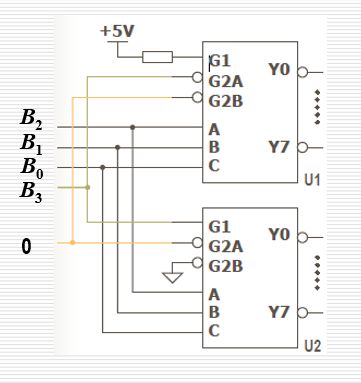

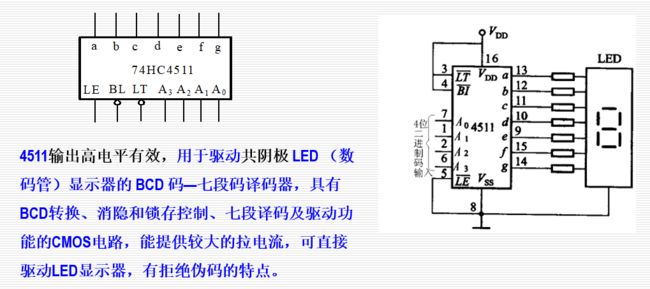

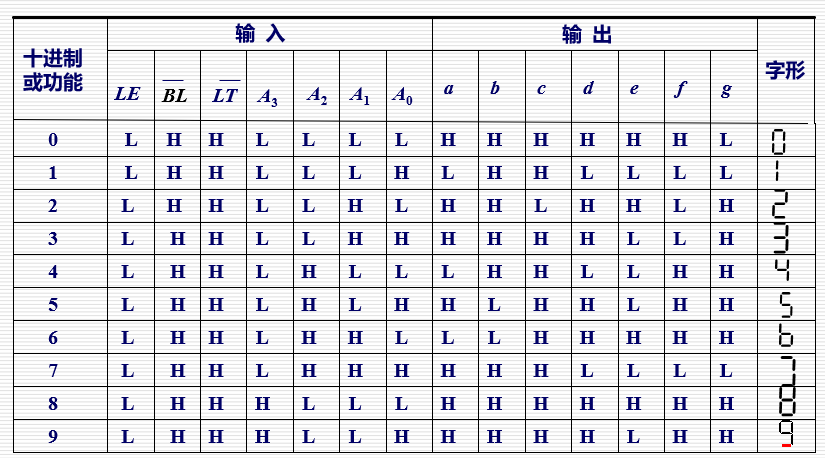

译码器 74138/139/4511

用译码器实现逻辑函数:最小项

二-十进制译码器 7442 唯一地址译码器

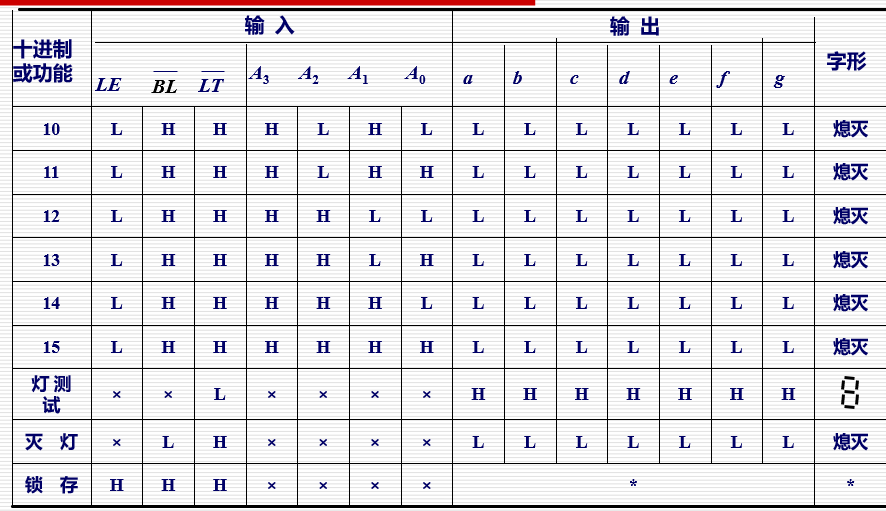

七段显示译码器 CMOS 74HC4511 数码管

共阴极输入高电平有效,输出高电平

共阳极输入低电平有效

LT非有效是灯测试 LIGHT

BL有效是灭灯

LE有效是锁存

有几道题可以看看

7447 七段字形译码器 输出低电平有效

7448 七段字形译码器 输出高电平有效

7449 BCD-七段译码器

数据选择器 74151

产生逻辑函数 最小项 变量>n要选一个出来接到相应输入端子D上

两片151组成二位八选一数字选择器(位扩展)或16选1数据选择器(字扩展)

并行数据->串行数据

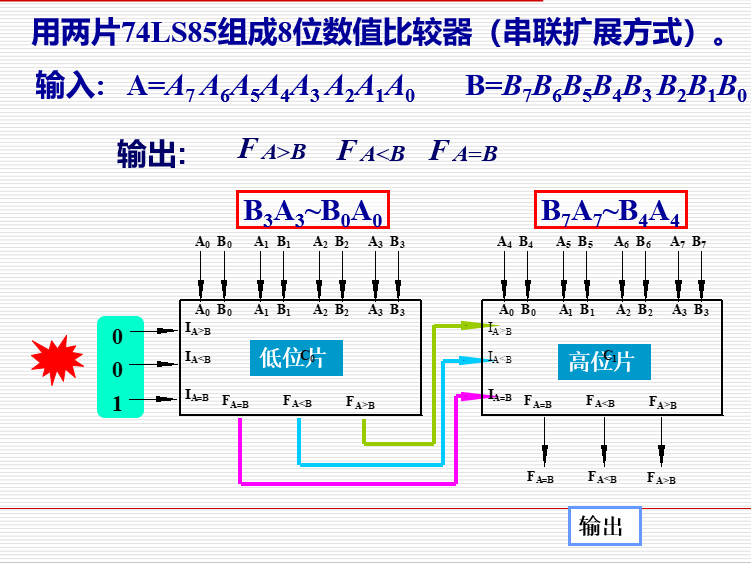

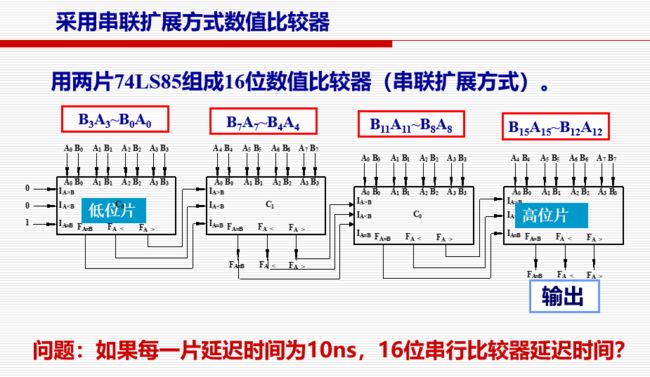

数值比较器 7485

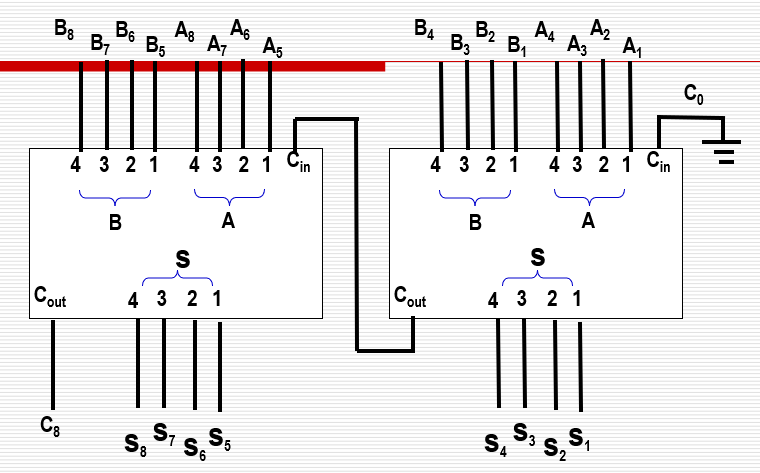

算数运算电路

时序逻辑电路

同步 异步

输出Y看的是现态不是次态

逻辑方程组 真值表 状态表 状态图 时序图

这块题比较多可以看看ppt

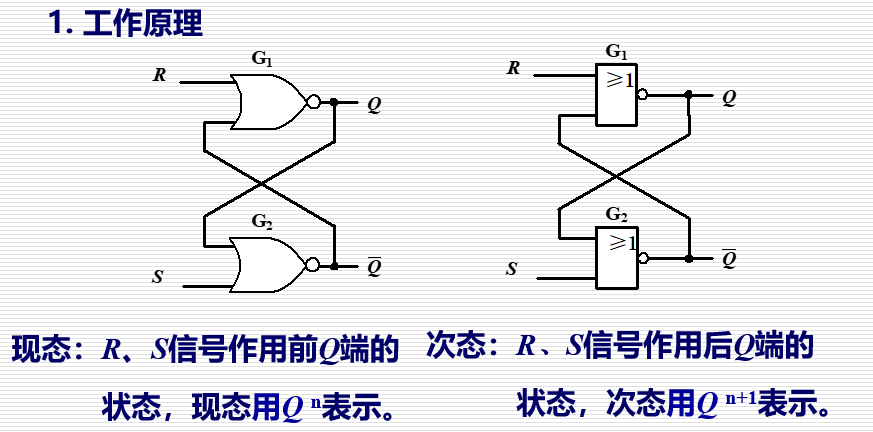

双稳态电路

锁存器 电平敏感 后来才出现

SR锁存器 与非 或非 门控

或非门RS 00保持 01Set置数1 10Reset清零0 11不定 约束条件SR=0

与非门 输入低电平有效 约束条件S非+R非=1

门控SR锁存器 加一个使能端

D锁存器

触发器 边沿敏感 比较多

SR触发器 与非 或非 逻辑门控

和SR锁存器一致

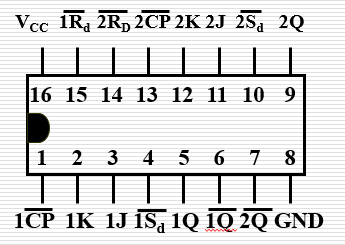

JK触发器

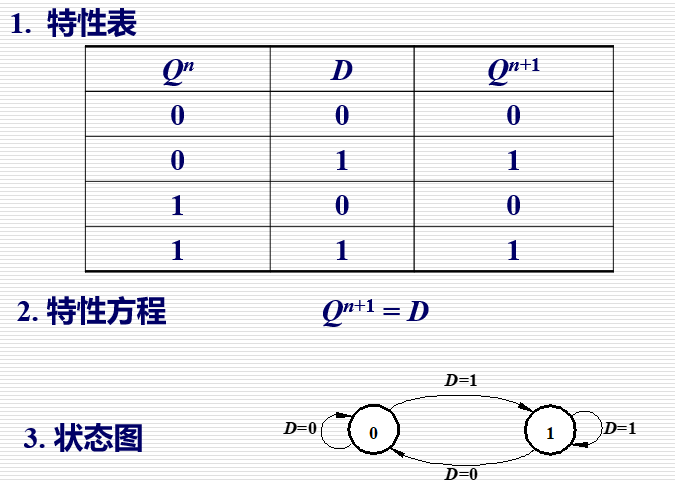

D触发器

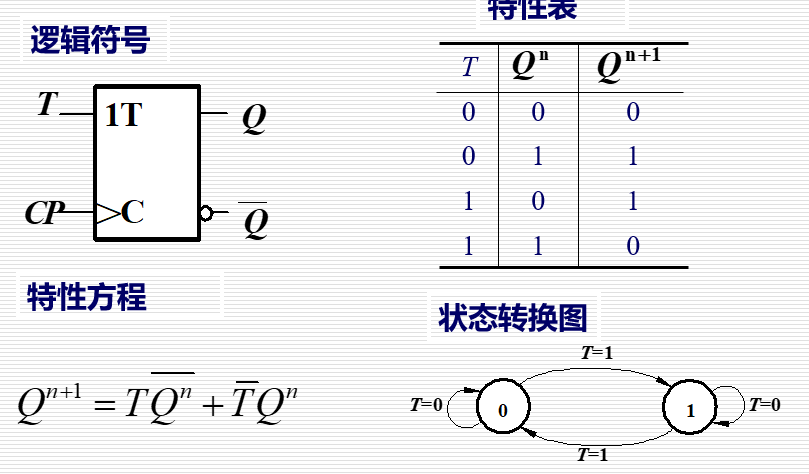

T触发器

T’触发器

翻转

逻辑功能的转换

寄存器

移位寄存器 左移 右移 双向 只能用边沿敏感的触发器

基本移位寄存器由D触发器构成,高低位和数字高低相同

74x194 4位双向移位寄存器 CMOS

S1S0 00保持 01右移 10左移 11置数

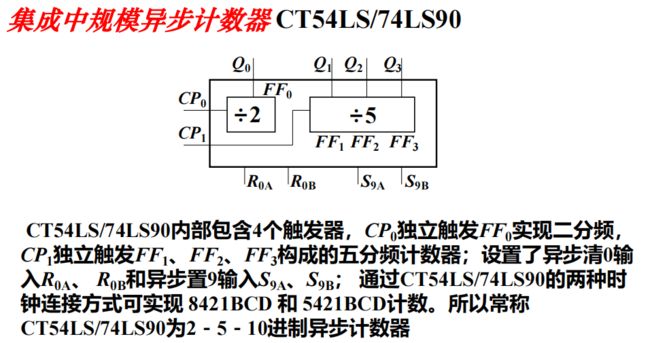

计数器

模:有效状态总数

异步清零 同步置数

4位异步二进制加法计数器

4位同步二进制加法计数器74161

CET、CEP为计数使能,并行进位TC=Q3Q2Q1Q0·CET

74x161 4位二进制计数器

环形计数器

扭环形计数器=约翰逊计数器

实现任意模值计数器

减小模:反馈清零法 反馈置数法

扩展: