XDMA IP学习

参考:xilinx xdma ipcore官方手册 PG195

一 XDMA IP概述

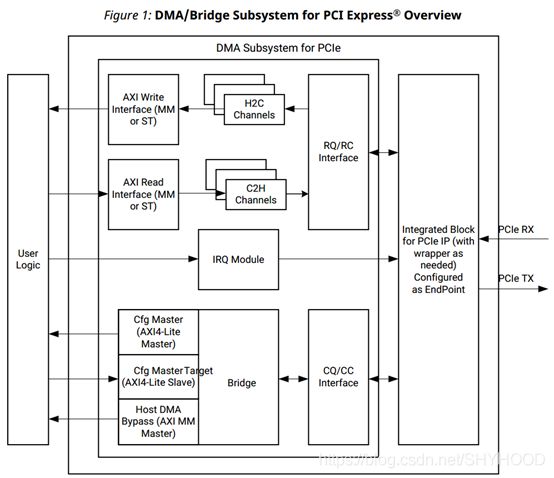

Xilinx® DMA/Bridge Subsystem for PCI Express® (PCIe®)(XDMA)是Xilinx公司2017年前后新推出的PCIe FPGA解决方案。功能上涵盖了PCIe ip核、SGDMA功能、多通道分离,同时支持AXI总线访问等。

XDMA支持UltraScale+、UltraScale和Virtex7 XT Gen3 (Endpoint),以及7系列(7A15T和7A25T除外)2.1(Endpoint)。最高支持4对Host-to-Card (H2C)和Card-to-Host (C2H)数据通道。

XDMA IP能配置为两种模式。一种为DMA Data Mover,另一种为PCIe bridge,PCIe bridge只支持Ultra Scale+系列。一般用XDMA都是做DMA Data Mover模式,后面只整理DMA Data Mover模式的内容。

二 XDMA IP结构

2.1 PCIe ip核

XDMA内部集成了PCIe的IP核,用于处理PCIe协议相关。PCIe core将PCIe接口组织为四个独立的AXIS的接口:

PCIe Requester Request(RQ)接口,用户应用程序通过该接口生成对连接到该链路的远程PCIe设备的请求。

PCIe Requester Completion(RC)接口,PCIe core将从链路接收的完成消息(响应于作为PCIe请求者的用户应用程序请求)返回给用户应用程序。

PCIe Completer Request(CQ)接口,PCIe core将来自链路的请求传递到用户应用程序。

PCIe Completer Completion(CC)接口,用户应用程序通过该接口将对CQ接口请求的响应发送回去。

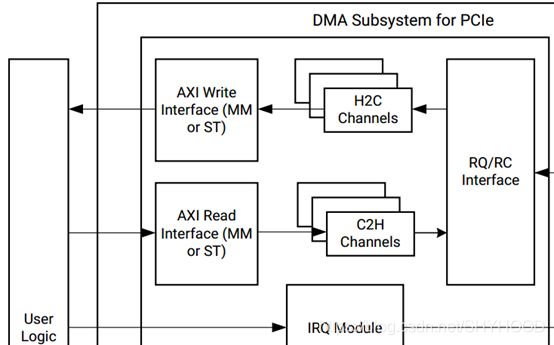

2.2通道接口

2.2.1 DMA数据通道

XDMA IP的DMA数据通道包含Host-to-Card (H2C)和Card-to-Host (C2H)两类,每类最高分别支持4通道。这些DMA通道可以被映射为独立AXI4-Stream接口或者是共享的AXI4-MM接口。(两者只能2选1):

AXI Memory Mapped:AXI内存映射的接口,常见用于对接DDR、RAM等有地址寻址的外设。

AXI Stream:AXI数据流接口,常用于对接FIFO等。

2.2.2 寄存器通道

The AXI4-Lite Master Configuration port:实现PCIE BAR地址到 AXI4-Lite寄存器地址的映射,可用来读写用户逻辑寄存器

The AXI4-Lite Slave Configuration port:用户可通过此接口访问XDMA IP的PCIe集成模块的相关寄存器

The AXI Memory Mapped Master CQ Bypass port: 用来实现PCIE 直通用户逻辑访问,可用于低延迟数据传输

注:AXI4-Lite Master Configuration port这个接口的数据输出是经过XDMA内部过滤的,也就是说这个接口出来的地址并不是所有的都能给用户使用,有部分地址是用来对XDMA的寄存器配置使用的,容易造成用户地址和配置地址混合,使用时需要注意。如果是对用户侧寄存器的大量访问最好使用The AXI Memory Mapped Master CQ Bypass port。

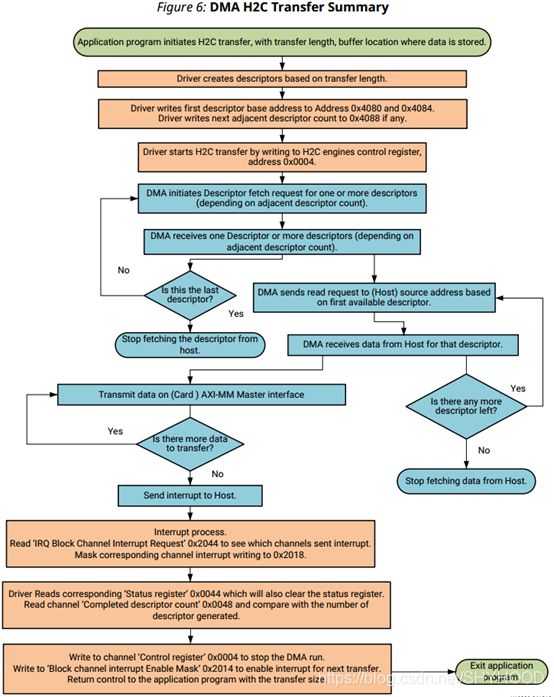

2.3 DMA

XDMA采用SGDMA。采用了一系列的descriptors,这些descriptors组成了一个链接列表。它们用来指明DMA transfers的源地址、目的地址以及DMA transfer的长度。他们由驱动程序产生。并且存储在host 内存中。DMA中的控制器会发起抓取descriptor lists来完成初始化并开始执行DMA操作。描述符的结构如下:

每个DMA通道都会有自己的descriptors列表。DMA读取到一个descriptor之后会提取其中Src_addr与Dst_addr,然后根据这些地址来完成memory transfer。完成当前descriptor对应的transfer之后。DMA 通道会根据当前descriptor的Nxt_addr来抓取下一个descriptor。而且descriptor中的Nxt_adj记录了列表中还剩下未完成的descriptor的个数。一旦为0,那么当前descriptor的control字段中的STOP位会置高。DMA就会停止抓取descriptor。

C2H和H2C的DMA传输流程如下图所示,其中绿色为应用层,橙色为驱动层,蓝色为硬件。

2.3中断

XDMA的IRQ模块能接受用户的外部中断和DMA通道的内部中断进而通过PCIe向链路产生中断。XDMA支持MSI-X,MSI和Legacy Interrupts(传统中断)。注:Host能使能一种或多种中断类型,当多个中断使能时,IP在一定时间内只能产生一种中断,其中MSI-X中断的优先级高于MSI,MSI优先级高于Legacy Interrupts,当一个类型中断产生或者挂起时,软件无法进行类型切换。下面分别介绍三种类型的中断:

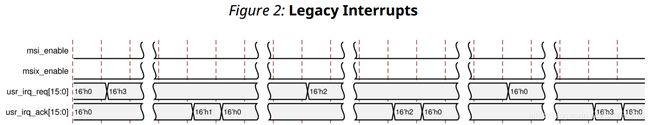

(1)Legacy Interrupts

对于Legacy Interrupts中断,当user_irq_ack 第一次为1的时候,代表中断已经被PCIe发送,之后才可以将usr_irq_req清0,当user_irq_ack 第二次为1的时候,可以重新设置usr_irq_req发起中断。

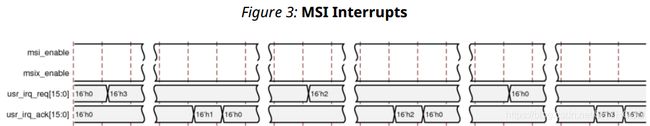

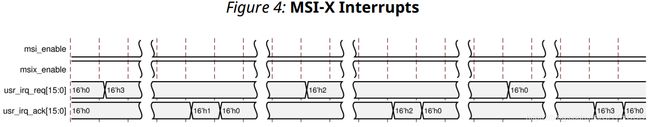

(2)MSI和MSI-X

MSI中断和MSI-X都是往配置的CPU中断寄存器里进行memory写操作,来产生中断,效率比INTx是共享式高,其中MSI最多支持32个中断向量,而且要求中断向量连续;而MSI-X中断机制可以支持更多的中断请求,而且不要求中断向量连续。

usr_irq_req 置位之后要一直保持到user_irq_ack置位且中断被Host处理。user_irq_ack 为置位只是说明中断已经被主机接收了,但是不代表已经处理。可以通过延迟usr_irq_req足够长的时间,确保中断能被响应,或者通过软件或者驱动层去清零usr_irq_req,比如通过AXI-LITE接口下发命令清除usr_irq_req。

注:当MSI和MSI-X同时使能时,产生为MSI-X

注2:关于XDMA的MSI-X的usr_irq_reg的清楚时机,xdma手册上不同版本描述不同,V4.1与V3.1与本文相同,V4.0中认为usr_irq_ack置位之后就可以清除usr_irq_reg。此块待验证。

2.4 寄存器空间

2.4.1 BAR

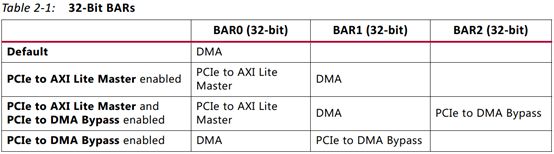

是否使能The AXI4-Lite Master Configuration port和The AXI Memory Mapped Master CQ Bypass port会导致不同的BARs分配。如下表:

2.4.2 BAR对应的寄存器

参考PG195

三 XDMA IP核配置

本次使用xilinx官方开发板KCU116(FPGA为KU5P)做相关实验,生成AXI-MM官方例程,对应IP核配置如下。

3.1 Basic

Functional mode:功能模式,选择DMA模式。

Mode:配置模式,选择Advanced高级配置。

Lane Width:根据硬件选择X8

Max Link Speed: 选择 8.0GT/s 即GEN3

Reference Clock:例程使用PCIe插槽传过来参考时钟,100MHz。

GT Quad:根据硬件选择GTY Quad 225(硬件上x8占用了Quad 224和225,选择PCIe Lan0的Quad 225)

DMA Interface Option:接口选择AXI-MM

AXI Data Width:选择默认256bit

AXI Clock Frequency:选择默认250M

AXI-Lite Slave Interface:用于选通AXI4-Lite Slave Configuration port通道。

3.2 PCIe ID

板子只有一个PCIe,这页选择默认配置

3.3 PCIe BARs

PCIE to AXI Lite Master Interface:使用AXI-Lite接口

PCIE to DMA Bypass Interface:这个接口不经过DMA直接访问用户逻辑,使用AXI-MM接口

PCIE to AXI Translation: 这个设置比较重要,通常情况下,主机侧PCIE BAR地址与用户逻辑侧地址是不一样的,这个设置就是进行BAR地址到AXI地址的转换,比如主机一侧BAR地址为0,IP里面转换设置为0x80000000,则主机访问BAR地址0转换到AXI Lite 总线地址就是0x80000000

3.4 PCIe MISC

选择对应的中断请求数,中断类型以及对应的中断向量数。通常linux只支持一个MSI的中断向量。

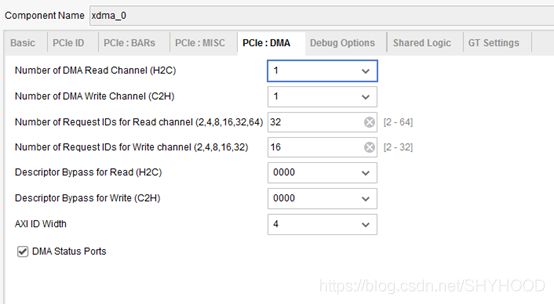

3.5 PCIe DMA

设置所需的Number of DMA Read Channel(H2C)和Number of DMA Write Channel(C2H)

Number of Request IDs for Read(Write)channel :这个是每个通道设置允许最大的outstanding数量,按照默认即可。

后续XDMA学习笔记:

XDMA IP学习2——细节补充+问题记录![]() https://blog.csdn.net/SHYHOOD/article/details/124486038?spm=1001.2014.3001.5502

https://blog.csdn.net/SHYHOOD/article/details/124486038?spm=1001.2014.3001.5502