行业观察 | 内存接口芯片和CXL协议

本文对内存接口芯片的概念和CXL协议进行不完全总结。

更新:2022 / 02 / 25

行业观察 | 内存接口芯片

- 背景

- 内存接口芯片

-

- 概念

- 趋势

-

- CXL 协议

背景

DRAM 内存基本被国外巨头 三星、美光 等内存模组制造商垄断,合计市场占有率超过 90%。

内存接口芯片

概念

什么是 内存接口芯片 ?

CPU 负责计算(侧重数据处理的高速度),内存负责存储数据(侧重数据的存取速度和稳定性),而 内存接口芯片 是 CPU 存取内存( DRAM )数据的必由通路,可以提高内存数据访问速度和稳定性,实现数据缓冲的功能。

内存接口芯片 的诞生,是为了解决服务器 CPU 的高处理速度与内存存储速度不匹配的问题( CPU 比内存处理数据的速度快,不加缓冲的内存条无法满足服务器 CPU 的运行速度、信号完整性和稳定性方面的要求,因此需额外添加接口芯片来提升内存性能)。

内存接口芯片 需与内存厂商生产的各种内存颗粒和内存模组进行配套,并通过服务器 CPU、内存和 OEM 厂商针对其功能和性能(如稳定性、运行速度和功耗等)的全方位严格认证,才能进入大规模商用阶段。

DDR5内存模组包括三颗配套芯片(SPD、TS和PMIC)。

DDR( Double Date Rate ),指的是内存的双倍速率。DDRx 表示不同内存技术时代,而内存从 DDR1 → DDR2 → DDR3 → DDR4 → DDR5 的技术迭代,可以简单理解成为内存的摩尔定律。

从 DDR 到 DDR5 每次迭代,电源电压值越来越低,数据传输速率呈几何倍数增长。

从上图可以看出 DDR 技术平均每 5 年迭代一次,而 CPU 的摩尔定律是 18 个月性能翻一倍,2003 年,随着内存 DDR2 产品发行,内存性能已经明显制约了 CPU 的速度,CPU 不得不长时间处在一种等待状态。

由此,IDT、英特尔等相继推出与之匹配的内存接口芯片( Memory Buffer、简称 MB ),其读写速度比内存更快,当 CPU 向内存中写入或读取数据时,CPU 可以直接从中提取,从而实现数据吞吐量的提升。

趋势

随着云计算、人工智能、高性能计算等技术的发展,处理器的算力不断地在提高,处理器的核心数也越来越多,这也推动了对内存大容量、高带宽的需求。

过去几年来,平均分配到每个计算核心的内存容量在不断增加,从早期的 3、4 GB每个核心,到 4 - 6 GB每个核心。2021年,每个计算核心上面平均要分配 8 - 10 GB的内存容量。

从带宽来看,虽然整机的内存总带宽是在不断提升,但是相对于核心数来说,每个核心上面的内存带宽提升并不明显。

从内存成本发展的趋势来看,过去十几二十年来,随着 DDR 内存的发展,单位内存的成本在不断下降。但近几年来,下降的趋势变得更平缓了。

很重要的原因在于,由于内存的基本单元之一是电容,而电容的尺寸在目前情况下很难再进一步缩小,这制约了内存制程的进一步提升,随着内存容量不断提升,内存条的成本就会上升。

一方面需要更大容量的内存,一方面又需要高带宽的内存访问能力,如何增加内存的带宽和容量呢?

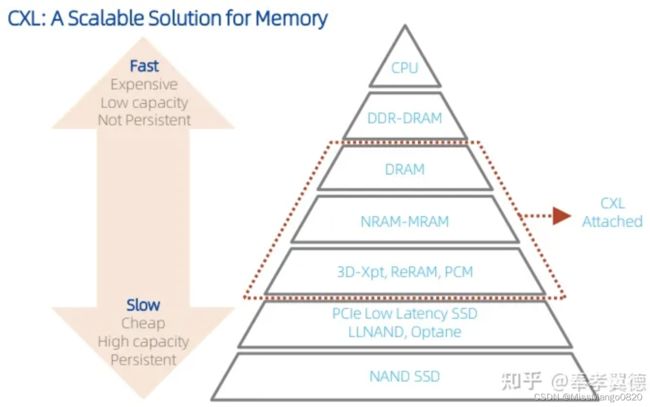

以往的做法中,就是在处理器当中增加内存通道,从上图可见,处理器支持的内存的通道数,从早期的 3 通道、4 通道,发展到了现在的 6 个内存通道、8 个内存通道,将来的处理器还会支持 12 个内存通道。然而,处理器支持的内存通道不可能无限地增加下去。因为,每增加一个 DDR 内存通道,都要增加很多信号,随着通道数的增加,处理器要处理的信号数量会越来越多,这对于处理器的封装设计,以及主板的 PCB 设计来说,都是很大的挑战。另外,随着内存控制器越来越多,也会对处理器的功耗和散热设计带来很多的问题。从经济性的角度来看,现有的 DDR 内存延时低,但是成本较高,市场上出现了一些新的存储介质,虽然延迟比较大,性能比较差,但是成本很低。如果系统能够支持不同的存储层级,意味着成本上面可进行一些优化。

但是,目前处理器主流的 DDR 接口无法兼容多种存储介质,虽然处理器可以通过 PCIe 接口来支持其他的存储介质,但无法在系统的角度保持不同存储介质间的缓存一致性,数据传输的效率无法进一步提升。

CXL 协议的出现,为解决内存系统存在的诸多问题提供了一个很好的解决方案。

CXL 协议

CXL 是一个开放的工业标准,由英特尔首先提出,业界许多领先的企业,包括处理器厂商,内存厂商,芯片设计厂商,以及 OEM、CSP 的厂商,都加入到了这个联盟当中。CXL 协议在物理侧上沿用了 PCIe Gen5 的规范,这也为高带宽提供了很好的基础。在物理层之上,它定义了三种不同的协议,根据支持的协议数量的不同,可以把 CXL 设备大致分成三个类型。今天我们主要看第三种设备类型,也就是 CXL 的内存扩展。设备三的类型,主要是支持CXL.mem 协议,主机的处理器通过这个协议,把这个内存读写的请求,发送到 CXL 的控制器,CXL 控制器再把这些请求转给后面的内存控制器,并完成相应的指令。通过 CXL 串行接口,处理器可以利用相对较少的信号数量来扩充内存的带宽和容量。同时,CXL 控制器来解耦了处理器对存储介质的依赖,使得不同的存储介质都可以通过各自的 CXL 控制器连到同一个处理器上。于是,从系统的视角来看,这就形成了可统一管理的、具有不同特性的存储空间。

CXL 内存模组是使用 CXL 作为内存互连技术的内存模组,它摆脱了传统 DDR 模组的限制。

它可以把不同的成本,不同性能的存储介质,通过 CXL 的接口连接到系统当中。

在一个服务器的节点当中,MXC 芯片可以以不同的模组形态,进行内存的带宽和容量扩展,满足一些高内存带宽的业务需求。也可以在新平台中,继续使用 DDR4 的内存条,来降低内存的成本。随着将来 CXL 2.0 平台的推出以及 Switch 交换机的推出,多个 CXL 的模组还可以组成一个内存池,通过 Switch 交换机连接到多个服务器节点,灵活地满足各台服务器对内存的需求。

内存池化应用的价值

在 CXL 技术出现之前,内存和处理器是紧耦合的,内存都部署在服务器节点内。

内存成本是占整个服务器成本的比例很高,但是在实际使用中,内存的使用效率并不高,有的内存空间根本没有被访问,有的内存空间则存放了一些比较冷的数据,它访问的频率其实很低。这部分的内存没能很好地发挥它的价值,如果用 CXL 来做池化,这意味着单节点服务器可以部署较少的内存,大部分的内存可以从服务器当中解耦出来,通过 CXL 技术,形成一个内存池,连接到多个服务器上。在使用中,通过 Switch 将内存动态地分配到有需要的服务器上,从而可以大大提高内存的使用效率,使得数据中心用较低的内存成本,能够满足实际业务的需求。