【STM32学习】——SPI通信协议&SPI时序&W25Q64存储芯片&软件SPI读写

目录

前言

一、SPI通信协议

1.概述

2.硬件电路

3.移位示意图

二、SPI时序

1.时序基本单元

2.完整时序波形

三、W25Q64存储芯片

1.芯片简介

2.硬件电路&引脚定义

3.芯片框图

4.Flash操作注意事项

四、软件SPI读写W25Q64

五、SPI通信外设

总结

前言

声明:学习笔记来自江科大自化协B站教程,仅供学习交流!!

对于SPI通信的学习和I2C一样,分为软件模拟实现和硬件配置实现读写W25Q64 Flash存储器!

SPI传输数据的速度更快,协议没有严格规定最大传输速度,取决于芯片厂商需求;SPI的设计比较简单粗暴,实现的功能没有I2C多,比较简单;SPI硬件开销比较大,通信线的个数较多,且通信过程经常有资源浪费的现象——“富家子弟,有钱任性”,只在乎任务快速完成!

一、SPI通信协议

1.概述

①SPI(Serial Peripheral Interface串行外设接口)是由Motorola公司开发的一种通用数据总线。

②四根通信线:SCK(Serial Clock)、MOSI(Master Output Slave Input)、MISO(Master Input Slave Output)、SS(Slave Select)。同步、全双工

③支持挂载多设备(一主多从)。有几个从机就有几个SS线,指定从机十分方便,给对应线触发电平就行。从机上引脚常写DO或DI,分别接主机的MISO和MOSI。

2.硬件电路

①所有SPI设备的SCK、MOSI、MISO分别连在一起;

②主机另外引出多条SS控制线,分别接到各从机的SS引脚。同一时刻只可选择一个从机。

③输出引脚配置为推挽输出,输入引脚配置为浮空或上拉输入。推挽输出高低电平均有很强的驱动能力,这将使得SPI引脚信号的下降沿非常迅速,上升沿也非常迅速(不像I2C那样,下降沿迅速,上升沿缓慢),信号变化快,可达到更高传输速度(MHz级别)。I2C并不是不想使用这个推挽输出,而是因为I2C要实现半双工,经常要切换输入输出,而且要实现多主机的时钟同步和总线仲裁,这些功能都不允许I2C使用推挽输出,要不然一不小心就会电源短路,他选择了更多的功能自然就要放弃更强的性能。SPI也有个冲突点,如图的MISO引脚,主机一个输入接了从机三个输出,如果三个从机都是始终时推挽输出,势必造成冲突,所以在SPI协议里有条规定:当从机的SS引脚为高电平(未被选中时),这个从机的MISO引脚必须切换为高阻态(相当于引脚断开,不输出任何电平),在从机SS为低电平时,MISO引脚才允许为推挽输出。

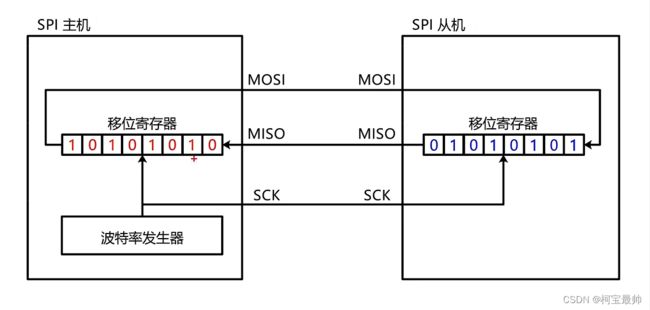

3.移位示意图

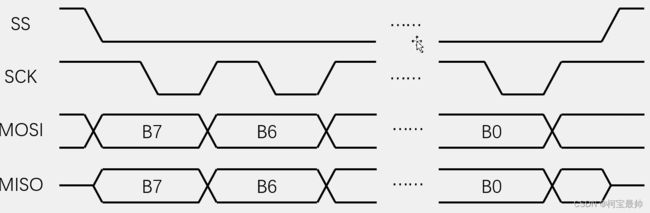

移位示意图是SPI硬件电路设计的核心

主机和从机的移位寄存器都有一个时钟输入端(SCK箭头),SPI一般都是高位先行,所以每来一个时钟移位寄存器都会向左进行移位,主和从同理。移位寄存器的时钟源是由主机提供,这里叫作波特率发生器,它产生的时钟驱动主机的移位寄存器进行移位,同时也通过SCK引脚输出到从机的移位寄存器。

电路工作流程:首先规定时钟的上升沿,所有移位寄存器向左移动一位,移出去的位放到引脚上(通信线上,实际是输出数据寄存器);时钟的下降沿,引脚上的位采样输入到移位寄存器的最低位。假设主机有个数据10101010要发送到从机,同时从机有个数据01010101要发送到主机...“转圈圈”如图,八个时钟后就会实现。SPI收发都是基于字节交换,当主机同时需要发送一个字节,且同时要接收一个字节时,就可执行下字节交换的时序。如果只想发送不想接收?仍然采用交换字节的时序,发送与接收同时进行,只不过接收的数据(一般统一发0x00或0xFF)不看就行。

二、SPI时序

1.时序基本单元

①起始条件:SS从高电平切换为低电平。SS是从机选择线,低电平有效,一旦选择了从机通信就开始了。

②终止条件:SS从低电平切换为高电平。

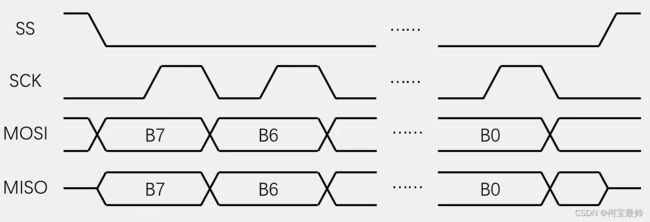

③交换一个字节

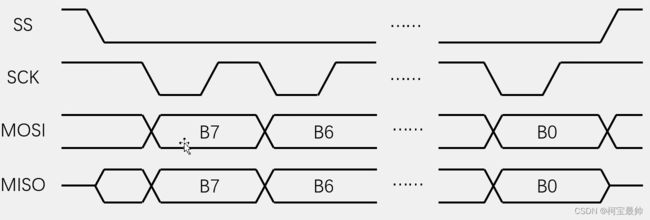

(模式0)

CPOL=0:空闲状态时,SCK为低电平

CPHA=0:SCK第一个边沿移入数据(奇数边沿进行数据采样),第二个边沿移出数据。但数据总要先移出再移入,所以在SCK第一个边沿之前,就要提前开始移动出数据了,如图几乎与SS下降沿开始信号同步,再SCK第一个上升沿之前。我们实操时按模式0!

(模式1)

CPOL=0:空闲状态时,SCK为低电平

CPHA=0:SCK第一个边沿移出数据,第二个边沿移入数据(偶数边沿进行数据采样)。先移出数据,再移入数据,比较符合常理,实际应用中模式1和模式0应用最多!

(模式2)

CPOL=1:空闲状态时,SCK为高电平

CPHA=0:SCK第一个边沿移入数据(奇数边沿进行数据采样),第二个边沿移出数据。

(模式3)

CPOL=1:空闲状态时,SCK为高电平

CPHA=0:SCK第一个边沿移出数据,第二个边沿移入数据(偶数边沿进行数据采样)。

模式0与模式2对比:CPOL相反,空闲状态电平不同,即SCK极性取反;剩下流程一致。

模式1与模式3对比:与上相同。

注意:CPHA表示时钟相位,决定的是第一个时钟采样移入还是第二个时钟采样移入,并不是规定上升沿采样还是下降沿采样。

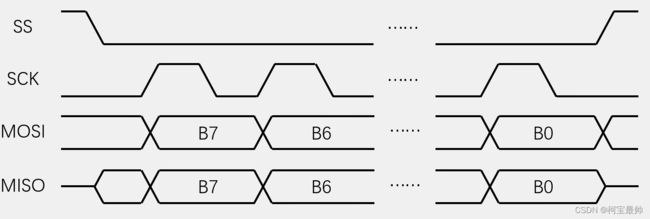

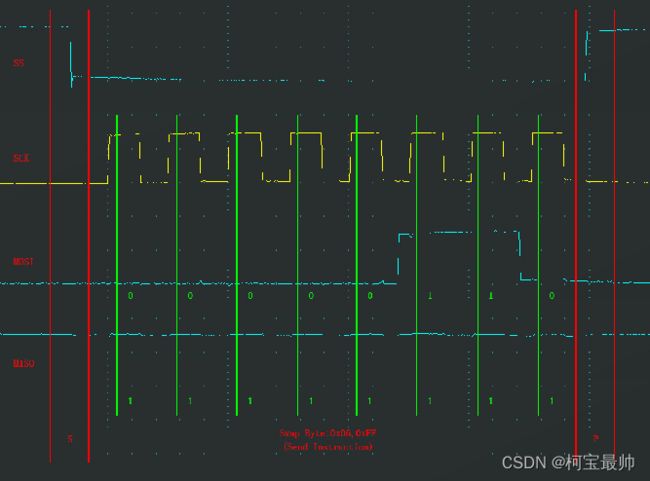

2.完整时序波形

当然每个芯片对SPI时序字节流功能的定义不同,这里以实操芯片W25Q64的时序为例进行讲解。SPI对字节流功能的规定不像I2C那样,I2C的规定一般是有效数据流第一个字节是寄存器地址,之后依次是读写的数据,使用的读写寄存器模型;

而在SPI中,通常采用的是指令码加读写数据的模型,过程就是SPI起始后,第一个交换发送给从机的数据,一般叫作指令码,在从机中对应会定义一个指令集,当我们需要发送什么指令时,就可以在起始后第一个字节发送指令集里面的数据,这样就能指导从机完成相应功能了,不同的指令可以有不同的指令个数,有的指令只需要一个指令码就可以完成,比如W25Q64的写使能、写失能等指令,而有的指令后面就需要再跟上要读写的数据,比如W25Q64的写数据、读数据等,写数据指令后面就要跟上在哪里写、要写什么,读数据同样。

下述图片可能不清,详见江科大教程!

发送指令:向SS指定设备,发送指令(0x06)

指定地址写:向SS指定的设备,发送写指令(0x02),随后在指定地址(Address[23:0])下,写入指定数据(Data)

指定地址读:向SS指定的设备,发送读指令(0x03),随后在指定地址(Address[23:0])下,读取从机数据(Data)

除了以上这些,还有其他时序,不过大同小异:都是起始、交换、交换、交换...、停止,只需要关注下每个字节的功能定义,就能很方便地利用SPI控制设备了。

三、W25Q64存储芯片

1.芯片简介

①W25Qxx系列是一种低成本、小型化、使用简单的非易失性存储器(掉电不丢失),常应用于数据存储、字库存储、固件程序存储等场景。存储器分为易失性存储器和非易失性存储器,前者包括SRAM、DRAM等,后者包括E2PROM、Flash等。

②存储介质:Nor Flash(闪存)。像STM32的程序存储器、U盘、电脑里的固态硬盘等都是Flash闪存,闪存分为Nor Flash和Nand Flash。

③时钟频率:80MHz、160MHz(Dual SPI双重SPI模式等效频率)、320MHz(Quad SPI四重)。双重和四重SPI了解下,本节未用!就是一个时钟发送或接收2位/4位,有点并行的意思!

④存储容量(24位地址):

- W25Q40: 4Mbit/512KByte(bit除以8换算为Byte)

- W25Q80: 8Mbit/1MByte

- W25Q16: 16Mbit/2MByte

- W25Q32: 32Mbit/4MByte

- W25Q64: 64Mbit/8MByte

- W25Q128: 128Mbit/16MByte

- W25Q256: 256Mbit/32MByte

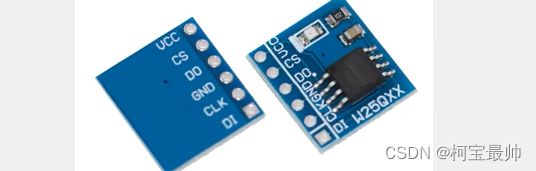

2.硬件电路&引脚定义

“/”和“—”的意思一样,低电平有效!

WP(Write Protect)写保护,低电平有效。配合内部的寄存器配置,可以实现硬件的写保护,低电平时保护住不让写。

HOLD数据保持,低电平有效,用的不多。如果在进行正常读写时,突然产生中断,然后想用SPI通信线去操控其他器件,这时如果把CS置回高电平,那时序就终止了,但又想在不终止总线时操作其他器件,这就可以HOLD引脚置低电平,这样芯片就HOLD住了——芯片释放总线,但是芯片时序也不会终止,它会记住当前的状态,当操作完其他器件时,可以再把HOLD置回高电平,然后继续HOLD之前的时序。

引脚图中括号里的IO0~IO3与上边说的双重和四重SPI有关,这里先不管!

电路原理图C1是电源滤波,R1和D1是一个电源指示灯,HOLD和WP都是低电平有效接到VC!

3.芯片框图

Flash空间划分:

一般一块存储空间可以先划分为若干的块block,其中每一块再划分为若干的扇区Sector,每个扇区内部又可分成很多页Page。

上图右侧大矩形空间里是所有存储器,存储器以字节为单位,每个字节都有唯一的地址,W25Q64的地址宽度是24位(3个字节),最大寻址范围是16MB,大矩形地址范围是000000h~7FFFFFh(8MB),地址空间只用了一半。以64KB为一个基本单元分成了128个Block,注意观察每一个Block里的地址规律xx0000~xxFFFFh。

左上角矩形就是还要再对每一块进行更细的划分,分为多个扇区Sector,如图虚线指向了各个Block,意思是每一块里面都是这个样子。在一个Block里再以4KB为一个单元切分成16个Sector,每一个Sector里地址变化规律xxx000~xxxFFFh。

Sector里继续分成若干Page,一个Page大小为256个字节,即一个Sector可分为16个Page,每一个Page里地址变化规律xxxx00~xxxxFFh。即页(Page)内的地址变化仅限于最低一个字节!

控制逻辑&状态寄存器:

左下角是SPI控制逻辑,即芯片内部进行地址锁存、数据读写等操作都可由其自动完成,就像整个芯片的管理员,需要操作什么告诉它就行了,它会自动操作内部电路完成功能!左侧为通信引脚。

控制上面有个状态寄存器(Status Register),芯片是否处于忙状态、是否写使能、是否写保护都可在此体现!

页缓存区:

256字节页缓存区(256-Byte Page Buffer),其实是一个256字节的RAM存储器,........。数据读写就是通过这个RAM缓存区进行的,写入数据会先放在RAM缓存区里,然后时序结束后芯片再将缓存区的数据复制到对应的Flash里,进行永久保存!为什么要这样?因为SPI写入的频率是非常高的,而Flash的写入由于需要掉电不丢失(留下刻骨铭心的变化)速度比较慢,而缓存区RAM速度非常快。但是因为缓存区只有256个字节,所以写入的一个时序,连续写入的数据量不能超过256字节。由于数据从缓存区转移到Flah存储器里需要一定时间,所以在写入时序结束后,芯片会进入一段忙的状态,如图有条线通往状态寄存器(Status Register),给其BUSY位置1,这时芯片不会响应新的读写时序。

其他:

写控制逻辑(Write Control Logic),和WP引脚相连,配合其完成硬件写保护。高压生成器(High Voltage Generators)是配合Flash进行编程的,要想实现Flash掉电不丢失就要在存储器里产生”刻骨铭心“的变化,一般需要高电压刺激。页地址锁存/计数器(Page Address Latch/Counter)和字节地址锁存/计数器(Byte Address Latch/Counter),这两个是用来指定地址的:STM32通过SPI总共发过来3个字节的地址,因为1个Page是256字节,所以一页内的字节地址取决于最低一个字节。发过来的高位2个字节(前2个)对应的就是页地址,它们会进入Page Address Latch/Counter,最后一个字节进入Byte Address Latch/Counter。

然后页地址通过写保护和行解码来选择我们要操作哪一页,字节地址通过列解码和256字节缓存来进行指定地址的读写操作。此地址指针在读写之后可以自动+1,这样就很容易实现从指定地址开始,连续读写多个字节的目的了。

4.Flash操作注意事项

为了保持Flash掉电不丢失、存储容量大、成本足够低的特性,它会在操作的便捷性等方面做出一些妥协和让步,所以有很多注意事项。RAM则不同,指哪写哪,想写多少就多少,且可覆盖写入,后续来的数据可直接覆盖原来的数据。

①写入操作时:

- 写入操作前必须先进行写使能

- 每个数据位只能由1改写为0,不能由0改写为1

- 写入数据前必须先擦除,擦除后所有数据位变为1。发出擦除指令后,芯片也会进入忙状态。

- 擦除必须按最小擦除单元进行。可选择整片芯片擦除、块擦除、扇区擦除,没有再小了。

- 连续写入多个字节时,最多写入一页的数据,超过页尾位置的数据会回到页首覆盖写入。在进行多字节写入时,地址范围不可跨越页的边沿,否则会地址错乱。

- 写入操作结束后,芯片会进入忙状态,不响应新的读写操作

②读取操作时:

- 直接调用读取时序,无需使能(1),无需额外操作(234),没有页的限制(5),读取操作结束后不会进入忙状态,但不能在忙状态下读取。

续下篇(实操):

四、软件SPI读写W25Q64

五、SPI通信外设

六、硬件SPI读写W25Q64

往期精彩:

STM32定时器输入捕获(IC)

STM32定时器输出比较(PWM波)

STM32定时中断

STM32外部中断

STM32GPIO精讲

…