- RISC-V架构生态及相关学习记录

我朝山海而去

risc-v学习

从网络整理,仅供自己学习_____________________________________________________________________________1.RISC-V架构的两个特性RISC-V,第五代精简指令处理器。RISC-V指令集,可以在理解上类比于主流商用Inter的x86,ARM的指令集,用于CPU读取、翻译从而指挥计算机进行相应操作。它在RISC(基于精简指令

- risc-v特权模式

狮子座硅农(Leo ICer)

risc-v

risc-v架构定义了3种工作模式,又称为特权模式(privilegedmode)。机器模式(machinemode),简称M模式;监督模式(supervisormode),简称S模式;用户模式(usermode),简称U模式。risc-v架构定义机器模式为必选模式,另外两种模式为可选模式,通过不同的模式组合可以实现不同的系统。risc-v架构支持几种不同的存储器地址管理机制,包括对物理地址和虚拟

- cs寄存器 x86 特权模式_我们一起学RISC-V——01-了解处理器和寄存器

黎贝卡

cs寄存器x86特权模式

本期内容如下:形象认识处理器RISC-V处理器面貌处理器都能做什么RISC-V核对外接口一、形象认识处理器1.1指令集分类处理器指令集分为两类,CISC(ComplexInstructionSetComputers,复杂指令集计算机)和RISC(ReducedInstructionSetComputers,精简指令集计算机)。CISC处理器,当以为美国Intel,AMD的X86处理器为代表,当然中

- 科技早报 | 5G-A在北京正式商用;苹果NFC芯片权限打开;阿里达摩院玄铁推出64位高实时能效RISC-V处理器设计R908 | 最新快讯

www3300300

人工智能microsoft

罗永浩披露“真还传2.0”:已还8.24亿罗永浩在微博发布长文,披露自己最新的债务进展情况。此前,他因谈论董宇辉与俞敏洪相关话题再度卷入舆论漩涡,发文是有意澄清期间产生的相关诽谤言论。据他所述,目前“真还传”一共还了8.24亿元,具体构成包括直播电商公司的税后现金收入、锤子科技的债务善后团队变卖资产、以及一笔由国有资本投资的6亿元债务。罗永浩表示,团队曾构想以资本化方式偿还这部分债务,但最终因交个

- 【RISC-V设计-12】- RISC-V处理器设计K0A之验证环境

kearn.chen

RISC-V设计专题risc-v

【RISC-V设计-12】-RISC-V处理器设计K0A之验证环境文章目录【RISC-V设计-12】-RISC-V处理器设计K0A之验证环境1.简介2.验证顶层3.顶层代码4.模型结构4.1地址映射4.2特殊功能寄存器5.模型代码6.运行脚本7.总结1.简介在前几篇文章中,分别介绍了各个模块的设计,本篇文章将会针对k0a_core_top层搭建一个简单的验证环境。2.验证顶层3.顶层代码//---

- CPU 指令集架构 复杂指令集架构(CISC)和精简指令集架构(RISC) ARM、MIPS、RISC-V和Alpha 指令集架构(Instruction Set Architecture,ISA)

EwenWanW

AGI架构arm开发risc-v

CPU指令集架构CPU指令集架构是计算机体系结构中与程序设计有关的重要部分。它定义了计算机如何执行和操作指令,是计算机执行程序的基础。指令集架构包括基本数据类型、指令集、寄存器、寻址模式、存储体系、中断、异常处理以及外部IO等多个方面。在CPU指令集架构中,主要有两种类型:复杂指令集架构(CISC)和精简指令集架构(RISC)。复杂指令集架构(CISC)的设计目标是尽可能将任务一次性完成,因此它的

- 【学一点RISC-V】RISC-V IMSIC

京雨

risc-v

IMSICRISC-VAIA文档第三章IncomingMSIController(IMSIC)传入MSI控制器(IMSIC)是一个可选的RISC-V硬件组件,与hart紧密相连,每个hart有一个IMSIC。IMSIC接收并记录Hart的传入消息信号中断(MSI),并在有待处理并使能的中断时向Hart发出信号。IMSIC在机器地址空间中有一个或多个内存映射寄存器,用于接收MSI。除了这些内存映射寄

- 睿赛德科技携手先楫共创RISC-V生态|RT-Thread EtherCAT主从站方案大放异彩

RT-Thread物联网操作系统

科技risc-v人工智能物联网大数据

日前,在先楫HPM6E00技术日上,睿赛德科技(RT-Thread)向广大工业用户展示了多年来双方在RISC-V生态领域的合作历程和成果,同时睿赛德科技携手先楫半导体首次推出了基于HPM6800处理器的EtherCAT主站解决方案,吸引了现场大量工业用户的关注。该方案不仅展示了卓越的性能和可靠性,还体现了双方在嵌入式系统领域的深入合作和技术领先优势。目前先楫半导体所有开发板已上RT-Thread主

- 【RISC-V设计-13】- RISC-V处理器设计K0A之指令测试

kearn.chen

RISC-V设计专题risc-v

【RISC-V设计-13】-RISC-V处理器设计K0A之指令测试文章目录【RISC-V设计-13】-RISC-V处理器设计K0A之指令测试1.简介2.验证用例3.指令代码4.链接脚本5.编译脚本6.仿真结果6.1复位结束6.2运行成功6.3终端打印7.总结1.简介借助上一篇文章所提及的验证环境,在本篇文章中,将会阐述如何增添一个用例来验证指令集,以及怎样运用编译器编译汇编代码,并生成二进制的Bi

- 【RISC-V设计-08】- RISC-V处理器设计K0A之BMU

kearn.chen

RISC-V设计专题risc-v

【RISC-V设计-08】-RISC-V处理器设计K0A之BMU文章目录【RISC-V设计-08】-RISC-V处理器设计K0A之BMU1.简介2.顶层设计3.端口说明4.总线时序4.1总线写时序4.2总线读时序5.代码设计6.总结1.简介总线管理单元(BusManagementUnit,简称BMU)是CPU中负责取指以及数据加载与存储的模块。其主要涵盖两个功能:其一为指令获取,当CPU开始运行,

- 一键教会OpenHarmony-4.1-Release的small系统的rootfs制作过程

wenfei11471

itopen组织1、提供OpenHarmony优雅实用的小工具2、手把手适配riscv+qemu+linux的三方库移植3、未来计划riscv+qemu+ohos的三方库移植+小程序开发4、一切拥抱开源,拥抱国产化一、rootfs制作命令small系统的rootfs制作脚本为build/ohos/packages/fs_process.py,制作的命令为build/ohos/packages/fs

- RISC-V汇编实现矩阵阶乘

wave_sky

risc-v汇编

1)源代码longlongfact(longlongn){if(n=0,gotoL1addix10,x0,1//return1addisp,sp,16//pop2itemsoffstackjalrx0,0(x1)//returntocallerL1:addix10,x10,-1//n>=1:argumentgets(n-1)jalx1,fact//callfactwith(n-1)ldx6,0(s

- 阿里平头哥“急速”发布玄铁910为哪般?

何玺

从中天微和达摩院合并成立平头哥算起,时间尚不足一年。7月25日,阿里巴巴旗下半导体公司平头哥对外发布玄铁910(XuanTie910),一款号称目前业界性能最强的一款RISC-V处理器。平头哥这个速度,真的有点“急”。关于平头哥“玄铁910”在阿里内部的命名体系中,武侠小说是主要的灵感来源。据悉,玄铁二字,来自于金庸小说中杨过的神剑。显然,阿里方面是希望这款处理器,能够拥有玄铁神剑那样的神器。在阿

- 大大通与您相约 elexcon 2024 深圳国际电子展

WPG大大通

展会人工智能大大通展会ai礼品电子展

“内核创新,智驱未来”,2024elexcon深圳国际电子展将于2024年8月27日至29日在深圳会展中心(福田展馆)盛大开幕。全球优质品牌厂商将齐聚现场。集中展示AI+嵌入式、存储、车规级芯片、智能传感、RISC-V技术与生态、AIoT方案、无源器件/分立器件、PMIC与功率器件、Chiplet和SiP先进封装等;展会期间还将举办一系列技术论坛,展示全球产业动态及未来技术趋势。作为大联大特别推出

- 【RISC-V 指令集】RISC-V 向量V扩展指令集介绍(八)- 向量整数算术指令

瑶光守护者

RISC-V指令集分析risc-v人工智能机器学习

1.引言以下是《riscv-v-spec-1.0.pdf》文档的关键内容:这是一份关于向量扩展的详细技术文档,内容覆盖了向量指令集的多个关键方面,如向量寄存器状态映射、向量指令格式、向量加载和存储操作、向量内存对齐约束、向量内存一致性模型、向量算术指令格式、向量整数和浮点算术指令、向量归约操作、向量掩码指令、向量置换指令、异常处理以及标准向量扩展等。首先,文档定义了向量元素和向量寄存器状态之间的映

- Openpiton RISC-V处理器学习笔记(2 仿真测试)

一层小笼包

risc-v学习fpga开发linux

一、克隆Openpiton工程选择合适文件夹(不含中文路径)克隆Openpiton开源工程注:由于GitHub不稳定,需要多尝试几次。sumkdiropenpiton&&cdopenpitongitclonehttps://github.com/PrincetonUniversity/openpiton.git#国内源(gitclonehttps://gitee.com/dong9991010/o

- 探索RISC-V架构测试:一个开源的硬件验证工具链

钟洁祺

探索RISC-V架构测试:一个开源的硬件验证工具链riscv-arch-test项目地址:https://gitcode.com/gh_mirrors/ri/riscv-arch-test在软件开发领域,我们常说“测试是质量的保证”。而在硬件设计中,这一原则同样适用。项目就是一个致力于RISC-V架构验证的开源工具链,它可以帮助开发者确保其RISC-V处理器实现正确地遵循了指令集体系结构(ISA)

- 重磅!RISC-V+OpenHarmony平板电脑发布

问界前讯

业界资讯

仟江水商业电讯(8月18日北京委托发布)RISC-V作为历史上全球发展速度最快、创新最为活跃的开放指令架构,正在不断拓展高性能计算领域的边界。OpenHarmony是由开放原子开源基金会孵化并运营的开源项目,已成为发展速度最快的智能终端开源操作系统,成为下一代智能终端操作系统根社区。开放RISC-V指令架构结合开源OpenHarmony操作系统,实现了移动终端设备从硬件到软件的全栈开源开放创新。经

- riscv简单常用汇编指令xv6

耶耶耶耶耶~

操作系统操作系统

文章目录前言entry.Smretasmvolatilereadcsrwritecsrriscv常见csr寄存器ecall,系统调用指令cpu执行异常处理指令的三种事件异常处理相关寄存器用户态trapsret指令页表切换操作用户态系统调用过程总结内核态trap缺页异常中断与设备驱动Locking调度文件系统操作系统拥有的资源xv6系统启动过程1.准备C代码执行环境2.进入mainchar*argv

- 基于 RISC-V SoC 的 1024 点 FFT 设计(10-02-05)1024 点 FFT 的 RISC-V SoC 整体架构

新芯设计

第十篇章基于RVSoC的1024点FFT设计ICFPGASoCVerilog芯片设计硬件开发RISC-V

芯片原厂必学课程-第十篇章-基于RISC-VSoC的1024点FFT设计10-02-051024点FFT的RISC-VSoC整体架构新芯设计:专注,积累,探索,挑战文章目录芯片原厂必学课程-第十篇章-基于RISC-VSoC的1024点FFT设计10-02-051024点FFT的RISC-VSoC整体架构引言一、FFT系统的架构设计二、FFT系统的总线设计三、FFT系统的资源分析与功耗分析引言 本

- 使用 C++23 从零实现 RISC-V 模拟器(5):CSR

everystep_

c++23risc-v

文章汇总「从零实现模拟器、操作系统、数据库、编译器…」:https://okaitserrj.feishu.cn/docx/R4tCdkEbsoFGnuxbho4cgW2YntcRISC-V为每个hart定义了一个独立的控制状态寄存器(CSR)地址空间,提供了4096个独立的寄存器位置。每个hart都可以通过这个独立的CSR地址空间来配置、管理和监控其执行环境,实现对其控制状态的细粒度操作。接下来

- 基于Qt的RTL可视模拟器(VSRTL)配置

吹角连营G

qtubuntu系统架构

文章目录VSRTL介绍Qt5.15.2安装构建VSRTLVSRTL介绍寄存器传输逻辑的可视模拟器(VisualSimulationofRegisterTransferLogic,VSRTL)是一个可以描述、可视化和仿真数字电路的框架。VSRTL描述的电路可以作为独立的应用,也可以嵌入到基于Qt的C++应用中。基于RISC-V指令集的模拟器Ripes即使用VSRTL开发。VSRTL依赖于C++17工

- RISC-V 在区块链智能及云原生中的应用、机遇与挑战

NervosNetwork

开发区块链rust虚拟机risc-v

本文转载自:斗篷客(ID:wearecloakman)区块链如同2000年前后的互联网,正一步步走入我们每个人的生活中。作为区块链整套技术中的核心之一,智能合约/虚拟机的设计在推动区块链创新的进程中,正扮演着越来越重要的角色。由此出发,虚拟机的设计也呈现着百花齐放的姿态。秘猿科技根据对智能合约层以及区块链虚拟机的理解与反思,基于RISC-V硬件指令集打造了虚拟机CKB-VM。在这次分享中,我们将会

- 使用 C++23 从零实现 RISC-V 模拟器(6):权限支持

everystep_

c++23risc-v

本节内容增加了权限表示,设置了三种权限。当cpu初始化时默认的权限为Machine模式。接下来实现这三种特权模式,随后实现sret和mret指令。RISC-V定义了三种特权等级,分别是用户态(UserMode)、监管态(SupervisorMode)、和机器态(MachineMode)。这三种特权等级对应着不同的操作系统和应用场景,提供了不同级别的访问权限。1.权限表示定义下面三个参数来表示不同的

- 关于RISC-V与Arm的对比分析和各自的应用

jacksong2021

原文:http://m.elecfans.com/article/1010395.html近日,开源指令集RISC-V得到了越来越多的重视。RISC-V是加州大学伯克利分校的开源指令集,由计算机体系架构的宗师级人物DavidPatterson领衔打造,通过将核心指令集以及其他关键IP开源,意图大大改变半导体的设计生态。随着西部数据、Nvidia等业界巨头以及大量初创公司宣布开始使用RISC-V,A

- RISC-V与ARM

吮指原味张

#其他指令集

参考资料:第五代精简指令集计算机RISC-V你了解多少?ARM与RISC-V架构的区别ARM与RISC-V的恩爱情仇1.ARM1991年ARM公司成立于英国剑桥,早期ARM也自主设计和生产芯片,但由于业绩平平,最后ARM改变了策略,他们不再生产芯片,转而以授权的方式,将芯片设计方案转让给其他公司。ARM有三种授权方式:处理器、POP以及架构授权。ARM架构是一种采用独特的ARM指令集系统、并且根据

- RISC-V和ARM

小米人er

我的博客risc-varm开发

参考:https://www.eet-china.com/mp/a39867.htmlRISC-V和ARM都是基于**精简指令集计算(RISC)**原理建立的指令集架构。他们的主要区别在于他们的授权模式和开放性:ARM是一种专有的指令集架构,众多使用ARM架构的厂商,只能根据自身需求,调整产品频率和功耗,不得改变原有设计。ARM架构和RISC-V架构都源自1980年代的精简指令计算机RISC,两者

- 为什么RISC-V的指令结构如此的奇怪

Megahertz66

RISC-Vrisc-v

为什么RISC-V的指令结构如此的奇怪RISC-V有六种不同的指令集,如下图分别为R-type/I-type/S-type/B-type/U-type/J-type但是为什么像B-type的指令不将立即数的顺序排成类似于imm[12:1]而是要搞成像上图中分开的样子呢?刚开始学习RISC-V的时候也是不求甚解的看了一下,直到我无意中看到了一个stackoverflow上面的提问。有兴趣大家可以去看

- RISC-V MCU开发教程之低功耗蓝牙MCU看门狗使用

借过风景

risc-vmcu单片机

的卢CH582M,其采用沁恒自研RISC-V微处理器“青稞V4”,片上集成2Mbps低功耗蓝牙,兼容Bluetooth®lowenergy5.3,另外配备SPI、I²C、RTC等丰富外设。的卢CH573、的卢CH582的看门狗计数器是8位的(计数最大255),计数周期131072/Fsys以卢CH573、的卢CH582为例,evt中主频都是60M,看门狗最大时间(131072/60000000)*

- [嵌入式系统-29]:开源的虚拟机监视器和仿真器:Windows环境下安装QEMU(Quick EMUlator)

文火冰糖的硅基工坊

嵌入式系统嵌入式架构操作系统

目录步骤1:windowsqemu的安装包下载步骤2:安装1.选择语言默认英文2.安装开始,选择Next3.安装选项,这里可以通过打开Systememulation中的下落项选择需要模拟的系统x86_64,arm,riscv64,riscv32等系统都可以支持勾选,尽量安装默认,全部勾选即可4.设置安装路径,选择自己合适的路径即可5.安装中,耐心等待即可6.安装完成,点击Finish即可7.qem

- 多线程编程之join()方法

周凡杨

javaJOIN多线程编程线程

现实生活中,有些工作是需要团队中成员依次完成的,这就涉及到了一个顺序问题。现在有T1、T2、T3三个工人,如何保证T2在T1执行完后执行,T3在T2执行完后执行?问题分析:首先问题中有三个实体,T1、T2、T3, 因为是多线程编程,所以都要设计成线程类。关键是怎么保证线程能依次执行完呢?

Java实现过程如下:

public class T1 implements Runnabl

- java中switch的使用

bingyingao

javaenumbreakcontinue

java中的switch仅支持case条件仅支持int、enum两种类型。

用enum的时候,不能直接写下列形式。

switch (timeType) {

case ProdtransTimeTypeEnum.DAILY:

break;

default:

br

- hive having count 不能去重

daizj

hive去重having count计数

hive在使用having count()是,不支持去重计数

hive (default)> select imei from t_test_phonenum where ds=20150701 group by imei having count(distinct phone_num)>1 limit 10;

FAILED: SemanticExcep

- WebSphere对JSP的缓存

周凡杨

WAS JSP 缓存

对于线网上的工程,更新JSP到WebSphere后,有时会出现修改的jsp没有起作用,特别是改变了某jsp的样式后,在页面中没看到效果,这主要就是由于websphere中缓存的缘故,这就要清除WebSphere中jsp缓存。要清除WebSphere中JSP的缓存,就要找到WAS安装后的根目录。

现服务

- 设计模式总结

朱辉辉33

java设计模式

1.工厂模式

1.1 工厂方法模式 (由一个工厂类管理构造方法)

1.1.1普通工厂模式(一个工厂类中只有一个方法)

1.1.2多工厂模式(一个工厂类中有多个方法)

1.1.3静态工厂模式(将工厂类中的方法变成静态方法)

&n

- 实例:供应商管理报表需求调研报告

老A不折腾

finereport报表系统报表软件信息化选型

引言

随着企业集团的生产规模扩张,为支撑全球供应链管理,对于供应商的管理和采购过程的监控已经不局限于简单的交付以及价格的管理,目前采购及供应商管理各个环节的操作分别在不同的系统下进行,而各个数据源都独立存在,无法提供统一的数据支持;因此,为了实现对于数据分析以提供采购决策,建立报表体系成为必须。 业务目标

1、通过报表为采购决策提供数据分析与支撑

2、对供应商进行综合评估以及管理,合理管理和

- mysql

林鹤霄

转载源:http://blog.sina.com.cn/s/blog_4f925fc30100rx5l.html

mysql -uroot -p

ERROR 1045 (28000): Access denied for user 'root'@'localhost' (using password: YES)

[root@centos var]# service mysql

- Linux下多线程堆栈查看工具(pstree、ps、pstack)

aigo

linux

原文:http://blog.csdn.net/yfkiss/article/details/6729364

1. pstree

pstree以树结构显示进程$ pstree -p work | grep adsshd(22669)---bash(22670)---ad_preprocess(4551)-+-{ad_preprocess}(4552) &n

- html input与textarea 值改变事件

alxw4616

JavaScript

// 文本输入框(input) 文本域(textarea)值改变事件

// onpropertychange(IE) oninput(w3c)

$('input,textarea').on('propertychange input', function(event) {

console.log($(this).val())

});

- String类的基本用法

百合不是茶

String

字符串的用法;

// 根据字节数组创建字符串

byte[] by = { 'a', 'b', 'c', 'd' };

String newByteString = new String(by);

1,length() 获取字符串的长度

&nbs

- JDK1.5 Semaphore实例

bijian1013

javathreadjava多线程Semaphore

Semaphore类

一个计数信号量。从概念上讲,信号量维护了一个许可集合。如有必要,在许可可用前会阻塞每一个 acquire(),然后再获取该许可。每个 release() 添加一个许可,从而可能释放一个正在阻塞的获取者。但是,不使用实际的许可对象,Semaphore 只对可用许可的号码进行计数,并采取相应的行动。

S

- 使用GZip来压缩传输量

bijian1013

javaGZip

启动GZip压缩要用到一个开源的Filter:PJL Compressing Filter。这个Filter自1.5.0开始该工程开始构建于JDK5.0,因此在JDK1.4环境下只能使用1.4.6。

PJL Compressi

- 【Java范型三】Java范型详解之范型类型通配符

bit1129

java

定义如下一个简单的范型类,

package com.tom.lang.generics;

public class Generics<T> {

private T value;

public Generics(T value) {

this.value = value;

}

}

- 【Hadoop十二】HDFS常用命令

bit1129

hadoop

1. 修改日志文件查看器

hdfs oev -i edits_0000000000000000081-0000000000000000089 -o edits.xml

cat edits.xml

修改日志文件转储为xml格式的edits.xml文件,其中每条RECORD就是一个操作事务日志

2. fsimage查看HDFS中的块信息等

&nb

- 怎样区别nginx中rewrite时break和last

ronin47

在使用nginx配置rewrite中经常会遇到有的地方用last并不能工作,换成break就可以,其中的原理是对于根目录的理解有所区别,按我的测试结果大致是这样的。

location /

{

proxy_pass http://test;

- java-21.中兴面试题 输入两个整数 n 和 m ,从数列 1 , 2 , 3.......n 中随意取几个数 , 使其和等于 m

bylijinnan

java

import java.util.ArrayList;

import java.util.List;

import java.util.Stack;

public class CombinationToSum {

/*

第21 题

2010 年中兴面试题

编程求解:

输入两个整数 n 和 m ,从数列 1 , 2 , 3.......n 中随意取几个数 ,

使其和等

- eclipse svn 帐号密码修改问题

开窍的石头

eclipseSVNsvn帐号密码修改

问题描述:

Eclipse的SVN插件Subclipse做得很好,在svn操作方面提供了很强大丰富的功能。但到目前为止,该插件对svn用户的概念极为淡薄,不但不能方便地切换用户,而且一旦用户的帐号、密码保存之后,就无法再变更了。

解决思路:

删除subclipse记录的帐号、密码信息,重新输入

- [电子商务]传统商务活动与互联网的结合

comsci

电子商务

某一个传统名牌产品,过去销售的地点就在某些特定的地区和阶层,现在进入互联网之后,用户的数量群突然扩大了无数倍,但是,这种产品潜在的劣势也被放大了无数倍,这种销售利润与经营风险同步放大的效应,在最近几年将会频繁出现。。。。

如何避免销售量和利润率增加的

- java 解析 properties-使用 Properties-可以指定配置文件路径

cuityang

javaproperties

#mq

xdr.mq.url=tcp://192.168.100.15:61618;

import java.io.IOException;

import java.util.Properties;

public class Test {

String conf = "log4j.properties";

private static final

- Java核心问题集锦

darrenzhu

java基础核心难点

注意,这里的参考文章基本来自Effective Java和jdk源码

1)ConcurrentModificationException

当你用for each遍历一个list时,如果你在循环主体代码中修改list中的元素,将会得到这个Exception,解决的办法是:

1)用listIterator, 它支持在遍历的过程中修改元素,

2)不用listIterator, new一个

- 1分钟学会Markdown语法

dcj3sjt126com

markdown

markdown 简明语法 基本符号

*,-,+ 3个符号效果都一样,这3个符号被称为 Markdown符号

空白行表示另起一个段落

`是表示inline代码,tab是用来标记 代码段,分别对应html的code,pre标签

换行

单一段落( <p>) 用一个空白行

连续两个空格 会变成一个 <br>

连续3个符号,然后是空行

- Gson使用二(GsonBuilder)

eksliang

jsongsonGsonBuilder

转载请出自出处:http://eksliang.iteye.com/blog/2175473 一.概述

GsonBuilder用来定制java跟json之间的转换格式

二.基本使用

实体测试类:

温馨提示:默认情况下@Expose注解是不起作用的,除非你用GsonBuilder创建Gson的时候调用了GsonBuilder.excludeField

- 报ClassNotFoundException: Didn't find class "...Activity" on path: DexPathList

gundumw100

android

有一个工程,本来运行是正常的,我想把它移植到另一台PC上,结果报:

java.lang.RuntimeException: Unable to instantiate activity ComponentInfo{com.mobovip.bgr/com.mobovip.bgr.MainActivity}: java.lang.ClassNotFoundException: Didn't f

- JavaWeb之JSP指令

ihuning

javaweb

要点

JSP指令简介

page指令

include指令

JSP指令简介

JSP指令(directive)是为JSP引擎而设计的,它们并不直接产生任何可见输出,而只是告诉引擎如何处理JSP页面中的其余部分。

JSP指令的基本语法格式:

<%@ 指令 属性名="

- mac上编译FFmpeg跑ios

啸笑天

ffmpeg

1、下载文件:https://github.com/libav/gas-preprocessor, 复制gas-preprocessor.pl到/usr/local/bin/下, 修改文件权限:chmod 777 /usr/local/bin/gas-preprocessor.pl

2、安装yasm-1.2.0

curl http://www.tortall.net/projects/yasm

- sql mysql oracle中字符串连接

macroli

oraclesqlmysqlSQL Server

有的时候,我们有需要将由不同栏位获得的资料串连在一起。每一种资料库都有提供方法来达到这个目的:

MySQL: CONCAT()

Oracle: CONCAT(), ||

SQL Server: +

CONCAT() 的语法如下:

Mysql 中 CONCAT(字串1, 字串2, 字串3, ...): 将字串1、字串2、字串3,等字串连在一起。

请注意,Oracle的CON

- Git fatal: unab SSL certificate problem: unable to get local issuer ce rtificate

qiaolevip

学习永无止境每天进步一点点git纵观千象

// 报错如下:

$ git pull origin master

fatal: unable to access 'https://git.xxx.com/': SSL certificate problem: unable to get local issuer ce

rtificate

// 原因:

由于git最新版默认使用ssl安全验证,但是我们是使用的git未设

- windows命令行设置wifi

surfingll

windowswifi笔记本wifi

还没有讨厌无线wifi的无尽广告么,还在耐心等待它慢慢启动么

教你命令行设置 笔记本电脑wifi:

1、开启wifi命令

netsh wlan set hostednetwork mode=allow ssid=surf8 key=bb123456

netsh wlan start hostednetwork

pause

其中pause是等待输入,可以去掉

2、

- Linux(Ubuntu)下安装sysv-rc-conf

wmlJava

linuxubuntusysv-rc-conf

安装:sudo apt-get install sysv-rc-conf 使用:sudo sysv-rc-conf

操作界面十分简洁,你可以用鼠标点击,也可以用键盘方向键定位,用空格键选择,用Ctrl+N翻下一页,用Ctrl+P翻上一页,用Q退出。

背景知识

sysv-rc-conf是一个强大的服务管理程序,群众的意见是sysv-rc-conf比chkconf

- svn切换环境,重发布应用多了javaee标签前缀

zengshaotao

javaee

更换了开发环境,从杭州,改变到了上海。svn的地址肯定要切换的,切换之前需要将原svn自带的.svn文件信息删除,可手动删除,也可通过废弃原来的svn位置提示删除.svn时删除。

然后就是按照最新的svn地址和规范建立相关的目录信息,再将原来的纯代码信息上传到新的环境。然后再重新检出,这样每次修改后就可以看到哪些文件被修改过,这对于增量发布的规范特别有用。

检出

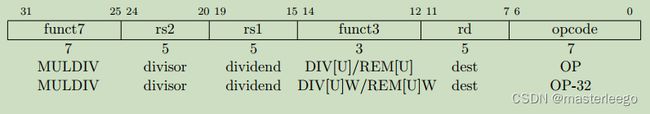

![表格9.1 零除和除法溢出的语义。L是操作的宽度,以位为单位:对于DIV[U]和REM[U]为XLEN,对于DIV[U]W和REM[U]W为32。](http://img.e-com-net.com/image/info8/bbe78e8d09784ca794ac53abe638a568.jpg)