浅谈AXI总线

这篇博客在写之前借鉴了网上各位大佬对AXI总线的理解和总结,在此表示感谢。集合了博客,知乎以及书上对AXI总线的介绍。做以下记录用于自己日后复习和更好的理解。

1:协议简介

Xilinx fpga 从Virtex-6系列开始,内部IP都支持AXI4总线协议,AXI高级可扩展接口(Advanced eXtensible Interface, AXI)是一种总线协议,该协议是ARM公司提出的高级微控制器总线结构 AMBA(Advanced Microcontroller Bus Archtiecture )协议中最重要的部分,AMBA总线标准一共有四套版本,各个版本的协议都沿用至今。AXI4总线协议包含在2010年发布的AMBA4.0中,包括AXI4,AXI4-Lite和AXI4-Stream。

它们的区别是:AXI4-Lite是AXI4的精简版,不支持突发传输方式(Burst-length固定=1),且总线接口只支持32bit 和 64bit位宽。

AXI4-Stream总线主要用于突发传输,而且对突发长度没有限制,支持一直读或写,没有地址通道,没有读写使能,只用TLAST信号拉高表示传输结束。

AXI4总线协议包括了主设备(Master)与互连结构之间,从设备(Slave)与互连结构之间,以及主设备与从设备之间的连接,AXI4总线是一种多通道并且以突发传输(连续传输)为机制的总线。可以连续对一片地址进行一次性读写,允许最大256轮的数据突发传输。

2:AXI有多少传输通道

AXI4总线拥有5个独立的传输通道:

(1)WRITE : 写地址通道,写数据通道,写响应通道。

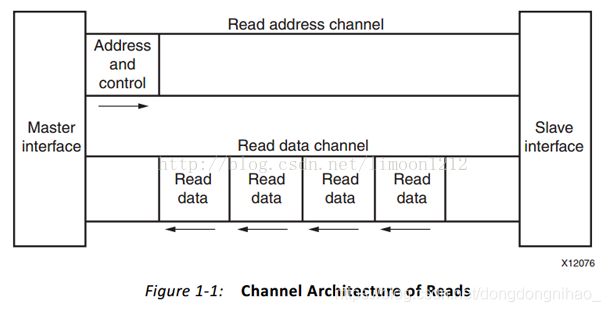

(2)READ:读地址通道,读数据通道(包含了读响应通道的功能)

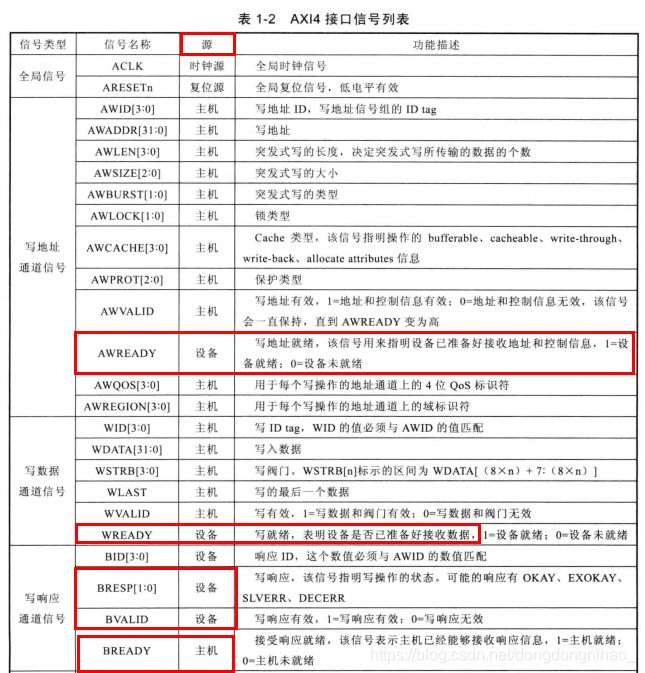

3:AXI4接口信号列表

WRITE:

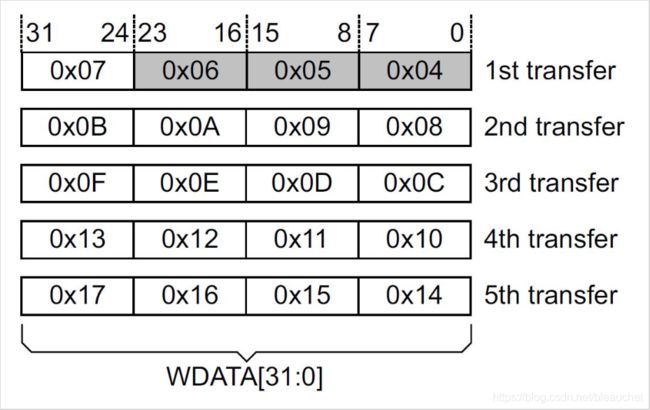

READ:

数据选通(WSTRB)信号说明:

WSTRB的每一位对应数据中的8位(1字节),用于标志数据中的对应字节是否有效。即当WSTRB[n] = 1时,标志数据中WDATA[(8n)+7: (8n)]部分有效。默认为11,表示均有效。

读/写突发类型(Aw/rBurst)信号说明:

AXI支持三种突发类型:

- FIXED(AxBURST[1:0]=0b00):固定突发模式,每次突发传输的地址相同

- INCR(AxBURST[1:0]=0b01):增量突发模式,突发传输地址递增,递增量与突发尺寸相关

- WRAP(AxBURST[1:0]=0b10):回卷突发模式,突发传输地址可溢出性递增,突发长度仅支持2,4,8,16。地址空间被划分为长度【突发尺寸*突发长度】的块,传输地址不会超出起始地址所在的块,一旦递增超出,则回到该块的起始地址

(借鉴了博客:https://blog.csdn.net/bleauchat/article/details/96891619)

这里顺便说明一下突发(Burst)的意思:

Burst length: ARLEN[7:0]和AWLEN[7:0]表示的就是这个。表示的是连续传输的周期数。一个burst内部是不可以被打断的。。所以data valid一旦高起来就要把一个burst传完再拉低,slave的ready信号可以中断,但是最终还是要高起来传完一个burst. 对于master来说,一旦开始传数,一个burst之间的valid应该是不会低的。

Burst size: 指的是一个burst里面有多少Byte. ARSIZE[2:0]和AWSIZE[2:0] 里就是这个。为什么只有3bit呢?因为只有8种情况。1,2,4,8,16,32,64,128。这个里面其实有个非常小的问题。。一般来说。总线位宽和burst size一致的。

但是也会出现不一致的情况:比如总线64bit, burst size是8Byte. 但是你要说我头铁非要给个不一样的值。。那也没问题。你总线是8BTYE, 你给了个2BYTE的Burst size, 那你就要指定,,每次传输这个2BYTE要放到8BYTE的哪几个BTYE上去。

(借鉴了知乎:https://zhuanlan.zhihu.com/p/96804919)

于是出现了两种不同的传输方式:

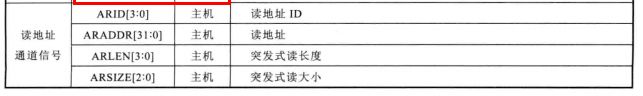

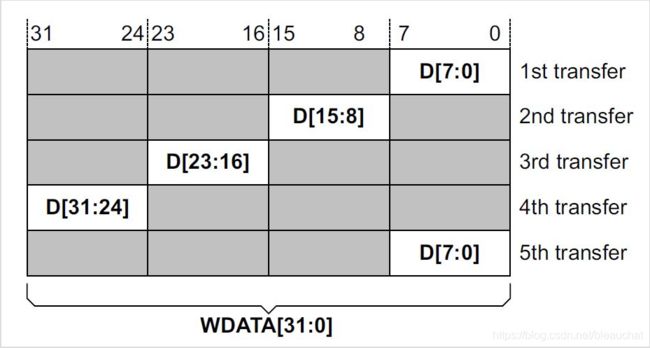

1:窄带传输

当传输的数据位宽小于xDATA总线带宽时,为窄带传输,每次使用的数据位数不同:

- FIXED模式突发下,使用同一段数据信号线

- INCREMENTING和WRAP地址的突发下,使用不同段信号线

比如上面这个例子。32bit的地址总线。burst size给了个8bit. 那就靠WSTRB这个信号确定往哪儿写。比如上面。传输了5次。在第五次传输时回到开头使用0~7位

2:不对齐传输(暂时还不理解)

当传输位宽超过1byte,起始地址不为数据总线硬件带宽(byte单位)整数倍时,为不对齐传输。不对齐传输的时候需要配合数据选通在第一次传输时将某几个byte置为无效,使第二次突发传输的起始地址(从机自动计算)为突发尺寸的整数倍。

4:AXI总线如何传输数据(写/读握手关系)

WRITE:

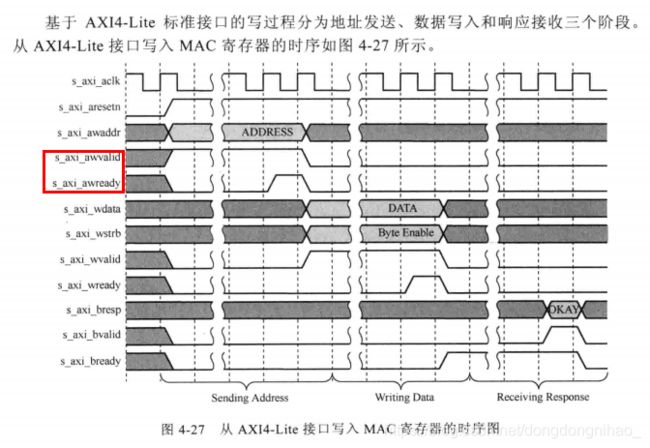

以AXI4-Lite标准协议为例,写过程分为三个阶段,地址发送,数据写入,响应接受三个阶段,时序如下图中所示。

一:地址发送阶段

在写数据过程中,主机的地址连接在s_axi_awaddr总线上,同时将s_axi_awvalid信号拉高,表示主机的有效地址信息已经在信道上等待从机完成接收。同时等待从机发出的接受响应,当从机发送的s_axi_awready有效(拉高)时表示从机允许接收地址信息。从接口只在s_axi_awvaild和s_axi_awready同时有效时才能完成地址信息的接收,即完成主接口的写地址发送。

二:数据写入阶段

主接口发送完地址信息后,准备写入数据,将待写入的数据置于s_axi_wdata总线上(s_axi_wstrb表示写入选通吸信号,默认为11,表示写入数据均可用),并将s_axi_wvalid置为有效(拉高),表示数据已经在信道上等待从机发出的写入响应信号,进而写入从接口。从接口将s_axi_wready信号拉高,表示从接口可以呗写入数据了。当s_axi_wavaild和s_axi_wready信号同时为1后,表示完成了数据写入

三:响应接收阶段

主接口完成数据写入后,主机把 s_axi_bready信号拉高(给从机一个我可以接收响应了 的信号),等待从机接口的响应信号。从接口的响应信号s_axi_bresp[1:0]用2‘b00表示数据信道的数据写入成功,即OKEY,从机接口发出的s_axi_bresp响应信号 的有效信号s_axi_bvaild为1时才表示响应有效。

主机的s_axi_bready=1,从机的s_axi_bresp[1:0]=2‘b00,s_axi_bvaild=1,同时满足表示主机接口确认从接口完成了数据的写入。

以上过程的结束表示一次完整的基于AXI4_Lite接口的写寄存器过程。

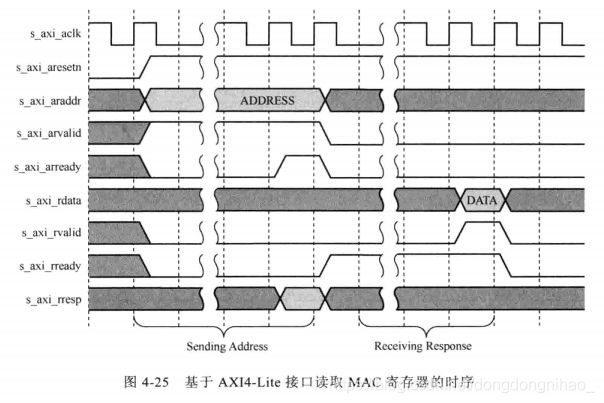

READ:

一:地址发送:

主机将要读入的地址输入到s_axi_araddr总线上,同时将s_axi_arvalid信号拉高。表示主机的地址已经在信道上等待从接口完成接收,同时等待从接口发出s_axi_arready信号,当从接口发出的s_axi_arready信号有效时,表示从接口允许接收地址信息。从接口只在s_axi_arvaild信号和s_axi_arready同时有效时才能完成信息接收,即完成主接口的读地址发送。

二:数据接收:

主机发送完地址请求后,发送接收数据请求信号,将s_axi_rready信号拉高,表示主机可以接收数据了。从接口接收到主接口的准备ready信号后给出响应,在s_axi_rdata总线上发送主机请求的数据,同时把s_axi_rvaild信号拉高,表示s_axi_rdata数据有效,主机根据s_axi_rvaild信号 有效 接收数据,完成数据的读过程。

以上即为AXI4-Lite的读写时序。

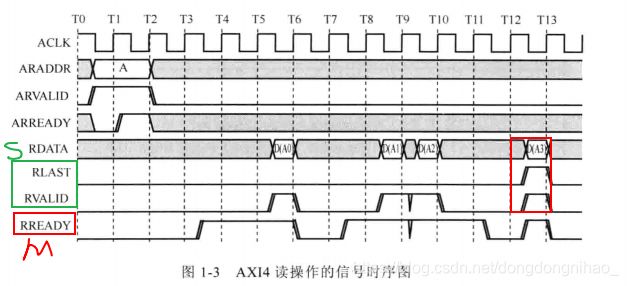

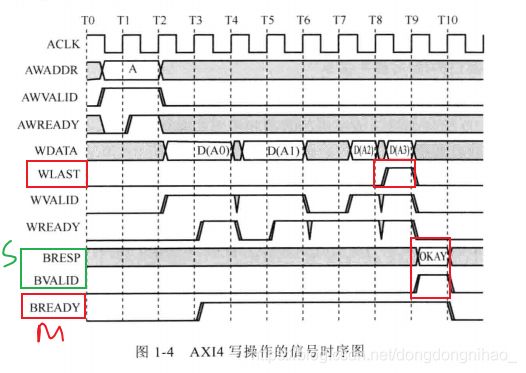

AXI-4的读写时序如下图中所示,基本时序与AXI4-Lite一样。区别在于AXI4-Lite只支持突发=1的操作。而AXI-4支持多burst的操作。最后一个数据写入或读出时拉高 W/RLAST信号。

完,如有错误请指正。