如何用VS code开发FPGA的程序,iverilog使用说明

目录

前言

一、VS code开发环境搭建

二、安装verilog和iverilog插件

三、准备FPGA程序测试代码

四、编译代码并查看波形

五、代码解读对比仿真波形

前言

之前一直用FPGA厂家自带的开发环境,但是针对一些体量不大,想要方便验证算法的时候,就想用一个简单的开发环境,网上找了找,发现很多工程师喜欢用VS code开发FPGA。用VSCode编辑verilog代码、iverilog编译、自动例化、自动补全、自动格式化等常用插件。

一、VS code开发环境搭建

首先需要搭建FPGA开发环境,网上论坛里的资料多来自于哔哩哔哩的视频,地址:RTL & FPGA开发中VSCode编辑器以及好用的几个插件_哔哩哔哩_bilibili 内容是:RTL & FPGA开发中VSCode编辑器以及好用的几个插件;

课程资料下载地址,里面有个《VScode编辑器的软件安装.pdf》,一步步操作即可。

链接:https://pan.baidu.com/s/1NZxgxncxkJa79LOYncfrKQ 提取码:4oxl

关于VS code开发环境的介绍,也 可以参考知乎的帖子:浮沉野马 - 知乎

二、安装verilog和iverilog插件

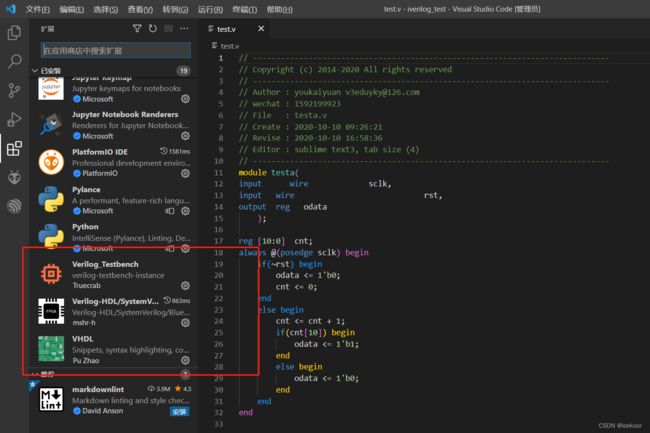

第一步:搜索下图的插件添加即可,iverilog附带gtkwave,插件的功能可以看介绍,下载完成后,还需进行以下配置,可以看知乎的帖子。

第二步:在扩展里搜索"verilog",找到下载人数最多的这个插件:Verilog-HDL/System,点一下“安装”按钮即可完成安装,此时我们发现代码有了颜色(如上图所示),但它并没有自动检错的功能。

第三步:将ctags添加到环境变量path,例如 新建 D:\ctags(根据你的实际情况),其他两个参照下图设定。

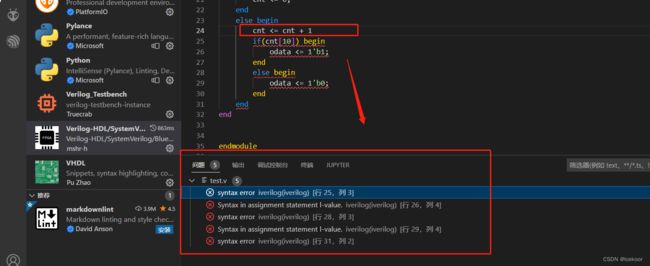

第四步:检测安装和配置是否成功,故意改错代码,需要保存后,是否会显示代码故障,测试结果如下图所示:

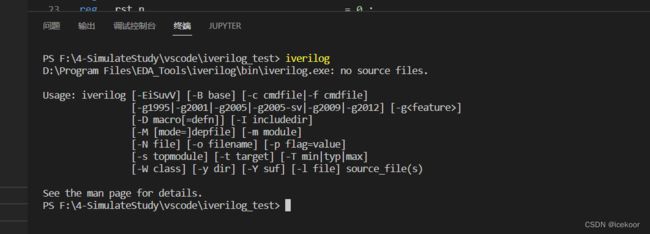

按下 Ctrl+~ 查看报错信息,如果iverilog没有起到作用,可以在终端中输入iverilog,再次启动iverilog功能。

三、准备FPGA程序测试代码

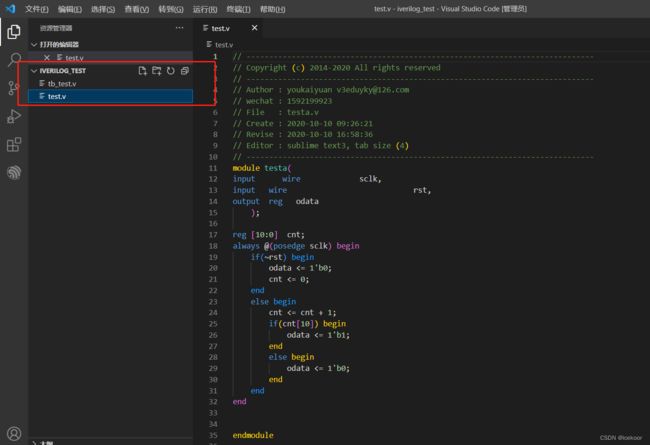

新建一个文件,添加FPGA代码,并在vscode中打开这个文件夹,写两个简单的verilog代码"test.v"和"tb_test.v",具体代码可以查看第四部分内容。

Testbech文件(顶层文件)添加必要代码:

需要在testbench仿真模块"tb_test"里添加下面的代码,不然不会生成.vcd文件,然后用gtkwave打开.vcd波形文件查看波形。

/* 生成vcd波形文件,用iverilog+GTKwave进行仿真所需的临时的vcd波形文件 */

initial begin

$dumpfile("./build/wavets.vcd"); // 指定VCD文件的名字为wavets.vcd,仿真信息将记录到此文件

$dumpvars(0, tb_testa ); // 指定层次数为0,则tb_testa模块及其下面各层次的所有信号将被记录

#100000 $finish;

end

上述代码解释如下:

本人希望把编译仿真生成的文件都放到"build"文件夹里,源代码都放到"src"文件夹里,所以我用的是"$dumpfile("./build/wavets.vcd");",但是很多插件只能支持网上的那种最简单的写法,不然找不到.vcd文件。

"#100000 $finish;" 经过100000ps(100us)后结束,也就是仿真时间;

注意:如果一直仿真停不下来,按ctrl+c可强制结束,终端无法返回时,输入finish就可结果仿真;

添加完的样子样式如图所示:

四、编译代码并查看波形

在终端里敲命令行代码,利用iverilog编译,生成.o文件。利用vvp命令可以生成.vcd文件,gtkwave可以直接打开.vcd文件查看波形。

下面是iverilog的终端控制方法,可以编译verilog文件,方便后续调试,建议大家好好学习。

输入:

第一个命令:md build

第二个命令:iverilog -o ./build/test.out tb_test.v test.v

第三个命令:vvp -n ./build/test.out

第四个命令:gtkwave ./build/wavets.vcd

下面显示解释上述命令:

第一个命令:"md build"创建build文件夹,用于存放编译仿真生成的文件,linux命令;

第二个命令:"."(点)的意思是当前位置,也就是这个位置,如果代码文件放置在src下面,则需要./src/或者说是.\src\ 源代码。

iverilog作用是编译文件,比如设计模块的代码和仿真模块的代码都在一个test.v文件里,那么编译这个文件只需要命令"iverilog test.v"

可是如果设计模块代码写在了test.v文件里,仿真模块的代码写在了tb_test.v文件里,那么只需要把所有的文件名字全都缀在后面即可"iverilog test.v tb_test.v"

iverilog的参数"-o

第三个命令:"vvp ./build/test.out"命令是生成.vcd波形文件,需要在testbench仿真模块(激励模块)添加几行代码,FPGA的仿真方法,这里就不多说了。如果用强大的仿真,推荐modelsim。

第四个命令:"gtkwave wave.vcd"意思就是用gtkwave.exe打开.vcd文件;

五、代码解读对比仿真波形

test.v和tb_test.v程序代码如下,比较简单,就是时钟sclk的计数,当cnt[10]为1时,置位odata;反之,复位odata。

module testa(

input wire sclk,

input wire rst,

output reg odata

);

reg [10:0] cnt;

always @(posedge sclk) begin

if(~rst) begin

odata <= 1'b0;

cnt <= 0;

end

else begin

cnt <= cnt + 1;

if(cnt[10]) begin

odata <= 1'b1;

end

else begin

odata <= 1'b0;

end

end

end// -----------------------------------------------------------------------------

`timescale 1ns / 1ps

module tb_testa;

// testa Parameters

parameter PERIOD = 10;

// testa Inputs

reg sclk = 0 ;

reg rst_n = 0 ;

// testa Outputs

wire odata;

initial

begin

$dumpfile("./build/wavets.vcd");

$dumpvars(0, tb_testa);

#100000 $finish;

end

initial

begin

forever #(PERIOD/2) sclk=~sclk;

end

initial

begin

#(PERIOD*2) rst_n = 1;

end

testa u_testa (

.sclk ( sclk ),

.rst ( rst_n ),

.odata ( odata )

);

endmodule仿真结果如下,GTKWave的软件就不多介绍了,喜欢用的可以自己研究,个人觉得比modsim的仿真差很多,用不习惯。