计算机系统基础知识笔记

计算机系统基础知识笔记

-

- 计算机硬件基本组成

- 中央处理单元(Central Processing Unit, CPU)

- CPU的组成

- 多核CPU

- 数据表示

- 浮点数表示

计算机硬件基本组成

计算机基本硬件五大基本部件:运算器、控制器、存储器、输入设备、输出设备

中央处理单元(CPU):由运算器、控制器等部件(寄存器、内部总线)集成

外设:输入设备和输出设备

存储器:内部存储器速度快、容量小、价格高、一般用来临时存放程序、数据以及中间结果,外部存储器速度慢、容量大、价格低,可以用来长期保存程序和数据

中央处理单元(Central Processing Unit, CPU)

中央处理单元(CPU)是计算机系统的核心部件,负责获取程序指令、对指令进行译码并加以执行。

CPU的功能:

1) 程序控制:CPU通过执行指令来控制程序的执行顺序

2) 操作控制:一条指令功能的实现需要若干操作信号配合完成,

CPU产生每条指令的操作信号并将操作信号送往相应的部件,控制相应的部件按照指令功能要求进行操作。

3) 时间控制:CPU对各种操作进行时间上的控制,即指令执行过程中操作信号出现的时间、

持续的时间以及出现的顺序都需要进行严格控制。

4) 数据处理:CPU通过对数据进行算术运算以及逻辑运算等方式进行加工处理。

数据加工处理的结果被人们所利用。

5) 对系统内部和外部的终端(异常)做出相应,并进行相应的处理。

CPU的组成

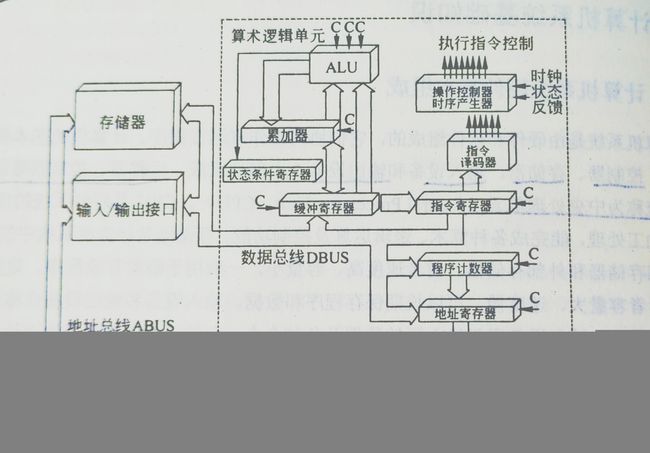

CPU主要由运算器、控制器、寄存器组和内部总线等部件组成。

(1)运算器:

由算术逻辑单元(Arithmetic and Logic Unit, ALU)、累加器(AC)、缓冲寄存器、状态条件寄存器(PSW)等组成,用于完成计算机的算数运算(加,减,乘,除等基本运算以及附加运算)和逻辑运算(与、或、非、零值测试等两值比较)。全部操作由控制器发出的控制信号指挥。

运算器的组成:

1) 算数逻辑单元(ALU):负责处理数据,实现算数运算和逻辑运算。

2) 累加寄存器(AC):是一个通用寄存器,功能是当运算器的算术逻辑单元执行算术或逻辑运算时,为ALU提供一个工作区。

例如在执行一个减法运算前,先将被减数取出暂存在AC中,再从内存储器中取出减数,然后同AC的内容相减,将所得到的结果送回到AC中。

运算结果是放在累加器中的,运算器至少要有一个累加寄存器。

3) 数据缓冲寄存器(DR):在对内存储器进行读/写操作时,用DR暂时存放由内存储器读/写的一条指令或一个数据字,将不同时间段内读/写的数据隔开来。

主要作用是作为CPU和内存、外部设备之间数据传输的中转站和缓冲。在但累加器结构的运算器中,数据缓冲器还可以兼做为操作数寄存器(相当于也是一个累加寄存器)。

4) 状态条件寄存器(PSW):保存由算术指令和逻辑指令运行或测试的结果建立的各种条件码,主要分为状态标志和控制标志。

如运算结果进位标志(C)、运算结果溢出标志(V)、运算结果为0标志(Z)、

运算结果为负标志(N)、中断标志(I)、方向标准(D)和单步标志等。

这些标志通常由1位触发器保存当前指令执行完之后的状态。通常一个算术操作产生一个运算结果,一个逻辑运算产生一个判决。

(2)控制器

控制器用于控制整个CPU的工作,他需要保证程序的正确执行,还要能够处理异常事件。一般分为指令控制、时序控制、总线控制逻辑和中断控制逻辑。

指令控制逻辑:

1) 取指令

2) 分析指令(指令译码)

3) 执行指令(按照指令操作数执行,形成下一条指令地址)

控制器的组成

1) 指令寄存器(IR):当CPU执行一条指令时,先把他从内存储器渠道缓冲寄存器再送入IR暂存。

指令译码器根据IR的内容产生各种微操作指令,控制其他的组成部件工作,完成所需的功能。

2) 程序计数器(PC):PC具有寄存信息和计数两种功能

顺序执行时:修改过程通常只是简单的对PC加1。

转移执行时:后续指令地址根据当前指令的地址加上一个(向前或向后)的位移量,

或者根据转移指令给出的直接转移地址。

3) 地址寄存器(AR):保存当前CPU访问的内存单元的地址,直到内存读/写操作完成(内存和CPU操作存在差异)

4) 指令译码器(ID):对指令(包括操作码和地址码两部分)中的操作码字段进行分析解释,

识别该指令规定的操作,向操作控制器发出具体的控制信号控制各部件工作。

控制逻辑

1) 时序控制逻辑:为每条指令按时间顺序提供应有的控制信号。

2) 总线控制逻辑:为多个功能部件服务的信息通路的控制电路。

3) 中断控制逻辑:控制各种中断请求,并根据优先级的高低对中断请求进行排队。

逐个交给CPU处理。

(3)寄存器组

1) 专用寄存器:运算器和控制器中的寄存器是专用寄存器,其作用是固定的

2) 通用寄存器:用途广泛并且可由程序员规定其用途

多核CPU

核心又称为内核,是CPU最重要的组成部分,CPU所有的计算、接收/存储命令、处理数据都由核心执行。

各种CPU的内核都具有固定的逻辑结构,一级缓存、二级缓存、执行单元和总线接口等逻辑单元都会有合理的布局。

多核即在一个单芯片上集成两个或多个处理器内核,每个内核都有自己的逻辑单元、控制单元、中断处理器、运算单元、共享或独有一级cache、二级cache,其部件完整性和单核处理器内核相比完全一致。

AMD的方案能够使得双核CPU的管脚、功耗等指标跟单核CPU保持一致,从单核升级到双核不需要更换电源、芯片组、散热系统和主板,只需要刷新BIOS软件即可。

多核CPU系统最大的优点(也是开发的最主要目的)是可满足用户同时进行多任务处理的要求。

数据表示

各种数值在计算机中表示的形式称为机器数,小数点隐含(整数隐含在末尾,小数隐含在起始位置)。机器数对应的实际数值称为数的真值。

源码:符号位+真值的绝对值

反码:正数=源码,负数=源码除符号位之外每位取反。

补码:正数=源码,负数=反码末位+1

移码:在数X上增加一个偏移量

浮点数表示

由于计算机采用2进制的局限性,事实上几乎所有的小数的精度都不能完全保证。

浮点数表示格式:

| 阶符 | 阶码 | 数符 | 尾数 |

|---|

浮点数能表示的数值范围由阶码决定,精度由尾数决定,通常采用规格化浮点数:将尾数限定在区间[0.5, 1]。由于尾数表示的是小数,所以其绝对值不会超过1,当尾数>=0时只需保证尾数大于0.5,当尾数<0时只需保证尾数<-0.5即可。

工业标准IEEE 754:

3种形式的IEEE 754浮点格式

| 参数 | 单精度浮点数 | 双精度浮点数 | 扩充精度浮点数 |

|---|---|---|---|

| 浮点数字长 | 32 | 64 | 80 |

| 尾数长度P | 23 | 52 | 64 |

| 指数长度 | 8 | 11 | 15 |

| 指数偏移量 | +127 | +1023 | +16382 |

(1)规格化值:阶码部分二进制不全为0或不全为1时表示的是规格化的数。对于尾数部分,由于约定小数点左边隐含一位,通常这位数就是1。

(2)非规格化值(用于表示数值0或非常接近0的值):当阶码部分二进制全为0时表示的是非规格化的。在这个情况下指数的真值为1-偏移量,尾数的值就是二进制形式对应的小数,不包含隐含的1。+0.0和-0.0在浮点表示时有所不同。

(3)特殊值:阶码部分二进制全为1表示特殊值。当尾数全部为0时表示无穷大,当符号位为0时表示正无穷,为1时表示负无穷。当浮点运算溢出时用无穷表示,当尾数部分不全为0时为"NaN",当运算结果不是实数或者无穷时表示NaN。

非规格化值和特殊值对比:

| 尾数不为0 | 尾数为+0 | 尾数为-0 | |

|---|---|---|---|

| 阶码全为0 | 接近0的数 | +0.0 | -0.0 |

| 阶码全为1 | NaN | 正无穷 | 负无穷 |