基于FPGA的数字频率计(设计全过程)

小序:

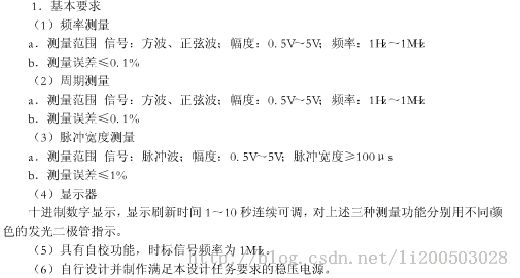

前几天看全国大学生电子设计竞赛历年试题,无意间发现了一道题目《简易数字频率计》,跟之前我用verilog写的一个频率计差不多,于是想尝试做一下,题目具体要求如下图中所示,我所用的开发板为 xilinx spartan 3ES, 最后结果还算理想,在要求的范围内的频率测量精度比较高,但是由于板子的限制没能实现脉冲宽度测量等功能,但是其原理比较简单,下文中将会给出设计过程,结果展示图片以及整个工程代码的下载链接。

数字频率计总体设计采用分块的思想,自底向上设计方向,三个子模块包括频率测量模块(fre_meter),二进制到十进制转换的模块(bin_dec)和数码管显示模块(led),最后用一个顶层模块(top)把三个子模块例化到一起。总体设计思路就是先通过测频模块测得的频率值然后通过进制转换模块将频率值转换为十进制数,最后再输入给显示模块显示出该频率值。

下图为模块示意图(实际工程中并没有采用原理图的输入方法,有种感觉ISE中原理图输入方法总会产生各种错误,这里仅作示意)。

下面分模块说明:

fre_meter: 测频模块,设计思路完全根据之前我写的一篇博文《verilog编写数字频率计》,只是稍作修改,这里不再重复

输入 clk:系统时钟信号 50Mhz rst_n:低电平异步复位 clk_in : 被测时钟频率。

输出 fre: 20bit位宽的频率值,可以满足题目中要求的 1Mhz的要求

bin_dec: 进制转换模块,二进制数转换为十进制 ,之前写的一篇博客《利用verilog将二进制码转换为十进制BCD码》其中只涉及到了8bit转换,本设计中待测最高频率1M,转换为二进制数为1111_0100_0010_0100_0000 ,之前的8bit转换思路没法搬到20bit转换中来用,所以寻找其他思路,后来在一个论坛中找到了16bit转换的代码,网址http://www.amobbs.com/thread-5500333-1-1.html ,经过修改后可以实现20bit二进制数到10进制的转换。

具体转换思路如下,位宽为20bit的二进制数最大为1111_1111_1111_1111_1111,转换为十进制为1048575,那么对于输入的二进制数hex,输出十进制数fre从百万位到各位分别为 Million , HunThousand , TenThousand , Thousand , Hundred , Ten , One。首先对比hex是否大于999999,如果是那么转换为十进制后的第七位Million为1,然后另d1=hex-1000000,如果hex不大于999999,那么 Million =0,d1=hex。 下面判断第六位HunThousand ,依次先后判断d1是否大于899999 、799999、699999......99999,假设d1>899999 ,那么 HunThousand=9,d2=d1-900000;如果d1>799999 ,那么 HunThousand=8,d2=d1-800000 ........依次类推逐一求得十进制数的每一位(具体设计见代码)。

输入 clk: 系统时钟信号50Mhz

rst:低电平异步复位

hex:20bit二进制频率值

输出 Million , HunThousand , TenThousand , Thousand , Hundred , Ten , One: 4bit位宽的频率值,代表十进制频率值的不同位

led: 数码管显示模块,数码管做动态显示利用人眼的对显示频率的敏感限度,八段数码管在一定频率下切换赋值,每一个时钟对一个数码管单独赋值并显示,切换频率大于一定值后,看起来像8位数码管同时显示(具体设计见代码)。

输入 clk: 系统时钟信号50Mhz

Million , HunThousand , TenThousand , Thousand , Hundred , Ten , One: 4bit位宽的频率值,代表十进制频率值的不同为位

输出 sel: 8bit 数码管位选信号

data:8bit数码管译码显示的值

测试结果:

下图为频率计的测试结果,上面一排为信号发生器输入的待测试脉冲的频率,下面一排为对应的频率计的测试结果,可以看出本设计的测量精度完全可以满足题目的要求,但是由于设备的限制,没能实现正弦波的测试,以及脉冲宽度的测试等等功能,但是我觉得原理基本和本设计中的测频模块相同。

本设计的ISE 工程下载地址http://download.csdn.net/detail/li200503028/7277701 ,积分不够用朋友可以给我发邮件308922492@qq.com。